*Serial Configuration Mode

串行配置模式分为:Master Serial 和 Slave Serial (如下图)两类; 两者的区别在与CCLK的输入输出方向;主动模式下为输出方向,从模式下为输入方向;

Slave Serial模式最典型应用于串行菊花链或者用外部控制器和CPLD配置单个FPGA。Master Serial模式中,CCLK作为输出;

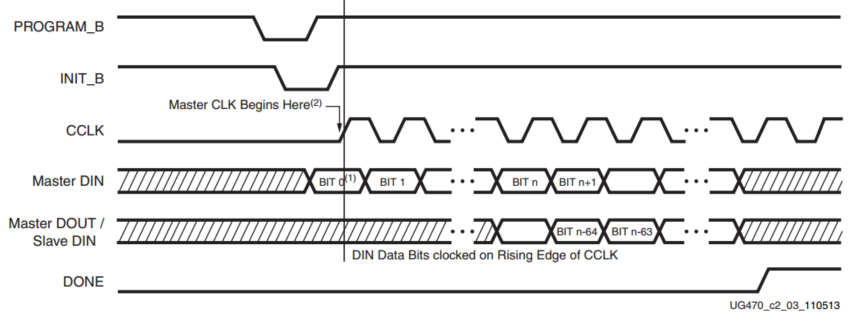

在Slave Serial 和 Master Serial 模式的时序图如下。Master DIN输入的第一个BIT0 代表第一个BYTE的最高位。

*SelectMAP configuration Mode

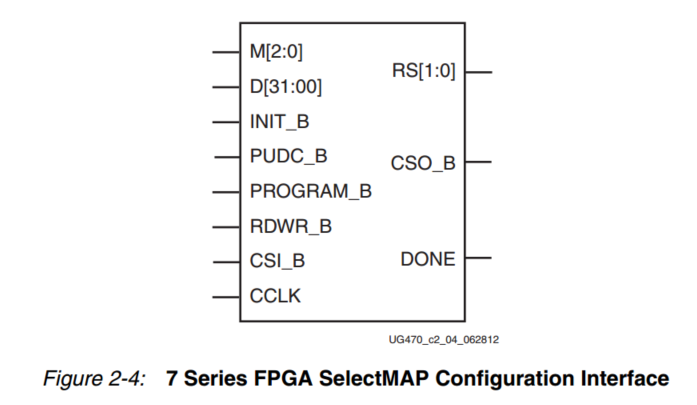

SelectMap配置接口提供了8/16/32bit位宽的双向数据总线到7系列FPGA的配置逻辑中,可以用来配置和回读。回读只能用与Slave SelectMap模式中。总线位宽是自动检测的。

SelectMap模式中支持多种配置方法:

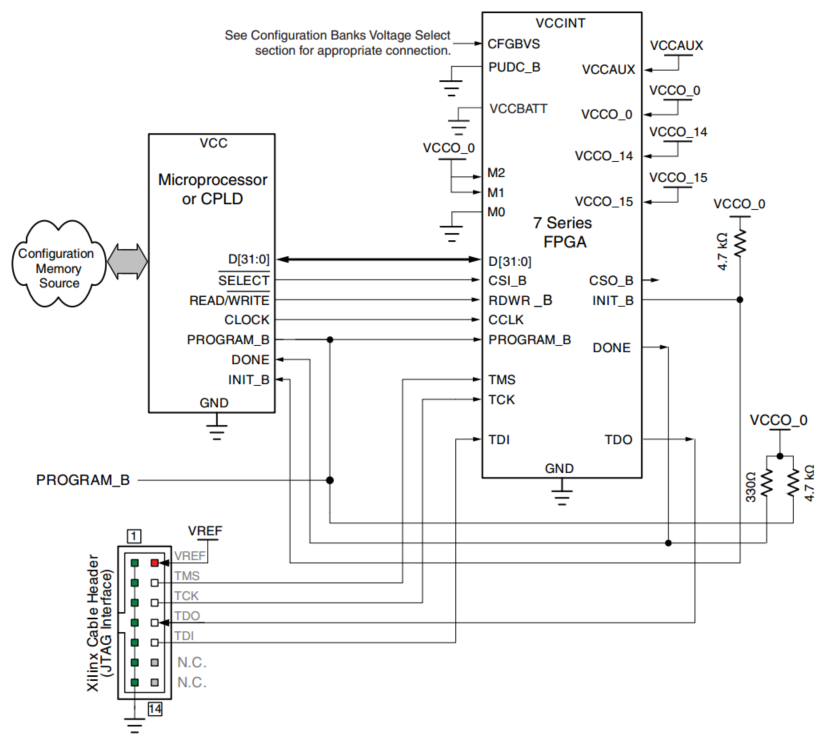

1.单器件Slave SelectMap:(如下图) 外部控制器/CPLD提供时钟和数据,通过Slave SelectMap接口配置FPGA。 Master SelectMap与Slave SelectMap相比,后者是首选模式。

2.多器件菊花链SelectMap总线:多个FPGA串行配置来自一个flash或者处理器的不同的镜像;

3.多器件协同SelectMap:多个FPGA并行配置来自一个flash或处理器的相同镜像。当使用平行flash时,建议使用BPI配置模式。

reference : UG626

reference: XAPP583

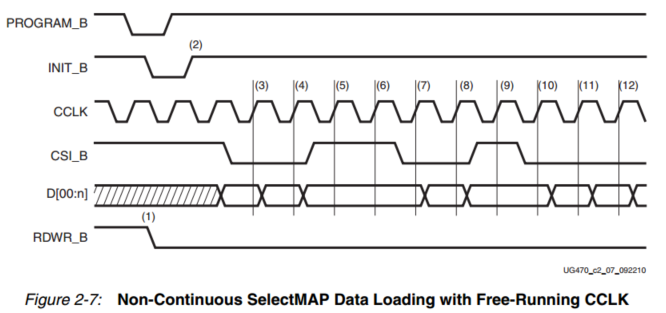

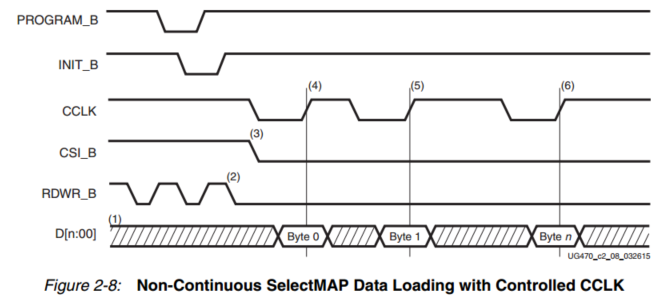

SelectMap支持连续数据写入(如下图)和非连续数据写入;非连续数据写入分为:CSI_B选择控制和CCLK中断控制。

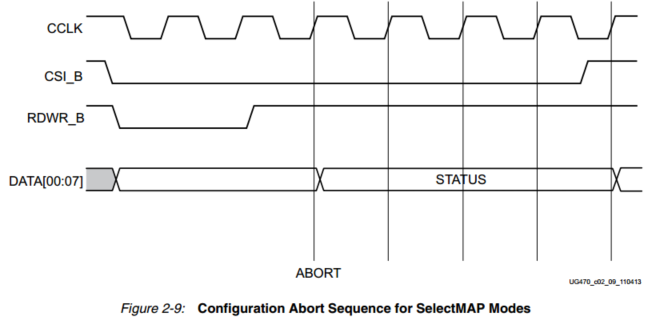

*SelectMAP ABORT

在SelectMAP配置和回读中,当CCLK采样下,RDWR_B改变同时CSI_B断言,将会出现中断。在一个配置中断中,通过四拍CCLK将内部状态输出到D[4:7]管脚上,其他D管脚保持拉高状态。在中断完成后,用户可以重新同步配置逻辑,继续配置。

配置中断序列:

1.配置顺序正常开始。

2.选择器件,将RDWR_B引脚拉高,同步到CCLK(CSI_B置为低电平)。

3.如果RDWR_B保持设置为读控制(逻辑高电平),FPGA会将状态字驱动到数据引脚上。

4. ABORT持续四个时钟周期,并更新状态。

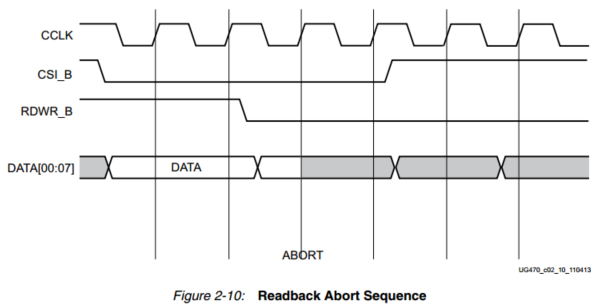

回读中断序列:

1.回读序列正常开始。

2.当器件被选中时,将RDWR_B引脚拉低至CCLK同步(CSI_B置为低电平)。

3.当CSI_B被置为无效时,ABORT结束。

注:回读期间的ABORT后面没有状态字,因为RDWR_B信号被设置为写控制(D 引脚是输入)。

中断状态字:

在配置中断下,器件驱动状态字到D[4:7]引脚;其他引脚保持为高。

在最后一个周期之后,可以重新加载同步字以建立数据对齐。

ABORT后有两种方法可以恢复配置或回读:

•ABORT完成后,设备可以重新同步。

•可以通过任意时间将PROGRAM_B置为低电平来复位器件。

要重新同步设备,必须取消置位CSI_B然后再重新置位。 通过发送ABORT发生时正在进行的最后一个配置或回读数据包,可以恢复配置或回读。 或者,可以从头重新开始配置或回读。

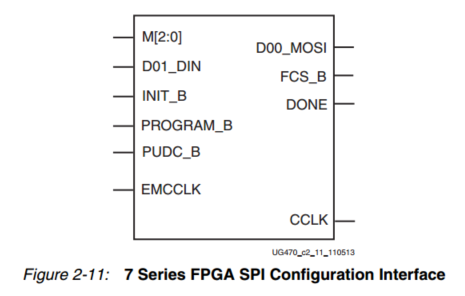

*Master SPI Configuration Mode

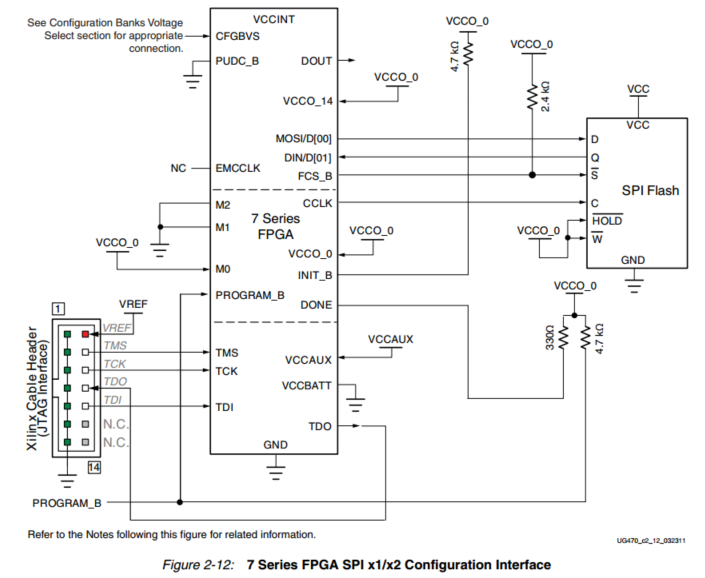

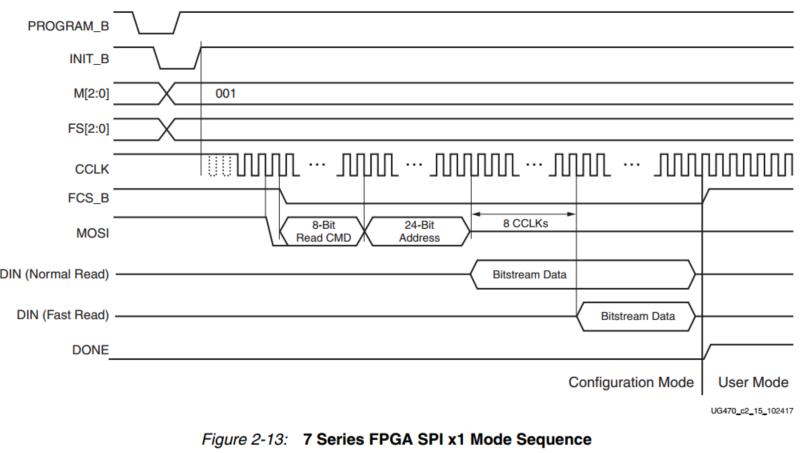

主SPI配置模式允许使用低引脚数,工业标准SPI闪存器件进行比特流存储。 FPGA支持直接连接SPI闪存器件的事实上标准的四引脚接口,用于读取存储的比特流。

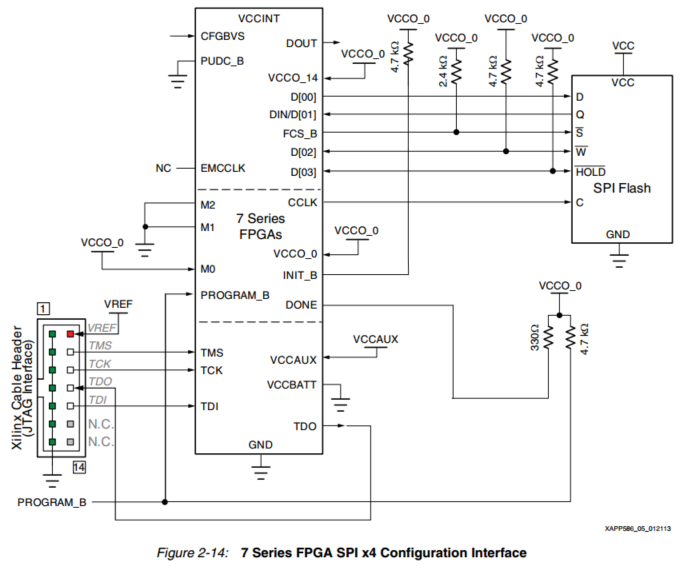

7系列FPGA主SPI配置模式 ,可以从支持x2和x4快速输出读操作的SPI器件读取, 这些输出模式比标准的1位SPI接口成比例地快。 此外,负边沿时钟模式可用于更好地利用整个时钟周期并允许更高的配置速度。 还支持超过128 Mb的SPI闪存密度,需要32位寻址。

SPI x1/x2 连接是相同的,因为x2模式使用D00_MOSI引脚作为双用途数据输入/输出引脚。

DOUT应连接到下游FPGA的DIN,以实现菊花链SPI x1配置模式。 x2或x4 SPI模式不支持菊花链。

对于从闪存到FPGA的数据路径,应考虑串联电阻,以最大限度地减少过冲。 可以通过仿真确定适当的电阻值。

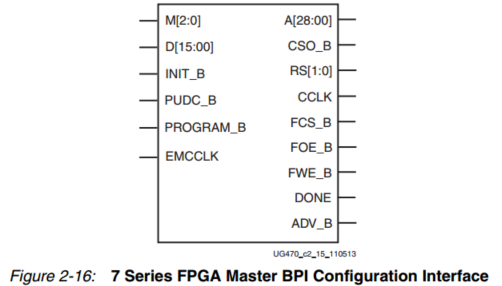

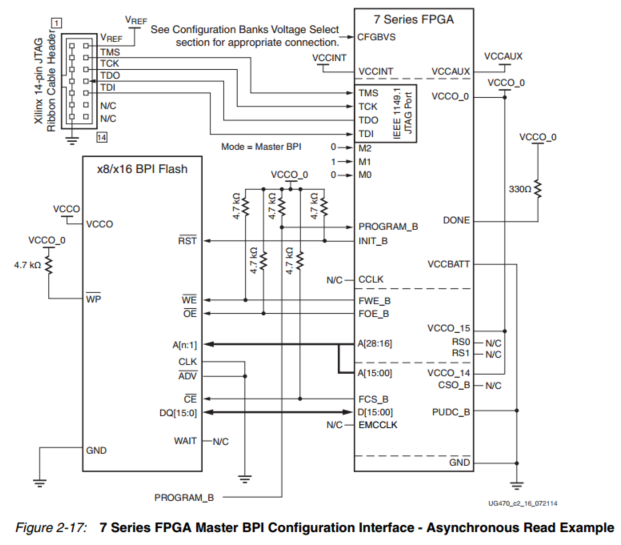

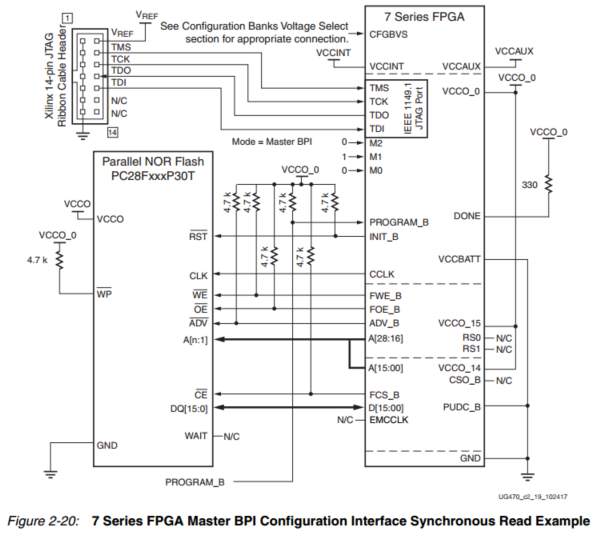

*Master BPI Configuration Interface

7系列FPGA主BPI配置模式 ,支持使用行业标准并行NOR(BPI)闪存器件进行比特流存储。 FPGA支持直接连接BPI闪存的地址,数据和控制信号,以提取存储的比特流。

主BPI配置模式有两种BPI闪存读取模式:异步和同步。 与其他直接配置模式相比,使用BPI flash同步读取模式可以实现更快的配置时间。 此外,多达29个地址线可以访问更宽密度范围的并行NOR闪存。

默认情况下,7系列FPGA使用BPI闪存的异步模式读取比特流数据 . FPGA从给定的起始地址驱动地址总线,BPI闪存发送回比特流数据。 默认起始地址为地址0.可以在MultiBoot重新配置过程中显式设置起始地址。 在异步读取模式下,支持总线宽度x8和x16 自动检测 。

在主BPI配置模式下,7系列FPGA默认使用BPI闪存异步读取模式来读取比特流数据。上电后,当FPGA的INIT_B输出变为高电平时,模式引脚M [2:0]被采样。此时必须将模式引脚定义为有效逻辑电平(主BPI配置模式M [2:0] = 010)。在整个FPGA配置中,PUDC_B引脚必须保持恒定的逻辑电平。

确定主BPI配置模式后,FPGA驱动闪存控制信号(FWE_B高,FOE_B低和FCS_B低)。尽管CCLK输出未连接到用于BPI闪存异步读取模式的BPI闪存器件,但FPGA在CCLK的上升沿之后输出地址,并且数据仍在CCLK的下一个上升沿采样。与BPI相关的时序参数使用CCLK引脚作为参考。在主BPI模式下,地址从0开始并递增1,直到DONE引脚置为有效。如果地址达到最大值(29'h1FFFFFFF)且未完成配置(DONE未置位),则状态寄存器中会出现错误标志,并开始进行回退重配置。 7系列FPGA BPI模式还支持异步页面模式读取,以允许增加CCLK频率。

1.INIT_B在FPGA内部初始化过程结束时释放。 外部电阻将INIT_B拉高。 在INIT_B的上升沿,FPGA对其M [2:0]引脚进行采样以确定配置模式。

2.在从M [2:0]引脚确定主BPI配置模式后,FPGA驱动FWE_B高电平,FOE_B低电平和FCS_B低电平。

3.对于主模式,FPGA在INIT_B的上升沿之后保持TICCK延迟再驱动CCLK。

4. FPGA通过其A [n:00]引脚驱动初始地址(A00),并保持初始地址至少10个CCLK周期。 对于上电配置,初始地址为0x00000000。 对于MultiBoot触发的配置,地址可以不同。

reference: XAPP587

*JTAG Interface

通过四引脚JTAG接口,可以使用Xilinx工具和Xilinx电缆直接从处理器或CPLD客户特定设计或使用第三方边界扫描工具配置7系列FPGA。 JTAG特定模式设置为(M [2:0] = 101)。 Xilinx工具使用JTAG接口,包括ISE Design Suite中的ISE和ChipScope™Pro工具,以及Vivado Design Suite工具。尽管JTAG命令优先于模式设置,但建议使用M [2:0]选项来启用JTAG模式和操作,而不会与其他配置模式发生冲突。