7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟、内部时钟进行处理,生成需要的低抖动时钟。PLL是MMCM的功能子集,也是基于MMCM的。其中MMCM包含的额外特性有:

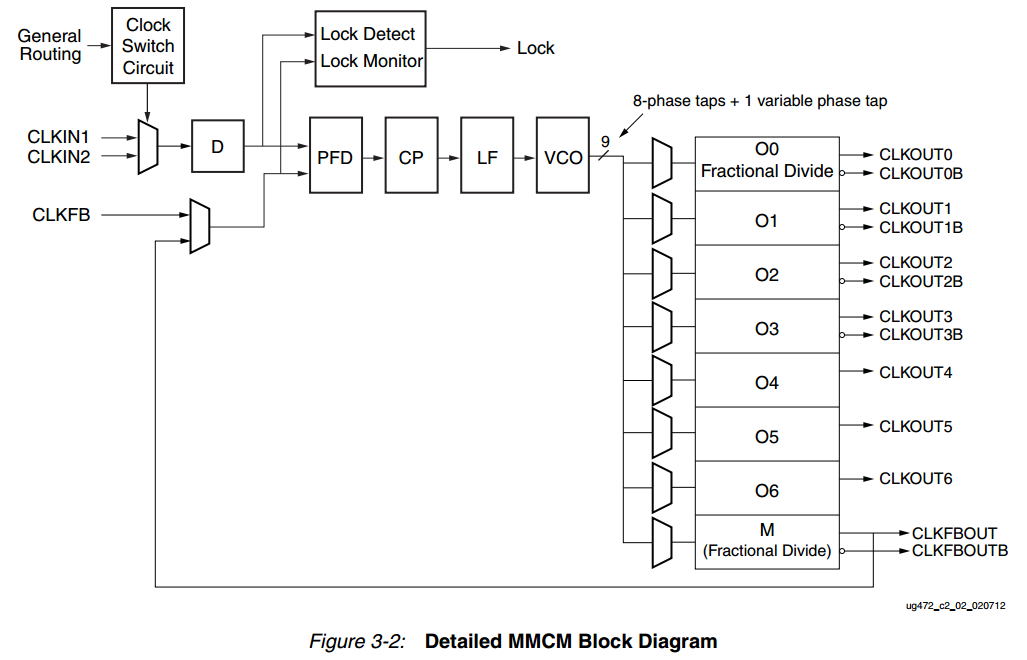

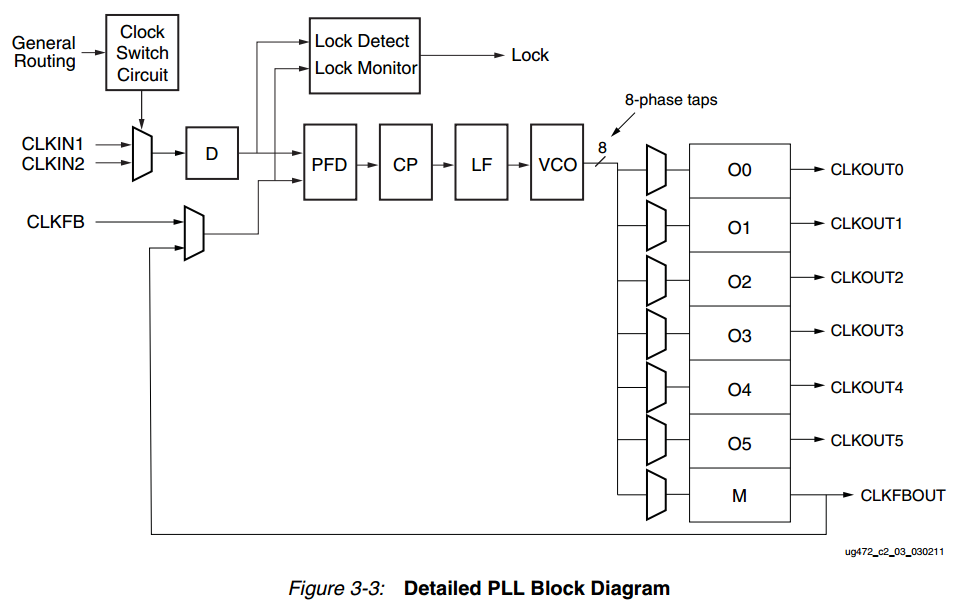

输入多路复用器从IBUFG,BUFG,BUFR,BUFH,GTs(CLKIN only)或互连(不推荐)中选择其一 作为参考和反馈时钟,每个时钟输入都经过一个可编程的计数器(D)。相位频率检测器(PFD)比较输入(参考)时钟和反馈时钟的上升边缘的相位和频率。如果最小的高/低脉冲是可保持的,则任务周期是辅助的。PFD用于生成与两个时钟之间的相位和频率成比例的信号。这个信号用于驱动增压泵(CP)和循环过滤器(LF)来为VCO生成一个参考电压。PFD会产生一个向上或向下的信号给充电泵和环形滤波器,以确定VCO是否应该以更高或更低的频率运行。当VCO以过高的频率运行时,PFD会激活一个向下的信号,导致控制电压降低,降低VCO的工作频率。当VCO以极低的频率运行时,向上的信号会增加电压。VCO生产八个输出阶段和一个可变阶段,用于精细阶段的转换。每个输出阶段都可以被选择作为输出计数器的参考时钟(图3-2和图3-3)。每个计数器可以独立地为给定的客户设计进行编程。还提供了一个特殊的计数器M。这个计数器控制MMCM和PLL的反馈时钟,允许合成宽范围的频率。除了整数除法输出计数器之外,MMCMs还为CLKOUT0和CLKBOUT0添加了一个分数计数器。

source: 可以选择单端输入、差分输入、全局buffer、no buffer四种;

Clock Management

Some of the key highlights of the clock management architecture include:

• High-speed buffers and routing for low-skew clock distribution

• Frequency synthesis and phase shifting

• Low-jitter clock generation and jitter filtering

Each 7 series FPGA has up to 24 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL).

参考:

UG472-7 Series FPGAs Clocking Resources.pdf

DS180-7 Series FPGAs Data Sheet: Overview.pdf