reference:https://blog.csdn.net/qq_40261818/article/details/83039829

PG046-Aurora 8B/10B Logicore IP Product Guide.pdf

GTP(吉比特收发器)简称Gigabit Transceiver with Low Power,经常应用于板级通信,板与板,应用在高速串行接口的数据收发。在A7系列芯片中我们叫GTP、在K7系列我们叫GTX、V系列叫GTH、对于不同速度等级的高速通信的物理接口。

首先就是要了解aurora IP帧模式,Aurora 协议是由Xilinx 公司提供的一个开放、免费的链路层协议,可以用来进行点到点的串行数据传输,具有实现高性能数据传输系统的高效率和简单易用的特点。Aurora 8b10协议是一个可扩展的、轻量级的链路层协议,可以用于单路或者多路串行数据通信。

1. AuroraIP帧模式

1.1 IP核配置

Lane width Byte=4Bytes 设置了用户AXI-Stream接口位宽是32bit

Lane Rate=5.0Gbps 设置了高速串行总线的数据速率

GT Refclk=125Mhz 设置了高速串行总线参考时钟频率,需要参考板卡实际连接的晶振频率

Init clk=50Mhz 用于初始化和产生复位的信号,请使用独立的时钟不要使用本IP核生成的用户时钟。

Drp clk=50Mhz 用于DRP配置的时钟,此时钟可以与Init clk 一致。

DataFlow Mode=Duplex 通信模式选择全双工,也可以选择单收或单发.

Interface =Frame 用户接口模式选择帧模式,帧模式帧内部含有起始字节和结束字节,选择性使能CRC ,用于数据校验,相对比流模式效率降低,但是能感知帧内是否出错。

Flow Control = UFC 流控信号选择User Flow Control,加入流控机制,流控信息可以更优先的传送,只有在Frame模式下可以选择。

Error Detection = CRC 使能CRC校验帧数据是否出错。

GT Selection -> Lanes = 1;

RefClk=GTPQ0 选择高速接口数量和参考时钟,这部分设置芯片有专用管脚对应,根据实际板卡和芯片型号选择。

Shared Logic = Include shared logic in core

共享逻辑资源不输出共享信号接口,只包含在IP核内部,在共享模式下一些时钟PLL资源可以给多个核使用。

INITCLK = Single ended init clk 初始化时钟选择单端时钟

未注明的设置选项保持默认即可

1.2 复位时序

上电后GT_Reset和Reset同时复位,GT_Reset提前128clk退出复位,当LaneUp&ChannelUp出现下降沿后 触发复位时序,Reset提前进入复位,128个时钟后GT_Reset进入复位状态,GT_Reset保持128时钟周期后,退出复位,之后再经过128时钟周期Reset退出复位,复位顺序完成。

1.3 用户流控信号 (ufc)

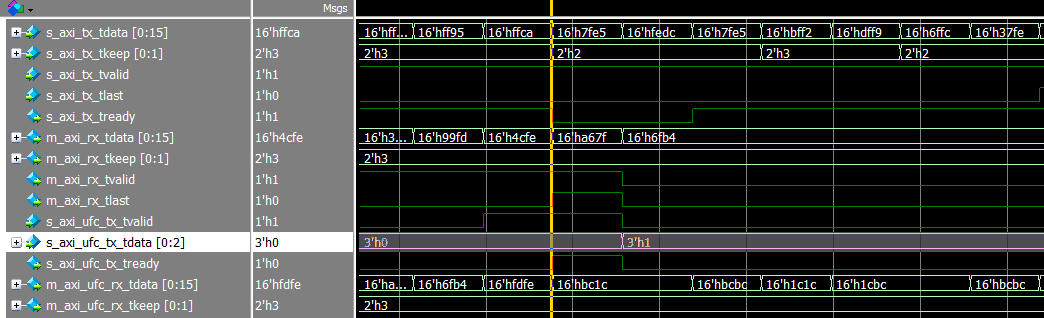

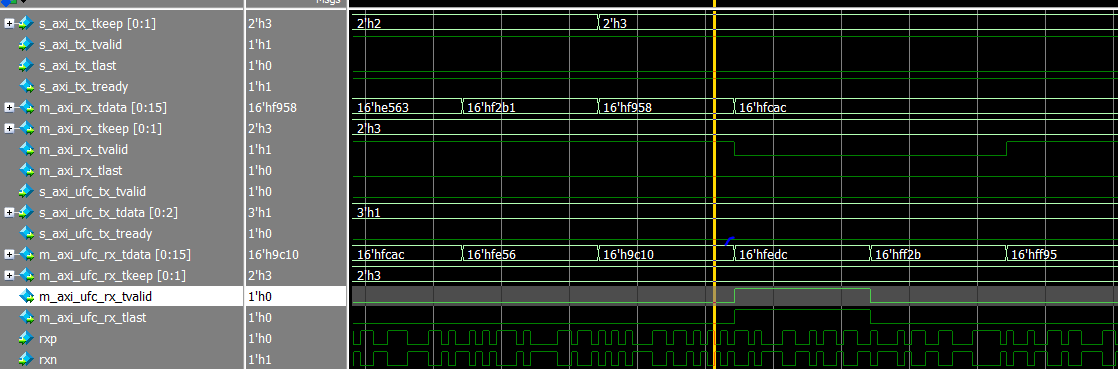

发送UFC数据,数据来自于S_axi_tx_tdata,发送到m_axi_ufc_rx_tdata; s_axi_ufc_tx_tdata指定UFC发送数据的大小(2~16byte); 如图,指定发送UFC大小2byte;

接收UFC数据,接收到2byte数据

1.3.1 用户流控信号时序

用户流控信号可以插入数据流中,从而在接收端可以降低缓冲buffer压力,一般应用场景,当接收端 buffer即将溢出时,给发送端发送指令,使得发送端插入流控数据降低接收端数据量防止溢出。

2. 帧模式结构框图

tx_ctrl和rx_ctrl模块是用户设计模块。tx_ctrl产生 测试数据源,通过Aurora IP发送到传输介质中,接收端接收数据并检测CRC检测结果,并对CRC错包计 数。在调试期间可以用xilinx调试IP的VIO功能监测错包数量。