- 新建工程文件

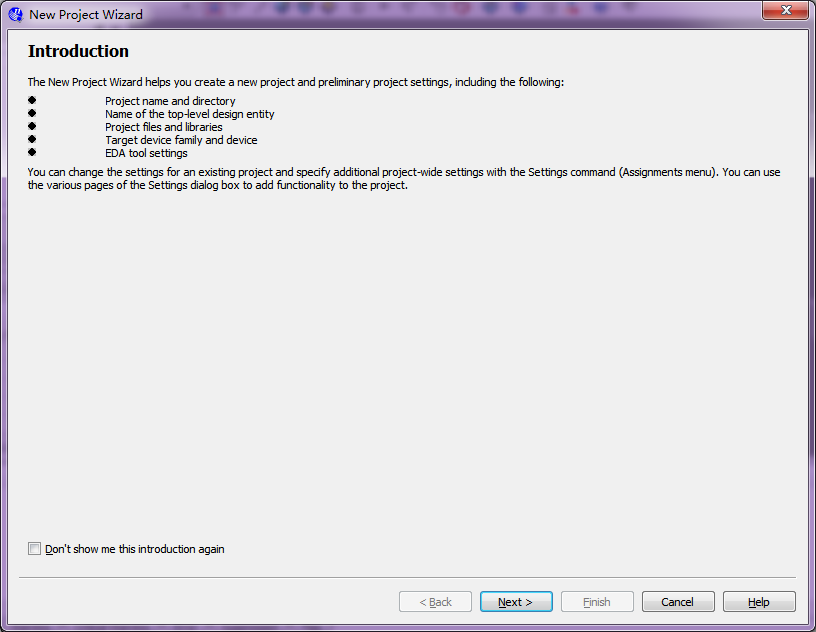

File>New Project Wizard,如图1所示

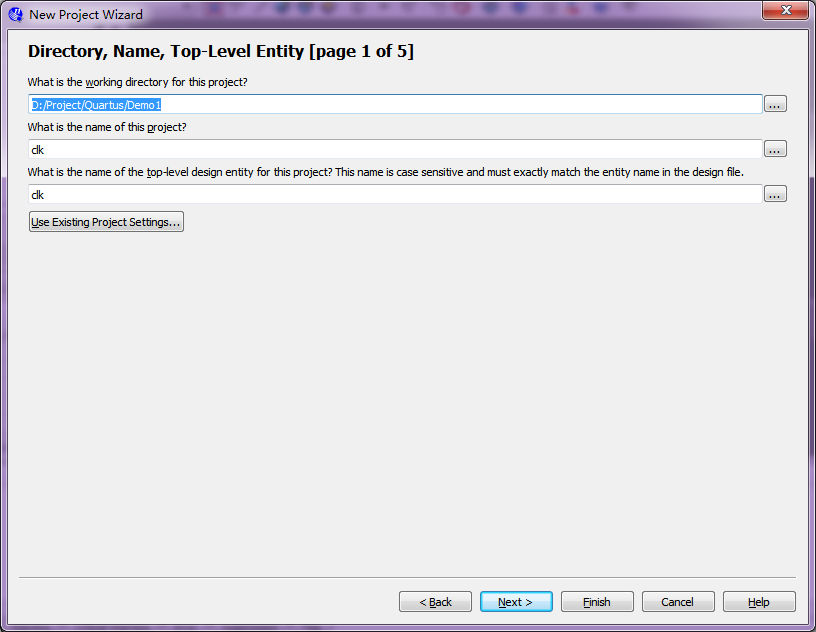

设置工程的文件夹目录及工程名,如图2所示

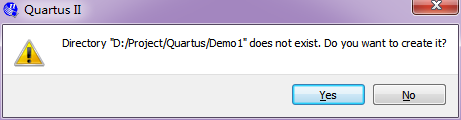

因为还没有创建demo1文件夹,Quartus II弹出一个对话框,询问是否新建所需文件夹,如图3所示。

单击Yes,将会出现图4

如果有已存在的文件,在此框图中添加,如果没,单击Next,将会出现图5

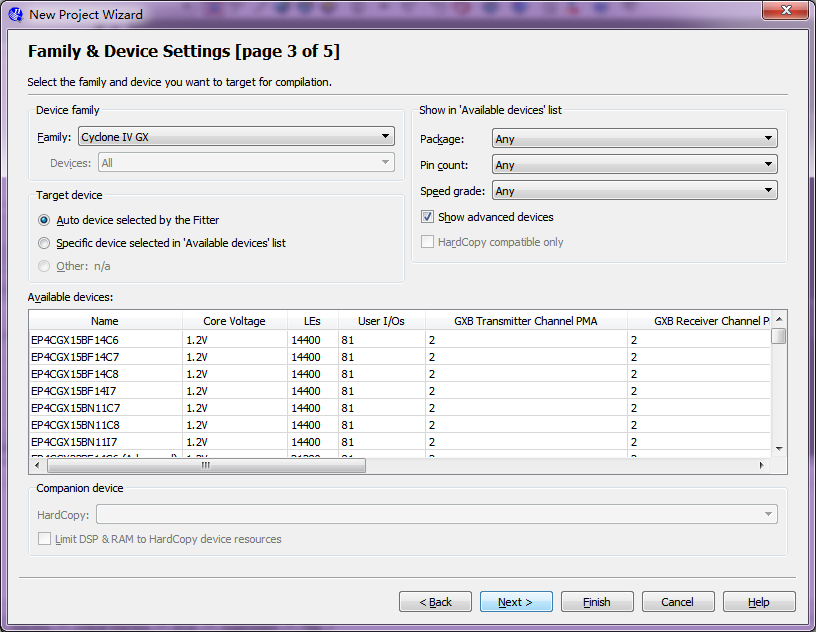

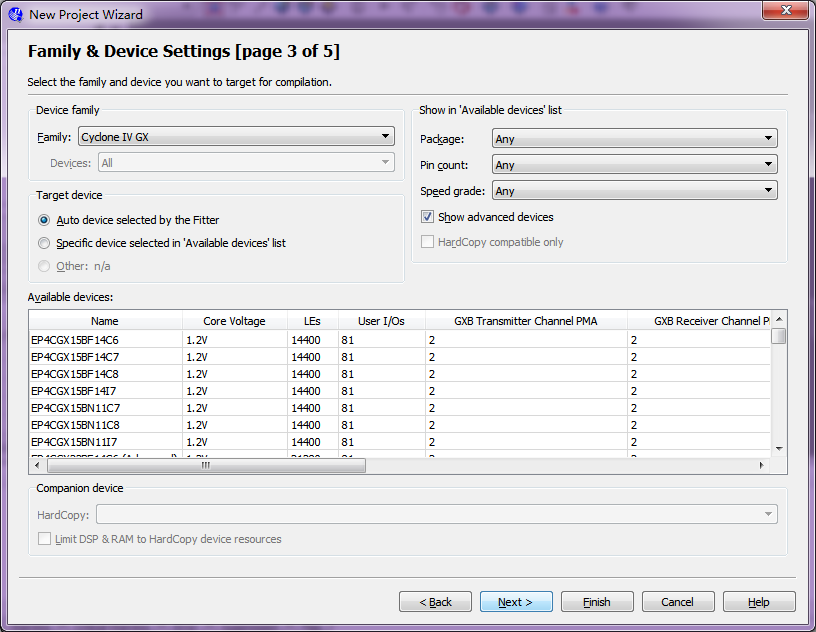

选择器件家族和指定的器件,单击Next,出现图6

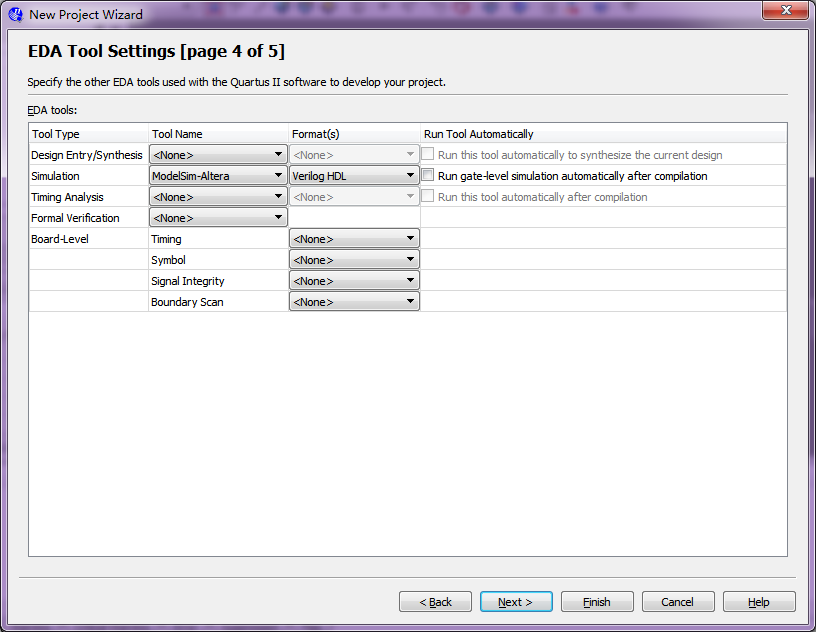

指定一些第三方EDA工具。持续Simulation选用ModelSim-Altera,格式为Verilog HDL。单击Next,出现图7

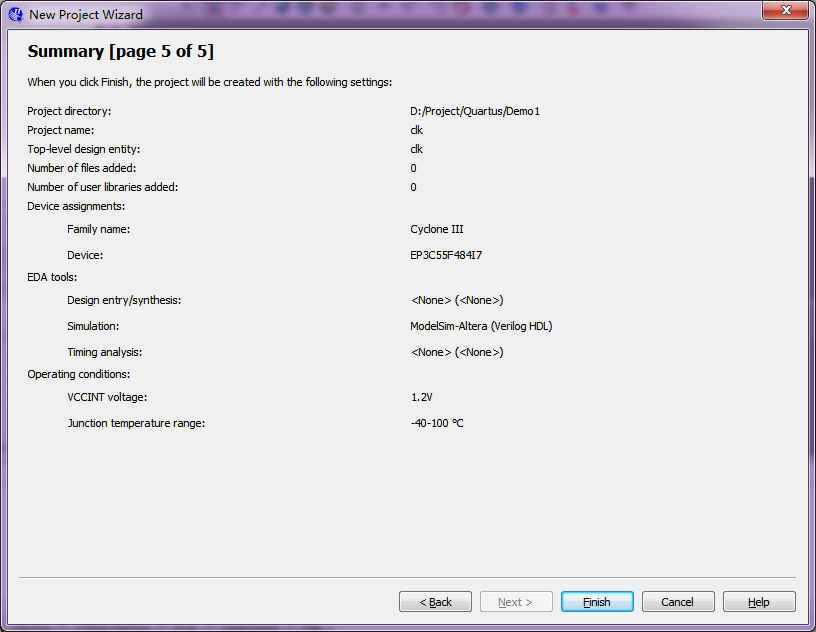

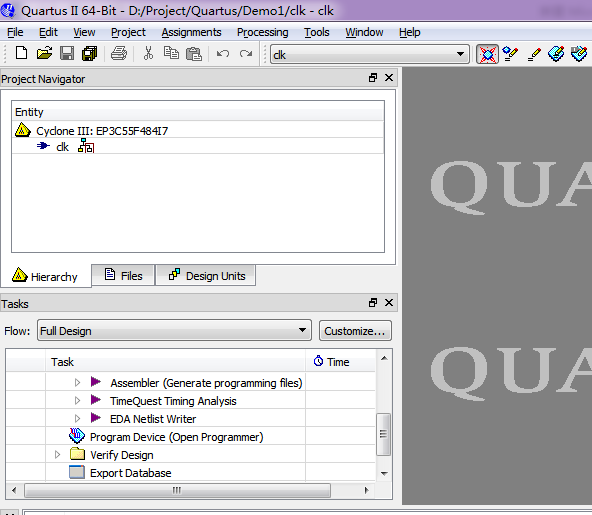

设置一览如图10所示。单击Finish,返回Quartus II主体窗口。标题栏将显示clk工程,如图8所示。

2.编写源程序

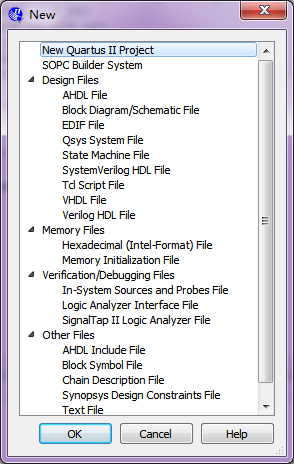

选择File>New打开图9所示窗口,选择Verilog HDL File,并单击OK。这将打开文本编辑器窗口。第一步是指定所创建的文件的名称。

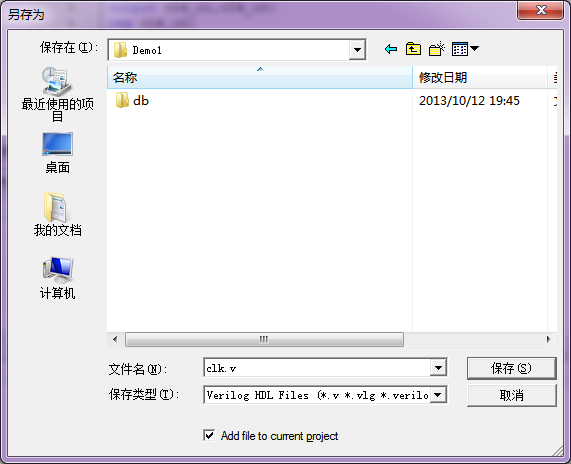

选择File>Save As,打开图10所示的对话框。选择存储类型为Verilog HDL File,填写名称为light.v。单击Save

输入要编写的代码

3.综合编译

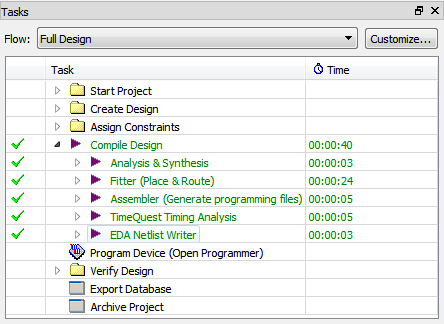

选择Processing>Start Compilation运行编译器,或者单击快捷键按钮运行。在编译过程中,Quartus II的左边会显示不同阶段的进度,如图11。

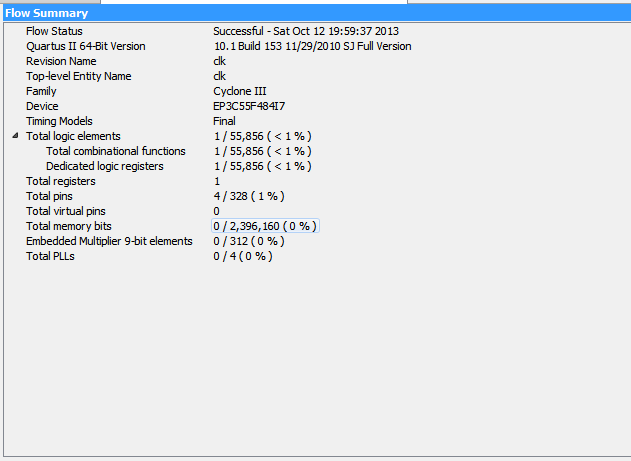

编译成功(或不成功)后,会弹出一个对话框,单击OK。Qartus II会显示图12所示画面的编译报告

4.仿真程序

新建testbench文件,使用文本编辑器新建testbench文件,如图13所示,命名为light_tb.v;不要勾Add file to current project选项,即不可加入到Quartus工程文件夹列表。

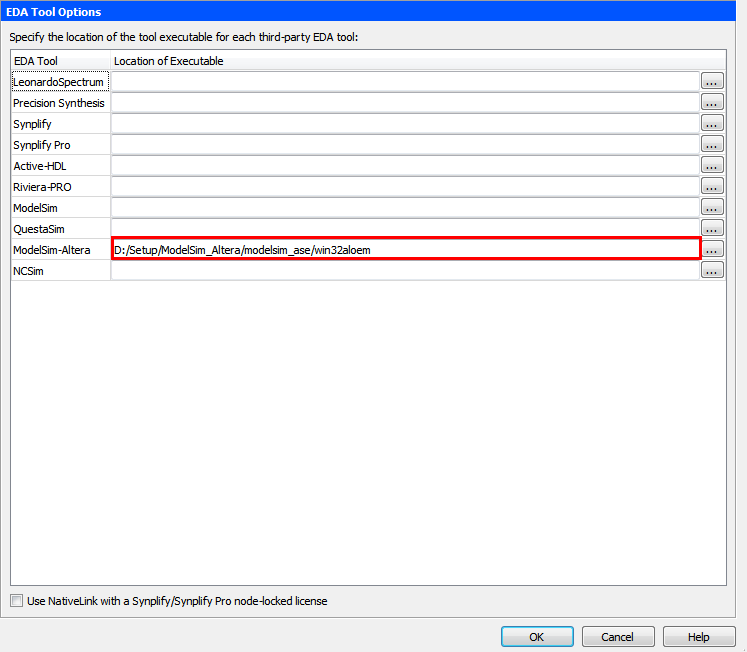

设置ModelSim-Altera路径,第一次使用需要先设置ModelSim-Altera路径。选择Tools>Options>General>EDA Tool Options,打开EDA工具选择,如图14所示,设置路径。

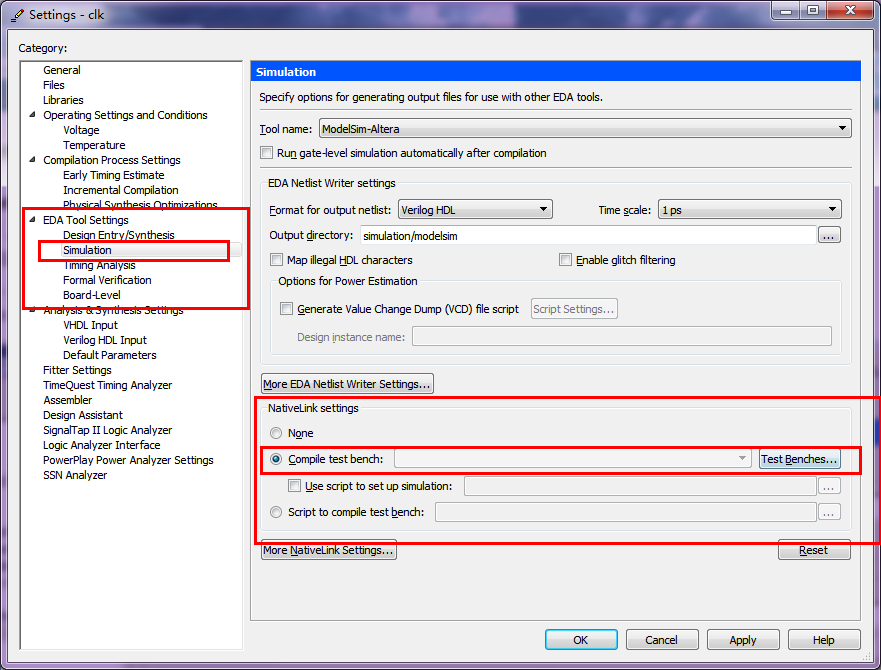

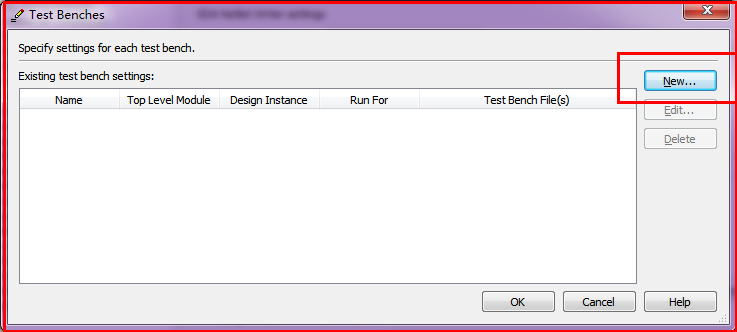

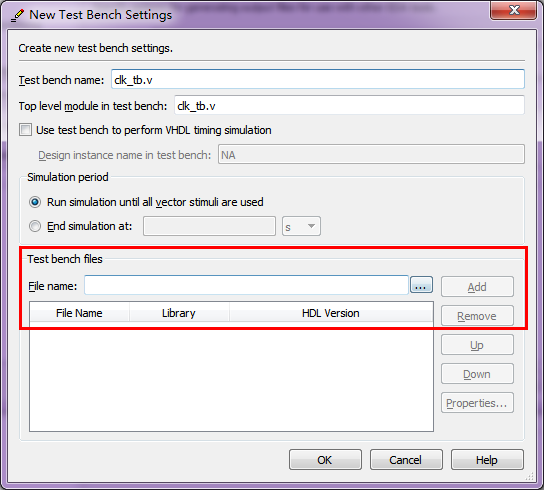

添加仿真所需测试文件,选择Assignments>Setting>EDA Tool Setting>Simulation,打开图15所示窗口。在NativeLink setting下,选择Compile test bench:标签,单击Test Benches按钮,打开图15所示窗口。单击New,弹出设置窗口,命名Test bench name:为clk_tb(与前面编写light_tb.v一致);在File name:处,点击…按钮,添加clk_tb文件路径;单击Add,完成后如图16所示。连续三次单击OK,返回Quartus II主题窗口。

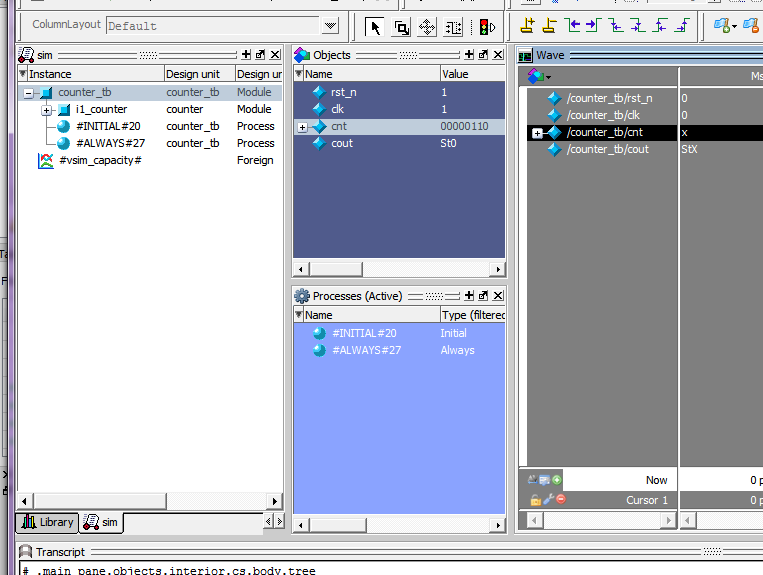

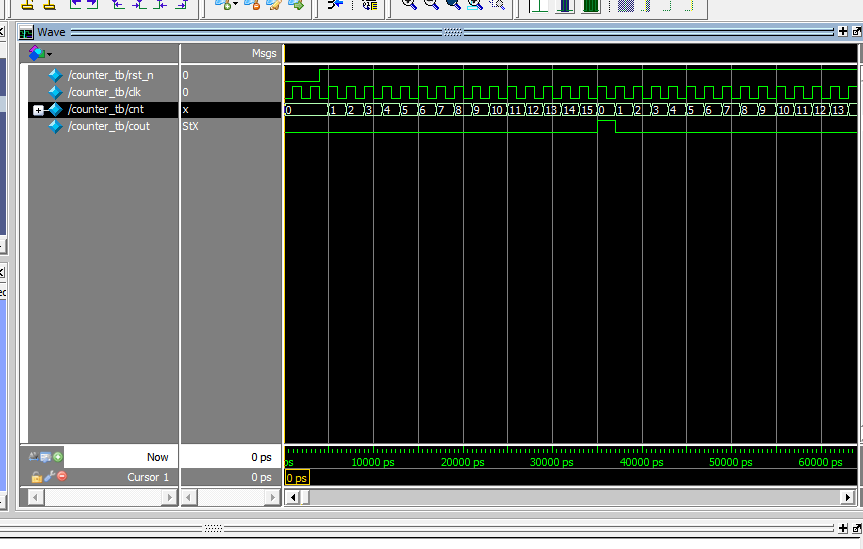

开始仿真,选择Tools>Run EDA Simulation Tool>EDA RTL Simulation,进行RTL仿真;或者选择Tools>Run EDA Simulation Tool>EDA Gate Level Simulation,进行门级仿真。此处以RTL仿真为示范。选择选择Tools>Run EDA Simulation Tool>EDA RTL Simulation,弹出图17所示仿真画面。稍等片刻,波形就会显现。