记录背景:最近由于想实现GMIItoRGMII的功能,因此需要调用ODDR原语。

ODDR:Dedicated Dual Data Rate (DDR) Output Register

通过ODDR把两路单端的数据合并到一路上输出,上下沿同时输出数据,上沿输出a路下沿输出b路;如果两路输入信号一路恒定为1,一路恒定为0,那么输出的信号实际上就是输入的时钟信号。

调用的Verilog语句是:

1 // ODDR: Output Double Data Rate Output Register with Set, Reset 2 // and Clock Enable. 3 // 7 Series 4 // Xilinx HDL Language Template, version 2017.4 5 6 ODDR #( 7 .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE" 8 .INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1 9 .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" 10 ) ODDR_inst ( 11 .Q(Q), // 1-bit DDR output 12 .C(C), // 1-bit clock input 13 .CE(CE), // 1-bit clock enable input 14 .D1(D1), // 1-bit data input (positive edge) 15 .D2(D2), // 1-bit data input (negative edge) 16 .R(R), // 1-bit reset 17 .S(S) // 1-bit set 18 ); 19 20 // End of ODDR_inst instantiation

模式解释:

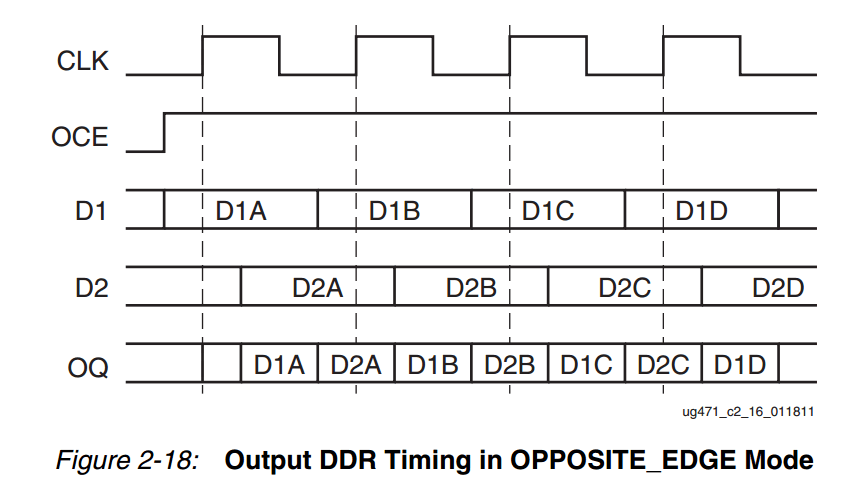

OPPOSITE_EDGE模式:

在此模式中,时钟边沿被用来以两倍的吞吐量从FPGA逻辑中捕获数据。这种结构与virtex-6的实现比较相似。两个输出都提供给IOB的数据输入或者三态控制输入。

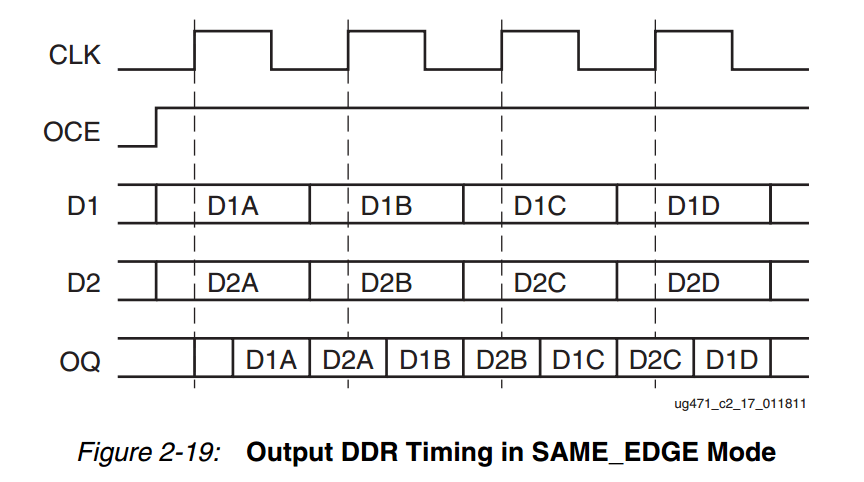

SAME_EDGE模式:

在此模式下,数据可以在相同的时钟边沿从给IOB。相同的时钟沿将数据送给IOB可以避免建立时间违规,并允许用户使用最小的寄存器来执行更高的DDR频率来进行寄存器的延迟,而不是使用CLB寄存器。

注意:

1、set和reset不能同时置位;

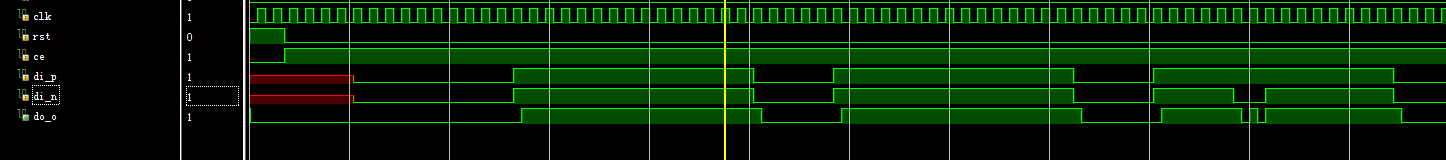

2、ODDR原语的复位需要约12个clock,第一次输入的数据可能会有问题(亲测),[由于公司网络的原因,无法上传图片],但亲测是如此。

修改代码前:

wire oddr_do_test; oddr_test oddr_test (.clk(tx_clk), .rst(rst), .ce(~rst), .di_p(tx_en), .di_n(tx_er), .do_o(oddr_do_test) );

增加如下代码:

wire oddr_do_test; reg [5:0]tx_en_d; reg [5:0]tx_er_d; always @ (posedge tx_clk) begin tx_en_d <= {tx_en_d[4:0],tx_en}; tx_er_d <= {tx_er_d[4:0],tx_er}; end oddr_test oddr_test (.clk(tx_clk), .rst(rst), .ce(~rst), .di_p(tx_en_d[5]), .di_n(tx_er_d[5]), .do_o(oddr_do_test) );