【From EETOP 论坛】

大家好,最近中兴事件火热,连朋友圈的医生,律师, 退休的大爷大妈们都在讨论,似乎有全民ICer的架势。分析的文章层出不穷,咱们DFT Eliter就不发表评论了,专心分享IC业内知识,培养全能DFT人才,此为正道。

大家可能问到:DFT到底是什么?你们是芯片设计师?还是验证工程师?还是测试工程师?还是搞foundry的?

借此机会,今天这篇文章就借用欧美常用的5W2H系统,分析一下DFT到底是什么。

什么是DFT?

DFT是Design For Test的缩写。 是指在芯片设计过程中引入测试逻辑,并利用这部分测试逻辑完成测试向量的自动生产,从而达到快速有效的芯片测试的目的。

DFT的工作包括

-- 在项目初期规划DFT架构;

-- 在RTL级别设计测试电路;

-- 在验证阶段验证测试电路;

-- 在synthesis阶段实现测试逻辑的插入;

-- 在测试阶段提供测试向量;

为什么要有DFT? WHY?

1958年Jack Kilby发明了第一只包含一个双极性晶体管,三个电阻和一个电容的集成电路。从那一个半导体集成电路开始了飞速的发展。 到目前为止, 以14nm工艺的基带芯片为例, 一个仅60mm2的芯片上就集成了30多亿个逻辑门。

高度晶体管集成同时也意味着高度的功能性集成。 在集成电路的产业初期, 功能性的测试足够能满足芯片测试的需要。 而在今天,数以十亿计的逻辑门任何一点生产的缺陷就能导致功能障碍。 用功能性测试去覆盖这些错误无疑是高成本,高时间,高复杂性的。

于此同时,摩尔定律下的半导体产业每18个月集成度就翻一倍。 工艺开发的和半导体的学习曲线都需要有一个切实可行的解决方案。 DFT就是随着集成电路产业的发展而建立起来的。

Tips:

[1]DFT的测试内容不同与功能性测试。

[2]功能性测试是为了验证设计出的是想要的;

[3]DFT测试是为了检测生产出的就是设计的。

WHERE?

哪些地方需要DFT?

半导体产业分为分立器件和集成电路两大块。

分立器件上的晶体管数目有限,采用DFT策略显然是不经济的。 集成电路部分才是DFT大展拳脚的领域。

集成电路由于其高集成性,功能模块繁多,工作模式也极其复杂。 在这一背景下,板极的功能性测试需要较长的时间,复杂的测试设计不能满足生产过程[1]中的大批量测试的要求。需要有DFT测试电路实现大规模大批量低成品的测试要求。

此外, SoC上的存储器(memory)的集成度也在不断加大。片上memory array的测试如果仅借助与功能性测试无疑是不全面而且耗时的。 memory的高度集成也需要DFT技术的帮助。

汽车类电子等对由于安全性需求对DPM[2]要求极高的产业也许要DFT技术。 想象一下随着电动汽车,新能源,5G的发展,自动驾驶离大众日常生活越来越近。 自动驾驶需要有强大的计算芯片来处理大量的感应器传回来的数据,给出正确的反应。在这里,任何一个硬件错误付出的都是血的代价。 DFT的测试方案可以覆盖整个芯片,达到要求的DPM。

Tips:

[1] 仅以2014年为例。半导体行业平均每秒生产出8trillion个晶体管。

[2] DPM是指Defects per million parts。

DFT的工作对象是什么?

DFT需要处理基本上芯片所有逻辑的测试。

他们包含:

1.片上存储器

2.模拟模块 (如锁相环,LDO,IDV等)

3.系统控制模块

4.时钟控制模块

5.电源管理模块

6.寄存器

DFT基本参与了所有的芯片功能,需要提供芯片初始化时FUSE的管理;需要设计协调时钟,复位,电源等控制逻辑确保测试功能的实现,同时不影响芯片正常的工作模式。

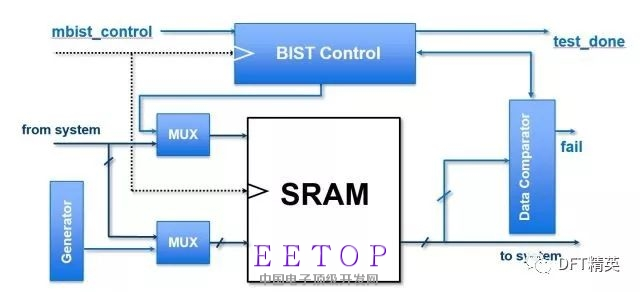

对于片上存储器,由于其分布的复杂性,需要统筹设计mbist的分布,以最小的代价实现测试覆盖。

除此之外, 芯片中功能模块的每一个寄存器都是扫描链测试的工作对象。任何一个寄存器,或者寄存器之间的组合逻辑发生故障,都需要能被DFT的方法侦测到。

WHEN?

DFT在什么时候参与进芯片设计过程?

如我们在上期推送中所描述的,在整个芯片开发流程中,除了流片和封装这两步以外,其他每一个阶段DFT都有其不同的工作。

简单说就是:

在架构阶段定义好DFT的架构

在设计阶段实现DFT的逻辑和验证

在后芯片阶段做好silicon bringup的辅助。

HOW?

如何做DFT?

随着1990年IEEE 1149.1关于JTAG[1]的标准发布, DFT的方法学慢慢建立起来。

测试的难度是随着芯片的集成度的增加而增加的。 高度集成的芯片的外部管脚数目有限。 芯片内部所有逻辑(3 billion + gates)都需要利用这些管脚实现测试。

1. JTAG

DFT方法之一就是在芯片内部建立TAP[2],以及一系列的测试寄存器,即JTAG. 通过JTAG网络增加测试的控制点和观测点,以实现后期的测试。

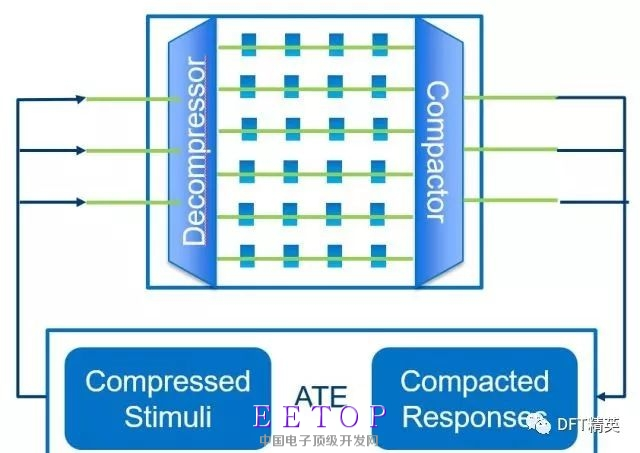

2. scan/EDT

对于寄存器以及寄存器之间的组合电路,则发展了扫描链的概念,将逻辑芯片抽象为寄存器逻辑和组合电路逻辑。通过扫描的方式将测试激例打入芯片,然后再以扫描的方式观测测试结果。

3. Mbist

对于片上存储器,常用的测试方法为mbist逻辑的插入。通过mbist pattern产生器,产生特定的数据读/写入特定地址,并将读出的地址做比较的是memory pass 或 fail结果。

4. 其他

其他测试方法还包含analogBist, LogicBist,BSD,Reliability Test等各种方法。 这些方法我们将会在后面的推送中陆续接受。

Tips:

[1]JTAG 是指(Joint Test Action Group,联合测试行动小组)是1985年制定的检测PCB和IC芯片的一个标准,1990年被修改后成为IEEE的一个标准,即IEEE1149.1-1990。

[2]TAP Test Access Port 测试访问口。

HOW MUCH?

DFT的代价?

世界上没有免费的午餐。DFT逻辑在给芯片设计生产带来众多优势的同时,也要付出 一定的代价。

1.测试逻辑占用芯片面积。 (例如基带芯片中>10%)

2.扫描覆盖率越高,测试向量越多

3.并行测试由于电源的限制不能无限增多

4.管脚数目的限制导致测试和测试逻辑复杂度增加

5.优秀的DFT架构和实现才能带来高质量的测试

半导体产业技术目前为止一直遵循者摩尔定律,按照三星的说法,直到5nm不会有根本性的困难。

事实上,从DFT诞生开始,DFT的方法就一直在进化。无论是fault模型,还是测试方法,DFT一直在进步。

5nm之后,不管半导体走向何方,More Moore; More than Moore; Beyond CMos,

只要芯片还是高度集成的,DFT一直会被需要。