什么是Clock Jitter和Clock Skew,这两者有什么区别?

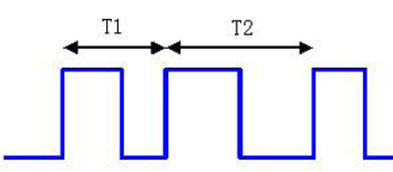

Clock Jitter(时钟抖动):是指芯片在某个给定的时间点上时钟周期发生暂时性变化,从而导致时钟在不同的周期上加长或者变短。换句话来说就是指,两个时钟周期之间存在差值,这个误差是在时钟内部产生的,与晶振或者内部的PLL有关。与时钟的布局布线无关。具体如下图所示为直观表现:

那么根据上图所示,可以得到适中的抖动值:Jitter = T2 - T1。除此之外,还有一种由于周期内信号的占空比发生变化而引起的抖动,称之为半周期抖动。总的来说,jitter可以认为在时钟信号本身在传输过程中的一些偶然和不定的变化之总和。

时钟偏移(Clock Skew):是由于布线长度及负载不同引起的,导致同一个时钟信号到达相邻两个时序单元的时间不一致。话句话说就是,时钟偏斜指的是同一个时钟信号到达两个不同寄存器之间的时间差值,时钟偏斜永远存在,到一定程度就会严重影响电路的时序。如下图所示:

总结:

skew通常是时钟相位上的不确定,而jitter是指时钟频率上的不确定(uncertainty)。造成skew和jitter的原因很多。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。而由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,就是jitter。

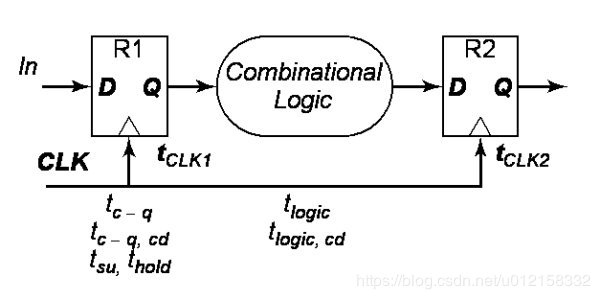

skew和jitter对电路的影响可以用一个简单的时间模型来解释。假设下图中t(c-q)代表寄存器的最大输出延迟,

t(c-q, cd)表示最大输出延时;t(su)和t(hold)分别代表寄存器的setup, hold time(暂不考虑p.v.t)差异;t(logic)和t(logic, cd)分别表示最大的组合逻辑传输延迟和最小组合逻辑传输延迟;

在不考虑skew和jitter的情况下,及t(clk1)和t(clk2)同频同相时,时钟周期T和t(hold)需要满足:(1)T > t(c-q) + t(logic) + t(su):(2)t(hold) < t(c-q, cd) + t(logic, cd)这样才能保证电路的功能正常,且避免竞争的发生。如果考虑CLK2比CLK1晚t1的相位,及skew=t1。则 t(hold) < t(c-q, cd) + t(logic, cd) - t1,这意味着电路由更大的倾向发生hold time violation;如果考虑CLK1比CLK2晚t2的相位,及skew=-t2,则 T > t(c-q) + t(logic) + t(su) + t2这意味着电路的性能下降了,但由于R2的hold time始终满足,所以不会有竞争的麻烦存在。

clock uncertainty = clock jitter + clock skew.