二进制加法

半加器(Half Adder)

半加器的功能是将两个1位二进制数相加。输入端口A、B,输出端口S(输出),C(进位)。

其有一个很明显的缺点:不能将低位的进位参与运算。

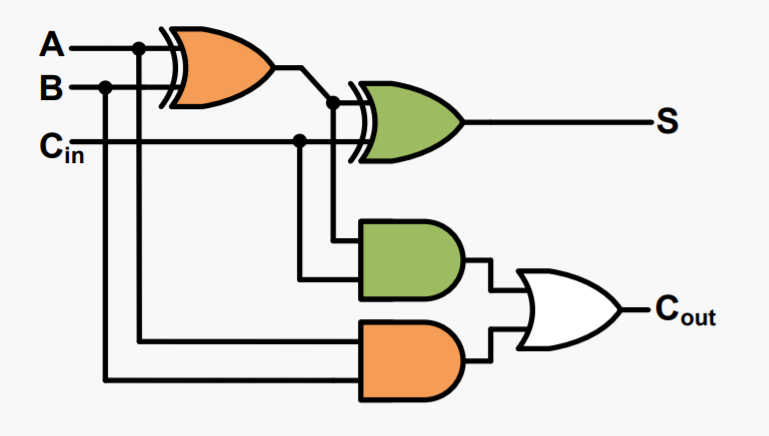

全加器(Full Adder)

全加器由两个半加器构成。输入端口A、B、Cin,输出端口S(和)、Cout(进位输出)。

有了全加器,只要将它简单的连在一起就能实现多位的加法器。

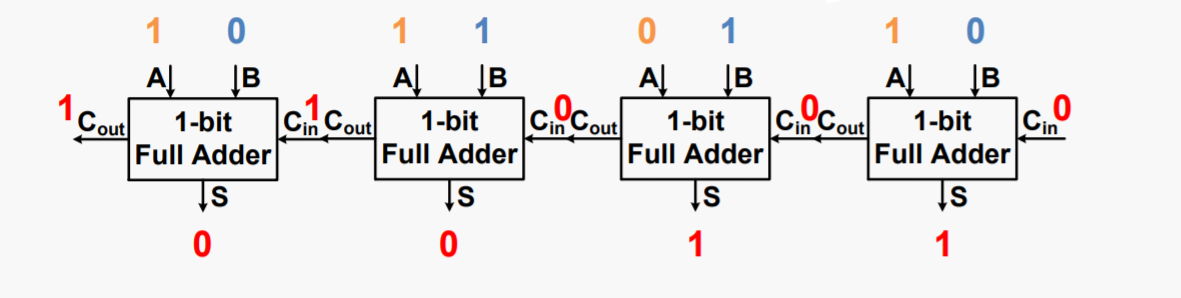

4-bit 加法器

例如求 (1101)2 + (0110)2,答案应该为和为 (0011)2,进位为1.可以用4个全加器构成4-bit全加器来实现,如图

显而易见,这个图可以推广,所以这样就能得到32-bit的加法器。

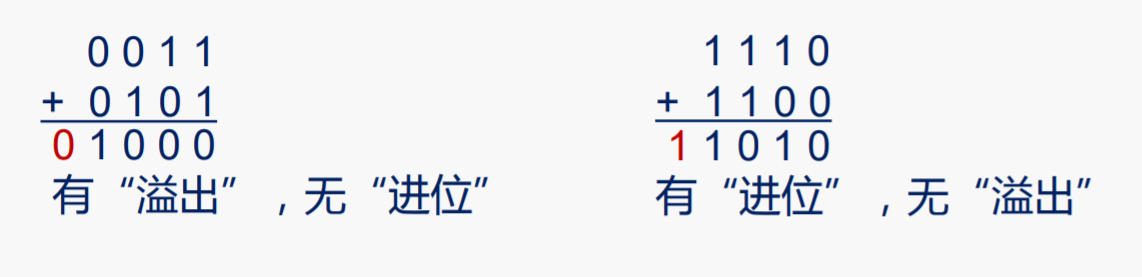

溢出

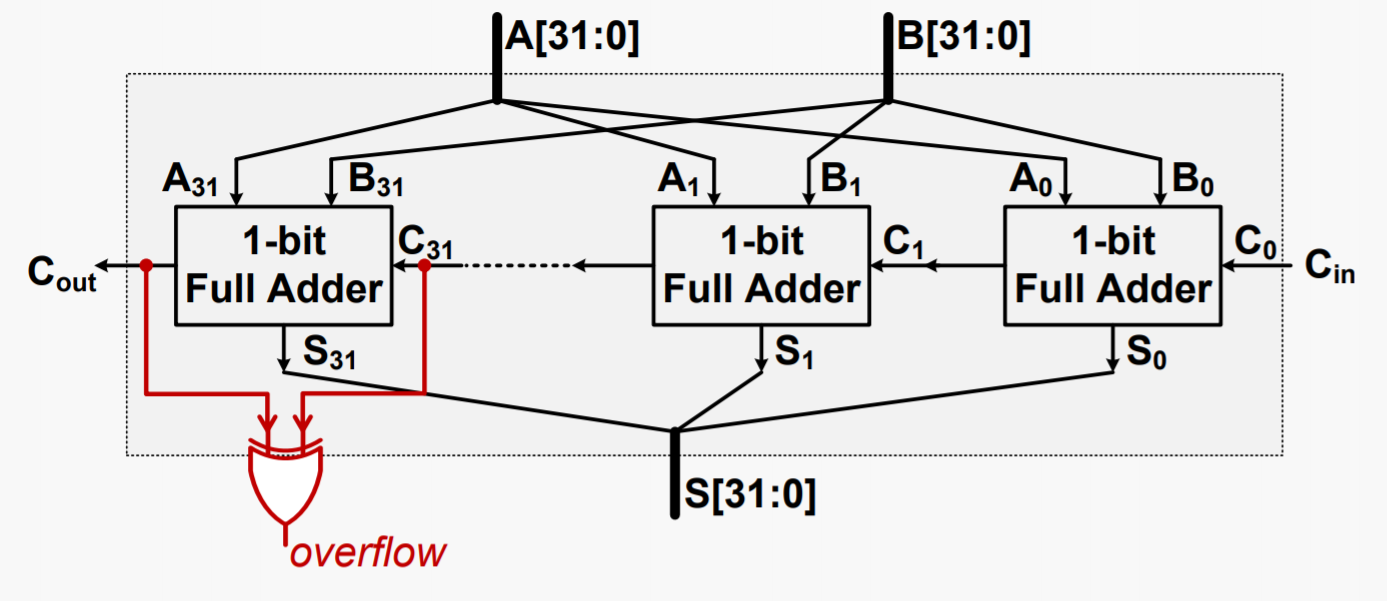

检查加法结果是否溢出

溢出(overflow):是指运算结果超出了正常的表示范围

- 溢出仅针对有符号运算而言的,发生溢出有两种情况:两个正数相加,结果为负数;两个负数相加,结果为正数。其实,无符号时可看作是mod 2k(k是最大位数),既然取模了,自然不用考虑溢出

- 有溢出不一定有进位、有进位不一定有溢出

- 有符号加法和无符号加法在运算时硬件电路是一样的,只是对结果的解读不同

4-bit运算时

溢出的检查方法

“最高位的进位输入”不等于“最高位的进位输出”,说明产生了溢出。

经过一个异或门,如果C31和Cout 不相等,overflow被设为1,表示溢出。(为什么可以通过这种方法判断呢?)

对溢出的处理方式

MIPS

提供对两种不同指令分别的处理

- 将操作数看作有符号数,发生“溢出”是产生“异常”,如add rd,rs,rt addi,rt,rs,imm

- 将操作数看作无符号数,不处理“溢出”,如addu rd,rs,rt addiu rt,rs,imm

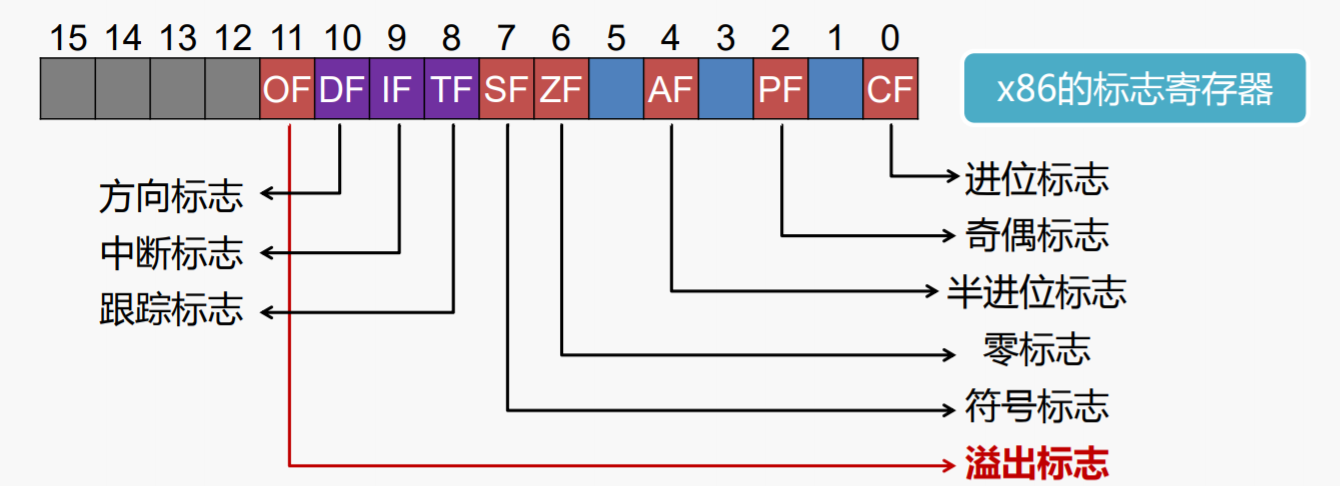

X86

设有“溢出标志OF”(Overflow Flag)。如果把操作看作有符号数,若发生溢出,则自动设置OF=1;否则OF=0。

二进制减法

原理

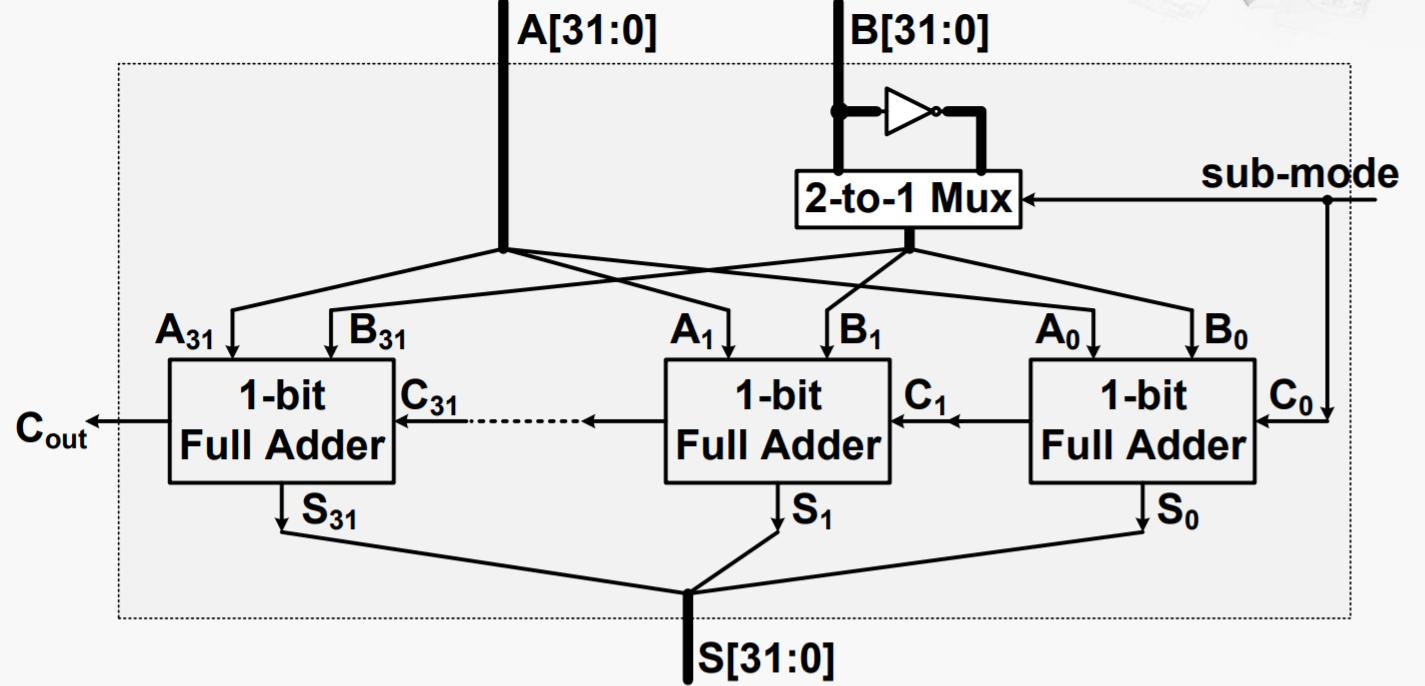

- 减法运算可转换成加法运算

- 只需将负数变成它的补码,补码与原码之间的转换规则:按位取反、末位加一

- A - B = A + (~B + 1)

实现

这其实是一个加法和减法器,与之前的32-bit加法器相比,在输入端B多了一个二选一多路选择器,当sub-mode为0,是加法模式,也没有来自低位的进位;当sub-mode为1时,是减法模式,首先B按位取反,同此同时sub-mode为是低位的进位,刚好是-B = ~B + 1.

参考链接:https://www.coursera.org/learn/jisuanji-zucheng/lecture/ydYAV/305-jia-fa-he-jian-fa-de-shi-xian