一.OCC缘由

何为全速测试(at speed test):在工艺节点在130nm以下的时候,很多情形下的物理缺陷都是由于延时来引起的。

因此在对这种类型的chip做dft的时候,需要建立一个新的故障模型,业内称之为延时故障模型(time delay model)。

解决的方法就是全速测试,所谓的全速测试就是让芯片工作在自己高倍时钟频率上,这个频率往往是要高过ATE的时钟的。

这样对扫描模型的建立就提出了新的要求。即至少要保证芯片的latch clock和capture clock为芯片内部的高倍时钟。

synopsys对此种问题的解决方法就是OCC(on chip clocking)。

OCC/OPCG的基本原理是在 scan shift 模式下, 选通慢速的ATE 时钟,load 或 unload 扫描链; 在 capture 模式下,对 free-running PLL clock 过滤筛选出 lauch 和 capture clock 进行at-speed 测试 。

在做SCAN的时候,由于ATE时钟速度和芯片port的传输速度的限制,导致ATE无法向片传输高速时钟。

但是,芯片内部需要 进行At Speed 测试的时候,用到和system mode一致的时钟频率进行测试。此时,需要由芯片内部自己产生测试时钟。

二. 典型OCC电路结构

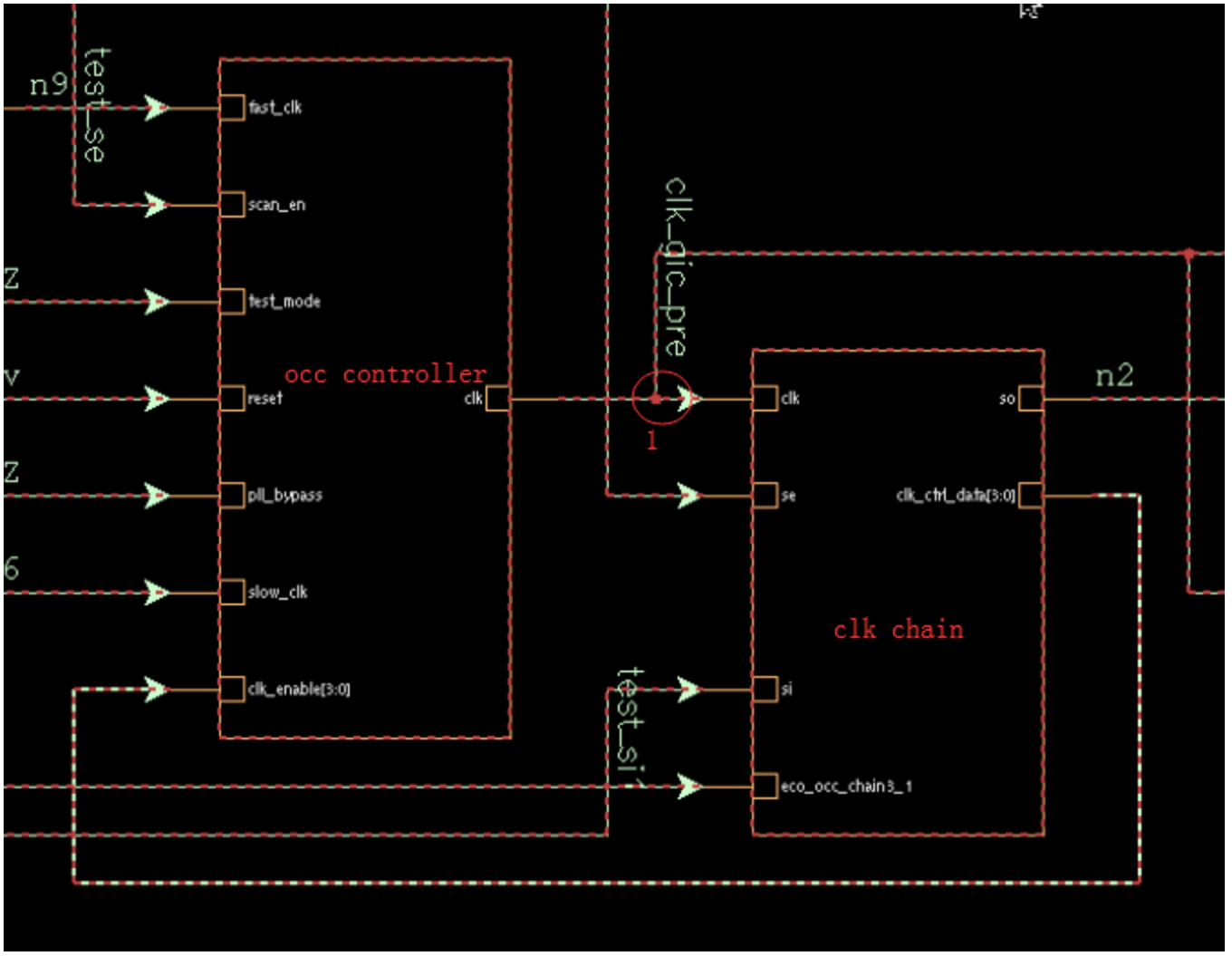

这个是典型的OCC(On Chip Clock)电路。主要有两部分组成,一个是occ controller,另外一个是clock chain。

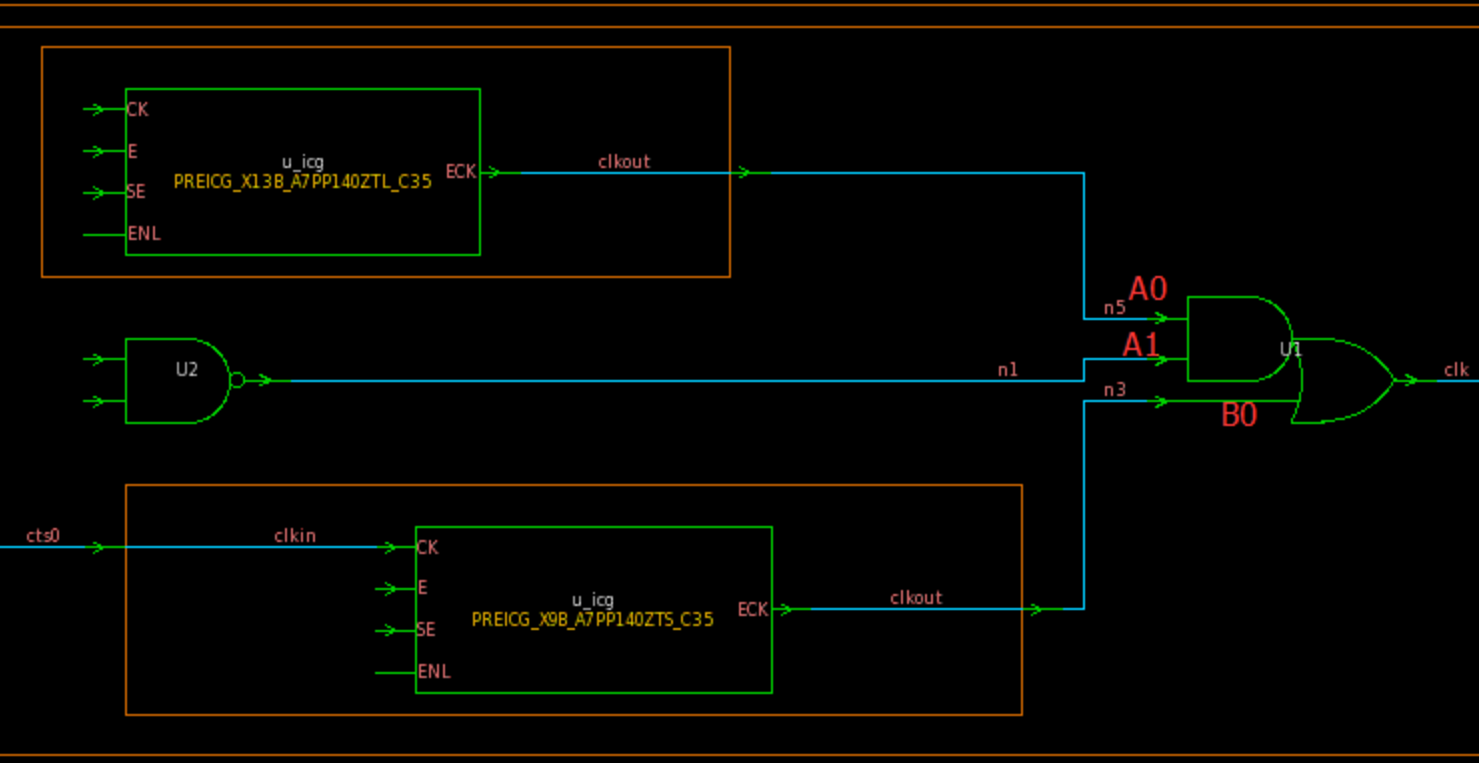

其中occ controller的核心电路如下图所示。其中A0接func_clk,A1接pllbypass,B0接occ_clk。

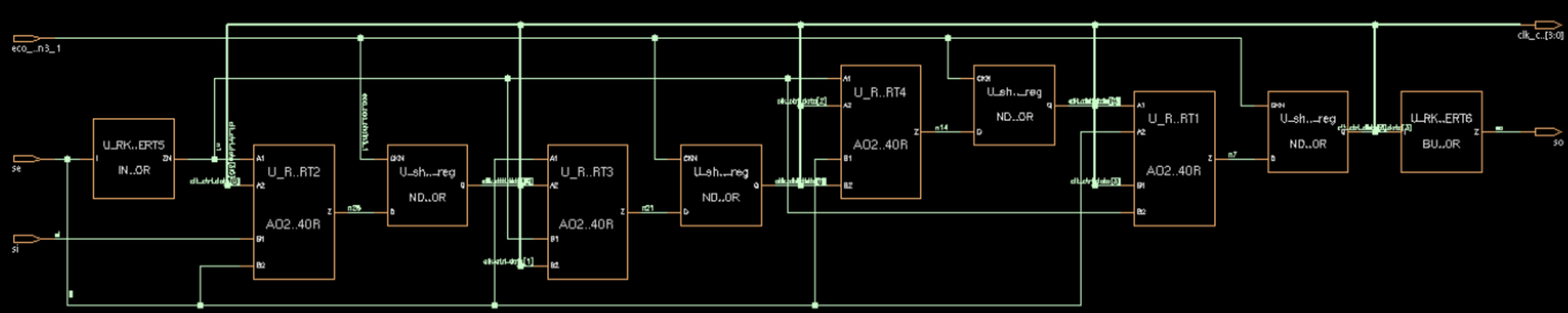

clock chain的电路原理图如下所示。

OCC电路插入方式主要有两种方式,目前大部分应该还是采用第一种方式,如在综合dft阶段工具自动插入的方式。

1. DFT Compiler自动插入。

2. 手动编写OCC 的verilog 电路,在dft_insert阶段。

三.OCC电路的时钟树综合

针对design中这种常见的时钟树结构,应该如何长时钟树呢?稍微有点实际工作经验并认真分析过时钟树结构的工程师,都应该能够做好这部分的时钟树。如果你认为让工具自己来,能够做好这部分tree的话,我是绝对不相信的。

细心的朋友会发现,我其实已经把时钟结构图都给出了,并且图上还特定标注了一个数值“1”。有了这个图之后,你的脑子里马上就应该要有个各路时钟的走向。时钟从哪里来,它将要去哪里。

如果不稍加引导工具来做tree,本案例工具长出来的tree一定会把occ那路时钟和function clk做balance。而本来occ那路时钟其实可以做的比较短。occ那路时钟被拖长之后就会有一系列的问题,比如绕线问题,比如clock chain中reg到occ controller中reg的hold timing问题。

那么,看到这里你们是否已经知道如何来长OCC电路这部分的clock tree呢?今天小编暂时不公布答案,让大家先自己独立思考。

1.获取图中 “1” output的所有load,这部分包含正常的reg和clk chain中的reg

2.将这两组reg归类到不同的组,disconnect这些net,并插入guide buffer,注意是clock buffer

3.在guide buffer后create 两路clock

4.分别对这两路时钟做时钟树综合

Tips:

1.尽量把时钟分得比较干净,能各自长tree的尽量各自长自己的。

2.尽量用“分段长tree的思想“。

3.可以对clock做eco。