使用PrimeTime PX进行功耗分析有两种:一种是平均功耗的分析Averaged power analysis,一种是Time-based power analysis。

电路的功耗主要有两种,一种是漏电流功耗(Leakage Power),也就是一个单元在没有switching,inactive或者static情况下的功耗,包括intrinsic leakage power和gate leakage power。

其中intrinsic leakage power主要是由source-to-drain的漏电流引起,也包括扩散区diffusion layer和基底substrate之间的电流泄露。

Gate leakage power是由source-to-gate和gate-to-drain的漏电流引起,随着工艺尺寸的降低diminish,它已经成为主要的漏电流功耗来源。Gate leakage power主要依赖于gate oxide的厚度和电压强度,不依赖于温度。

另外一种是Dynamic Power,是指电路在active时候的功耗,包括internal power和switching power。

Internal power是指在boundary of cell内的动态功耗,包含cell内部的电容充放电,PN节之间的瞬时短路(momentary short circuit, P晶体管和N晶体管在关闭打开过程中间的某一短暂时刻,会短路,导致从VDD到GND的瞬时电流).因此,对于具有较慢transition time的电路,short-circuit power能够占到总的gate power的50%。

Switching power是由一个cell的输出端负载电容的充放电导致的(power dissipated by the charging and discharging of load capacitance at the output of the cell).总的load capacitance是输出驱动端(driving output)net和gate电容的累加。

Averaged mode: SAIF, VCD, set_switching_activity, Tool defaults

Time-based mode: RTL-VCD, Gate-Level VCD (Peak power)

关于SAIF和VCD的区别:

SAIF: SAIF stands for Switching Activity Interface Format. The SAIF files capture signal transitions and the time spent at each logic level. The SAIF file contains the toggle counts and static probabilities for the nets in the design. SAIF is supported only in the averaged power analysis mode. Use the read_saif command to annotate the activity information in the SAIF format.

VCD: VCD stands for Verilog Change Dump format. It is an event-based format that contains every value change for the signals in the design and the time at which they occurred. Use the read_vcd command to specify the VCD file in both the averaged and time-based analysis modes. Use the read_vcd command to specify the activity files in other event-based formats within the PrimeTime PX tool. Internally, the tool converts these formats to the VCD format using the appropriate utility.

VCD文件示例:http://en.wikipedia.org/wiki/Value_change_dump

这里只关注Gate-level的功耗分析,对于RTL level的,需要进行一系列的mapping操作。

首先看SAIF文件格式

对于Gate-level的SAIF文件,报刊每个单元activities的反标,用来计算平均功耗。使用read_saif来读取saif文件。

SAIF文件的产生有多种途径,甚至可以由VCD文件转换(vcd2saif),也可以在simulation中获得,这里补充一下,使用Synopsys的VCS MX可以对Verilog、System Verilog和VHDL的工程实现混仿。这里需要关注Power Compiler的文档。

VCD文件格式

同样,对于VCD文件格式,也有RTL和Gate-level之分,对于RTL level的VCD文件,需要使用read_vcd –rtl或者read_vcd –zero_delay读取activity file。read_vcd默认为读取gate-level的文件。

对于VCD文件,同样可以使用VCS或者其他的HDL仿真环境来产生。

在time-based的功耗分析模式,PT PX不支持多个activity VCD文件的读入。在读取VCD文件的时候,经常会出现VCD hierarchy与当前design不匹配的情况,导致最终反标成功的cell为0,这个mismatch主要是由于当使用read_vcd -strip_path来指定当前的design时,-strip_path选择错误,或者VCD文件没有包含所有的design hierarchy。

使用PT PX的重要内容之一是name mapping,主要是对于RTL级别的design进行功耗分析的时候,需要将RTL级别的activity与门级网表进行map。这里不赘述。

Averaged Power Analysis

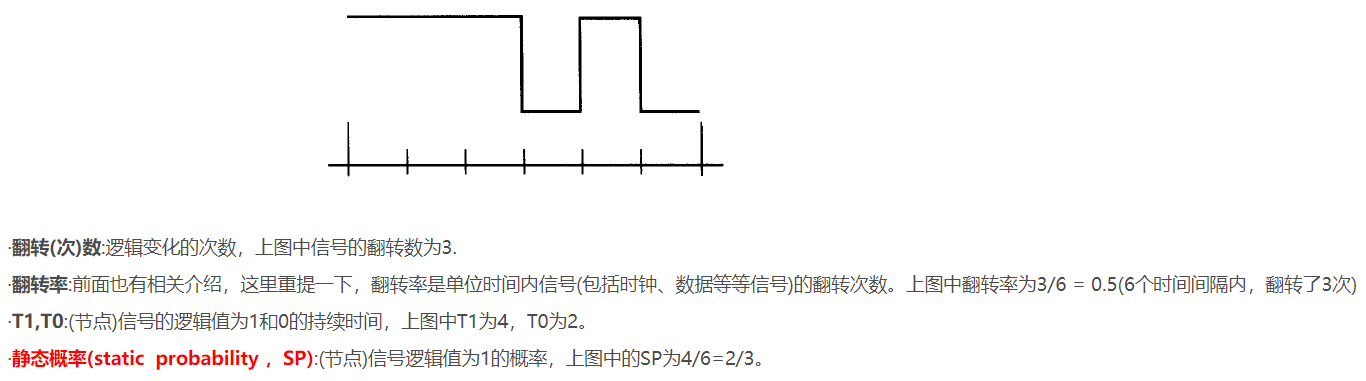

进行平均功耗的分析需要的switching activity主要包含static probability和toggle rate两个参数。

Static probability是某个信号在某一个特定logic state下的概率,比如,SP1和SP0就是某个信号在logic-1和logic-0下的概率。SP是一个信号在某一个状态的时间/总的仿真时间,得到的一个比值,比如SP1=0.7表示在70%的时间这个信号等于1.

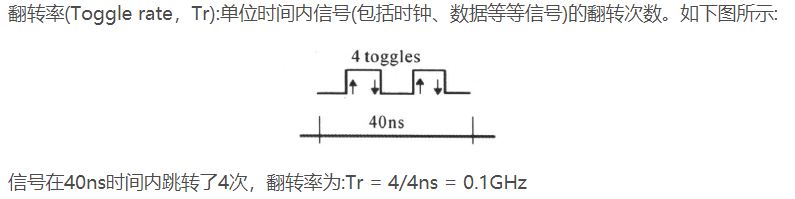

Toggle rates是一个对象,比如net、pin、port在per unit time下的0->1和1->0的transition数目。由TR表示。

行为反标的方法包括:

Annotation of RTL or gate-level VCD files with read_vcd command

Annotation of RTL or gate-level SAIF files with the read_saif or merge_saif commands

使用VCD文件进行反标:

read_vcd -strip_path TB/DUT my.vcd

-strip_path指定当前实例化的设计的path。

需要注意的是,在做平均的功耗分析的时候,PT PX支持读入多个VCD文件,但是条件是需要指定不同的时间,在使用read_vcd命令的时候使用-time指定。

read_vcd还支持有条件的功耗分析,使用-when开关,比如说指定分析在某个信号为true时候的功耗。

使用SAIF文件的时候,涉及的commands有read_saif (read_saif -strip_path TB/DUT my.saif)、merge_saif和write_saif.

当分析不同时钟频率情况下的功耗的时候,需要set_app_var power_enable_analysis true,并且使用set_power_clock_scaling的命令。

当simulation的activity文件无法得到时,需要用户自己定义activity,使用的命令包括set_case_analysis, create_clock, infer_switching_activity and set_switching_activity。

report switching activity

另一个重要内容是report switching activity。在读入saif或者vcd文件,或者set_switching_activity之后,使用report_switching_activity就能够报告switching activity的各项活动。可以使用-list_not_annotated可以列出没有被反标的对象。

使用下面的属性还可以得到TR和SP的值:

toggle_count/toggle_rate/glitch_rate/static_probability

注意,在此之前,首先要update_power。

还有一些选项,如report_switching_activity -average_activity -hierarchy

还有一个命令为get_switching_activity,使用activity_source属性,可以定义activity information的来源,包括file, set_switching_activity, set_case_analysis, propagated, implied, default, or UNINITIALIZED等。可以得到TR,SP和glitch rate

在得到switching activity之后,使用update_power来将其反标,使用report_power来报告power的值。

使用report_annotated_power -list_annotated可以得到反标的报告列表。

Time-based power analysis

PT PX使用VCD来计算每个事件导致的功耗,SAIF格式对此不支持。

read_vcd "../sim/vcd.dump" -strip_path "tb/macinst" -when {N5},读取VCD文件中,在N5为true时候的activities。另外还有-time选项。

Handling Large Activity Files

Gate-level的VCD文件可能会非常大,尽管PT PX能够处理大于2G的VCD文件,但是还是要尽量避免产生和储存大的VCD文件。方法一是生成压缩的文件格式来减小activity file的尺寸,比如FSDB或者gzipped的VCD文件。另一种方法是直接将simulation生成的activity数据导入到PT PX,步骤如下:

1) 建立HDL的仿真环境,产生activity文件。比如,在testbench中必须包含$dumpvars或者$dumpfile来产生VCD文件。这个文件名即管道名,因此,两个工具都知道从哪里读写数据,而不需要创建大的文件

2) 定义命令或者运行脚本来调用HDL的仿真,使用-pipe_exec。比如,如果运行一个脚本执行VCS的仿真,包含vcs –R –f arguments –l log。使用下面的某一个命令来调用仿真,并直接读取VCD数据到PT PX

-pipe_exec run_vcs

-pipe_exec “vcs –R –f arguments –l log”

Average Toggle Rate=Number of Toggles on All Signals Per Interval/Number of Signals

Coverage=Number of Signals with at least one Toggle/Number of Signals

建立分布式环境,加速功耗分析

1) 建立分布式的计算环境,允许同时运行多个scenarios。使用LSF的两个machines进行分布式的peak power分析。

set_app_var power_enable_analysis true

set multi_scenario_working_directory ./work

set multi_scenario_merged_error_log ./work/error_log.txt

set_multi_scenario_license_limit -feature PrimeTime 2

set_multi_scenario_license_limit -feature PrimeTime-PX 2

set_host_options -32bit -num_processes 2 -submit_command /lsf/bin/bsub

start_hosts

2) 将仿真分割成两个模块

set test_dir .

# The common data is used by all the scenarios. Since all the scenarios must read the design data and update timing.

create_scenario -name run_0 -specific_data run_0.tcl -common_data common.tcl -common_variables {test_dir}

create_scenario -name run_1 -specific_data run_1.tcl -common_data common.tcl -common_variables {test_dir}

set_app_var power_enable_analysis true

set_app_var power_analysis_mode time_based

set_app_var search_path "."

set_app_var link_library " * link_library.db"

read_verilog mac.vg

current_design mac

link

read_sdc $test_dir/mac.sdc

set_disable_timing [get_lib_pins ssc_core_typG]

read_parasitics ../src/annotate/mac.spef.gz

#####################################################

# check, update, or report the timing

#####################################################

check_timing

update_timing

report_timing

#####################################################

# read switching activity file

#####################################################

read_vcd -strip_path tb/macinst ../sim/vcd.dump.gz

report_switching_activity -list_not_annotated

#####################################################

# check or update or report power

#####################################################

check_power

update_power

report_power -hierarchy

quit

Example 4 Script Example for Time-Based Power Analysis

#####################################################

# Set the Power Analysis Mode

#####################################################

set power_enable_analysis TRUE

set power_analysis_mode time_based

#####################################################

# link design

##############################################

set search_path "../src/hdl/gate ../src/lib/snps . "

set link_library " * core_typ.db"

read_verilog mac.vg

current_design mac

link

#####################################################

# set transition time / annotate parasitics

#####################################################

read_sdc ../src//hdl/gate/mac.sdc

set_disable_timing [get_lib_pins ssc_core_typ/*/G]

read_parasitics ../src/annotate/mac.spef.gz

#####################################################

check_timing

update_timing

report_timing

#####################################################

# read switching activity file

#####################################################

read_vcd ../sim/vcd.dump.gz -strip_path tb/macinst

#####################################################

# analyze power

#####################################################

check_power

set_power_analysis_options -waveform_format out -waveform_output vcd

update_power

report_power

quit