FLOORPLAN:

-

做好floorplan要掌握哪些知识技能

-

遇到floorplan问题,大致的debug步骤和方法有哪些

-

如何衡量floorplan的QA

以上是驴神提的五大点问题。鄙人狠狠地反驳了驴神的提问。后端实现工作是一个不可分割的整体,最终能收获什么样的果实,在你种下种子的那一刹那就已经注定了;至于中间的浇水施肥打药,那都是按部就班的工作了。整个后端过程就是一个混沌过程,floorplan是输入,gds和netlist是输出,中间是一团笼罩着混沌过程的迷雾。但是作为一个后端熟手、老司机,理应做到眼中有码心中无码,当你完成你的floorplan的时候,中间的迷雾在心中自动消散,最后能得到什么样的结果大致就有数了。

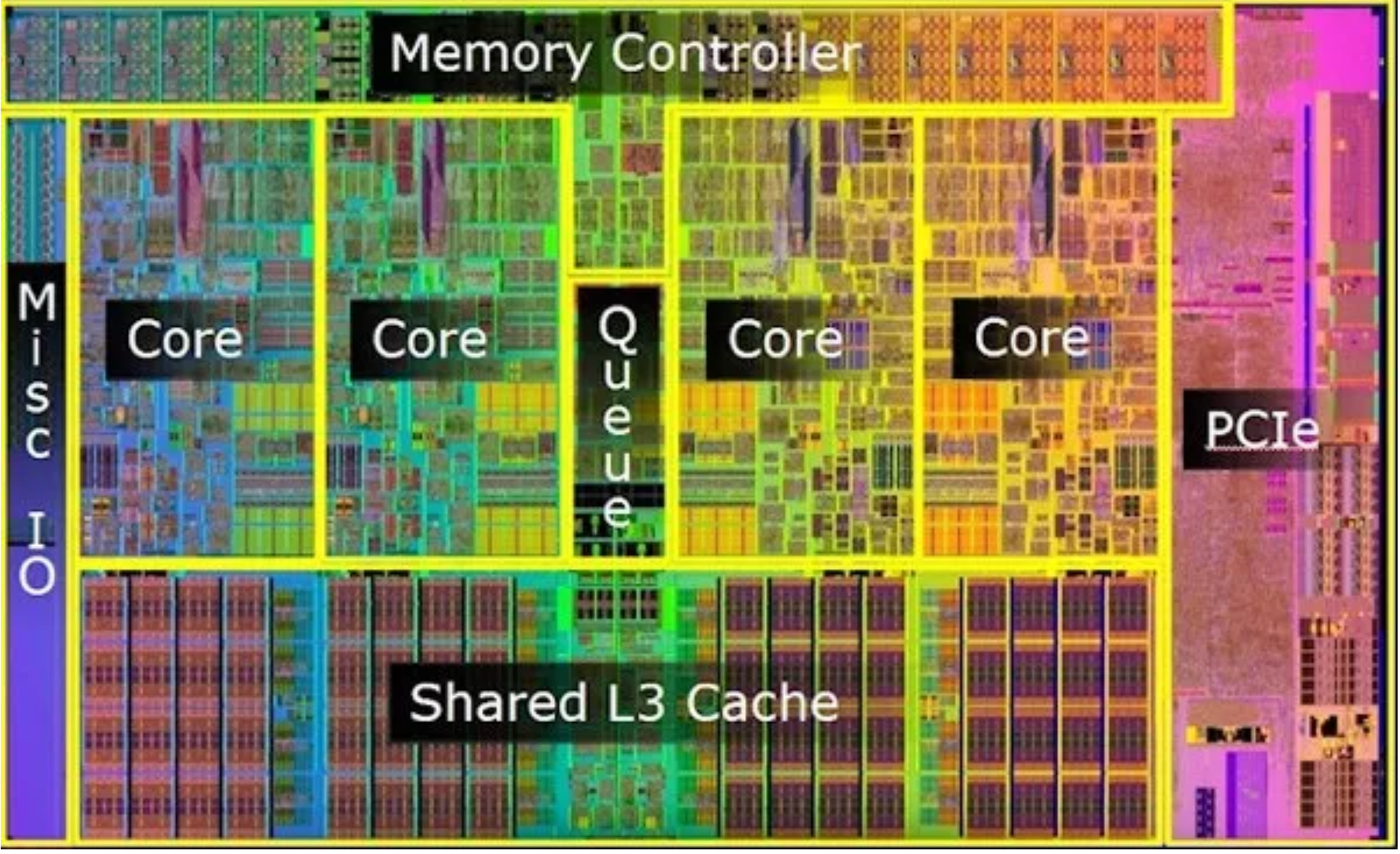

言归正传,floorplan作为后端工作的起始点,是后段工作最关键的节点;floorplan的质量,直接决定了这个design的上限。那么floorplan要做哪些事情呢?除了画个框框,摆摆memory,画画powermesh,还有规划placement blockage (hard/soft/partial), route guide (by layer/by percentage), cell guide (region/fence), 加physicalcell, 做一些preplace等等。做floorplan, 首先需要有良好的艺术鉴赏眼光!一个好的floorplan,一定是一个美的floorplan!只有每一个细节都显示出美感的floorplan,才会是一个好的floorplan!

当我们从头开始做一个floorplan的时候,一定要意识到,floorplan直接决定了placement的质量,决定了route的质量;io的位置、memory的位置、cellguide这些,都是种子,是给EDA工具的种子,基于这些种子,工具才能做出一个placement结果;同样,当placement 确定的时候,route 的结果也基本决定了。所以在做floorplan 的时候,一个合格的工程师应该要掌握设计的数据流向,和工艺的基本特性。那么floorplan的一些重要步骤应该注意哪些事项呢,简单的说:

-

IO/IP的规划。首先要熟读IO/IP的application note,掌握各个IP/IO的使用方法,有没有特殊的绕线需求,有没有特殊的place需求;对于顶层design,要了解IO的power domain对各种特殊cell的要求;对于blocklevel,如果需要自行决定io pin的位置,那么可以通过innovus的editPin功能很轻易的完成设置;

-

Memory位置的摆放。Memory 的摆放严重影响到 placement 和 routing 的质量。首先应该根据设计的数据流对 memory 位置进行粗调,然后应该根据 routing 的估算和drc的要求来进行微调。Memory 的位置对齐,出pin的方向,以及 channel 的宽度都是需要精细计算的;因此熟练使用 innovus 的floorplan toolbar的相关功能可以极大的提高我们做floorplan的效率;

-

Placement blockage的设置。根据设计工艺的特点,DRC的要求,在memory/IP/power domain周围盖上hard placement blockage是常见做法;在channel里面根据timing的需求和绕线资源的计算,往往也要加上soft 或者 partial blockage;

-

Cell guide的设置。根据设计的数据流,我们有时候会希望约束一些module摆放到特定的位置;innovus提供了三种不同的约束: guide/region/fence, 来满足不同的需求。Guide的使用往往需要对design特别了解,并且经过很多尝试和分析才能得到较好的结果;

-

Power mesh的规划。记住一个原则:永远优先选用细而密的 power mesh 而不是粗而稀的 power mesh;

-

在完成floorplan之后,先用innovus检查一遍是否有违规的地方;

-

要对floorplan质量进行评估,最好的办法就是直接跑一遍place+route。

如果floorplan没有问题,就可以正式进入到APR阶段。EDA工具发展到现在这个阶段,后端工程师的方法学也在不断更新。传统的后端方法里面,place/cts/route 泾渭分明,丁是丁卯是卯;但是在innovus最新的early clock flow里面,place阶段就把cts/route统统尝试了一遍;而useful skew的使用,和innovus cts engine的进化,使得user几乎不再需要去debug clock tree structure,不再需要设置一大堆ignorepin/floating pin/exclude pin/stop pin之类(工程师要失业了!?);传统地看clock tree skew的评价标准,在今天基于useful skew的工具方法学下面也不再适用了。因此,正如前文所述,place/cts/route 从来没有像今天这样紧密的结合在一起,形成一个密不可分的整体。

通过innovus的early clock flow+useful skew的使用,我们能比以前达到更高的frequency,而整个设计方法也变得更加简单。那么在这么智能化的工具面前,我们工程师还可以做些什么来帮助提高设计质量呢?

-

适当的cell guide。如前文所述,适当的cell guide相当于种下了一颗优质的种子,使得最后能结出丰硕的果实;

-

适当的path group。尽管innovus通常不需要设置很多path group,但是对于少数critical path,适当的path group 设置也是有益处的;

-

适当的over constraint。因为earlyclock flow的使用,工具在 placement 阶段就能看得前所未有的清晰;因此一个适当的over constraint能帮助工具取得一个最好的QoR,过犹不及。

那么既然现在工具这么智能,QoR这么好,是不是我们工程师就可以把流程脚本往服务器一丢,然后等着看 post route 结果就行啦呢?No!永远不要停止对中间结果的检查:

-

不停追踪log file,有没有什么异常发生;

-

检查每一步的结果,包括但不限于:run time, timing, route over flow / violations, drv vioaltions, clock tree latency, derate / uncertainty setting, crosstalk delay.