一、实验目的

(1)进一步熟悉Quartus II软件和GW48-PK2S实验系统的使用方法;

(2)用状态机实现序列检测器的设计,了解一般状态机的设计与应用

二、实验内容

1. 基本命题

利用Quartus II实现一个8位的序列检测器设计;给出仿真波形。最后进行引脚锁定并进行测试,硬件验证设计电路对给定序列的检测功能。

2. 扩展命题

在上述设计基础上,通过修改设计,实现以最简便的预置方法,获得n位序列检测器的功能。

三、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

四、实验

1. 基本命题

① 总体设计

设计两个进程。

进程Com1:实现序列的检测

进程Com2:实现检测结果的输出

② 程序设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT(DIN, CLK, CLR :INSTD_LOGIC;--串行输入数据位/工作时钟/复位信号

AB :OUTSTD_LOGIC_VECTOR(3DOWNTO0));--检测结果输出

END SCHK;

ARCHITECTURE behav OF SCHK IS

SIGNAL Q :INTEGERRANGE0TO8;

SIGNAL D :STD_LOGIC_VECTOR(7DOWNTO0); --8位待检测预置数

BEGIN

D <="11100101" ;--8位待检测预置数:密码:E5H

Com1:PROCESS( CLK, CLR )

BEGIN

IF CLR = '1' THEN Q <=0;

ELSIF CLK'EVENTAND CLK='1' THEN--时钟到来时,判断并处理当前输入的位

CASE Q IS

WHEN0=> IF DIN = D(7)THEN Q <=1;ELSE Q <=0;ENDIF;

WHEN1=> IF DIN = D(6)THEN Q <=2;ELSE Q <=0;ENDIF;

WHEN2=> IF DIN = D(5)THEN Q <=3;ELSE Q <=0;ENDIF;

WHEN3=> IF DIN = D(4)THEN Q <=4;ELSE Q <=0;ENDIF;

WHEN4=> IF DIN = D(3)THEN Q <=5;ELSE Q <=0;ENDIF;

WHEN5=> IF DIN = D(2)THEN Q <=6;ELSE Q <=0;ENDIF;

WHEN6=> IF DIN = D(1)THEN Q <=7;ELSE Q <=0;ENDIF;

WHEN7=> IF DIN = D(0)THEN Q <=8;ELSE Q <=0;ENDIF;

WHENOTHERS=> Q <=0;

ENDCASE;

ENDIF;

ENDPROCESS;

Com2:PROCESS( Q ) --检测结果判断输出

BEGIN

IF Q =8 THEN AB <="0001"; --序列数检测正确,输出 "1"

ELSE AB <="0011"; --序列数检测错误,输出 "3"

ENDIF;

ENDPROCESS;

END behav ;

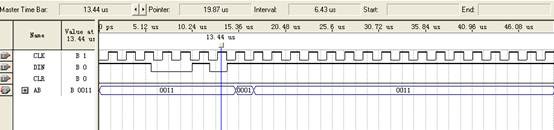

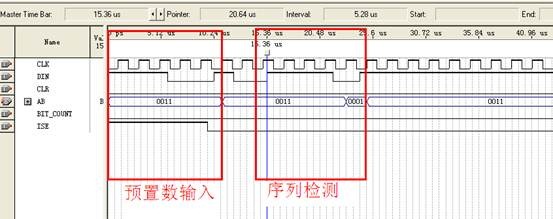

③ 仿真分析

图6-1 仿真波形图

仿真预测:当输入的结果是预置序列的时候,输出0001;反之,输出0011。

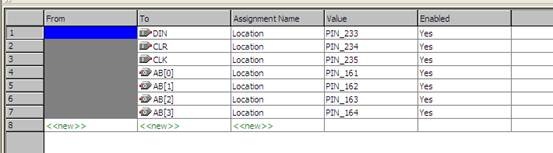

④ 硬件测试

表1-1 SCHK在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

输入引脚D |

DIN |

按键1 |

PIO1 |

233 |

模式No.5

|

|

清零端 |

CLR |

按键2 |

PIO2 |

234 |

|

|

主频率 |

CLK |

按键3 |

PIO3 |

235 |

|

|

4位数字量输出引脚 |

AB |

数码管7 |

PIO40~47 |

161-164 |

图6-2引脚的配置

2. 扩展命题

① 总体设计

本命题通过改写case判断语句,将要检测的序列和序列的位数关联,通过IF语句对状态进行判断。

② 程序设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT(DIN, CLK, CLR ,BIT_COUNT :INSTD_LOGIC;--串行输入数据位/工作时钟/复位信号/要检测的位数标识码

AB :OUTSTD_LOGIC_VECTOR(3DOWNTO0));--检测结果输出

END SCHK;

ARCHITECTURE behav OF SCHK IS

SIGNAL Q :INTEGERRANGE0TO8;

SIGNAL D :STD_LOGIC_VECTOR(7DOWNTO0); --8位待检测预置数

SIGNAL Count:INTEGERRANGE0TO8; --要检测的位数(最多支持8位)

BEGIN

D <="11100000" ;--8位待检测预置数:--11100000

Com1:PROCESS( CLK, CLR )

BEGIN

IF BIT_COUNT='0' THEN Count<=3;--判断要检测多少位

ELSE Count<=4;ENDIF;

IF CLR = '1' THEN Q <=0;

ELSIF CLK'EVENTAND CLK='1' THEN--时钟到来时,判断并处理当前输入的位

if Q=(Count+1)THEN Q<=0;ENDIF;--开始新的一轮的检测

if(DIN = D(7-Q))THEN Q<=Q+1;ELSE Q<=0;ENDIF;--进行状态的检测

ENDIF;

ENDPROCESS;

Com2:PROCESS( Q ) --检测结果判断输出

BEGIN

IF Q =(Count+1) THEN AB <="0001"; --序列数检测正确,输出 "1"

ELSE AB <="0011"; --序列数检测错误,输出 "3"

ENDIF;

ENDPROCESS;

END behav ;

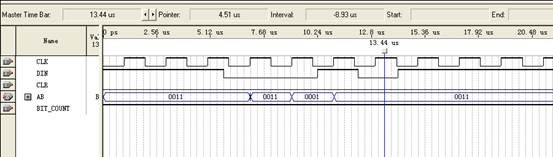

③ 仿真分析

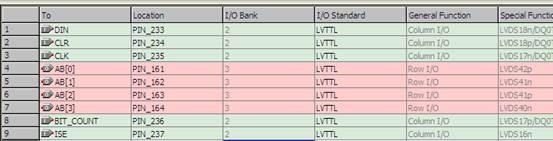

当BIT_COUNT为低电平的时候,实现4位序列检测器的功能;当BIT_COUNT为高电平的时候,实现5位序列检测器的功能。设待检测的序列为“11100000”。

图6-3 5位序列检测器波形图

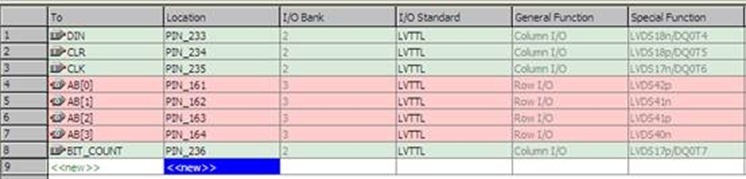

④ 硬件测试

表1-2 SCHK在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

输入引脚D |

DIN |

按键1 |

PIO1 |

233 |

模式No.5

|

|

清零端 |

CLR |

按键2 |

PIO2 |

234 |

|

|

主频率 |

CLK |

按键3 |

PIO3 |

235 |

|

|

检测位数标识 |

BIT_COUNT |

按键4 |

PIO4 |

236 |

|

|

4位数字量输出引脚 |

AB |

数码管7 |

PIO40~47 |

161-164 |

图6-4 引脚的配置

五、实验思考题

如果带检测预置数必须以右移方式进入序列检测器,那么该程序该做如何修改?

① 总体设计

同序列检测中数据右移输入的思路,但是我们这次不进行检测,收到什么就将其存入程序中的预置数变量中。我们需要额外设置一个输入变量,变量ISE用来标示是否进行预置数序列的输入,当ISE=1,输入口DIN用来输入预置数序列的;当ISE=0,输入口DIN用来输入要检测的序列。其中预置数序列的长度与BIT_COUNT相关。

② 程序设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT(DIN, CLK, CLR ,BIT_COUNT,ISE :INSTD_LOGIC;--串行输入数据位/工作时钟/复位信号/要检测的位数标识码/预置数序列的输入使能

AB :OUTSTD_LOGIC_VECTOR(3DOWNTO0));--检测结果输出

END SCHK;

ARCHITECTURE behav OF SCHK IS

SIGNAL Q :INTEGERRANGE0TO8;

SIGNAL D :STD_LOGIC_VECTOR(7DOWNTO0); --8位待检测预置数

SIGNAL Count:INTEGERRANGE0TO8; --要检测的位数(最多支持8位)

BEGIN

Com1:PROCESS( CLK, CLR )

BEGIN

IF BIT_COUNT='0' THEN Count<=3;--判断要检测多少位

ELSE Count<=4;ENDIF;

IF CLR = '1' THEN Q <=0;

ELSIF CLK'EVENTAND CLK='1' THEN--时钟到来时,判断并处理当前输入的位

if Q=(Count+1)THEN Q<=0;ENDIF;--开始新的一轮的检测

--ISE=1的时候,开始预置数序列的输入

if ISE='1' then D(7-Q)<=DIN;Q<=Q+1;

else

if(DIN = D(7-Q))THEN Q<=Q+1;ELSE Q<=0;ENDIF;--进行状态的检测

endif;

ENDIF;

ENDPROCESS;

Com2:PROCESS( Q ) --检测结果判断输出

BEGIN

IF Q =(Count+1)AND ISE='0' THEN AB <="0001"; --当序列数检测正确并且预置数使能为低电平的时候,输出 "1"

ELSE AB <="0011"; --序列数检测错误,输出 "3"

ENDIF;

ENDPROCESS;

END behav ;

③ 仿真分析

图6-5 带有预置数功能的4位序列检测器波形图

④ 硬件测试

表1-3 SCHK在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

输入引脚D |

DIN |

按键1 |

PIO1 |

233 |

模式No.5

|

|

清零端 |

CLR |

按键2 |

PIO2 |

234 |

|

|

主频率 |

CLK |

按键3 |

PIO3 |

235 |

|

|

检测位数标识 |

BIT_COUNT |

按键4 |

PIO4 |

236 |

|

|

预置数使能 |

ISE |

按键5 |

PIO5 |

237 |

|

|

4位数字量输出引脚 |

AB |

数码管7 |

PIO40~47 |

161-164 |

图6-6 引脚的配置