一、实验目的

学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

二、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

三、实验

1. 基本命题

在QuartusⅡ上设计一个含计数使能、异步复位和计数值并行预置功能的4位加法计数器,并进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

1) 实验原理

由数电知识可知,4位加法计数器由clk时钟,rst置位,en使能,cq输出,cout进位输出构成。

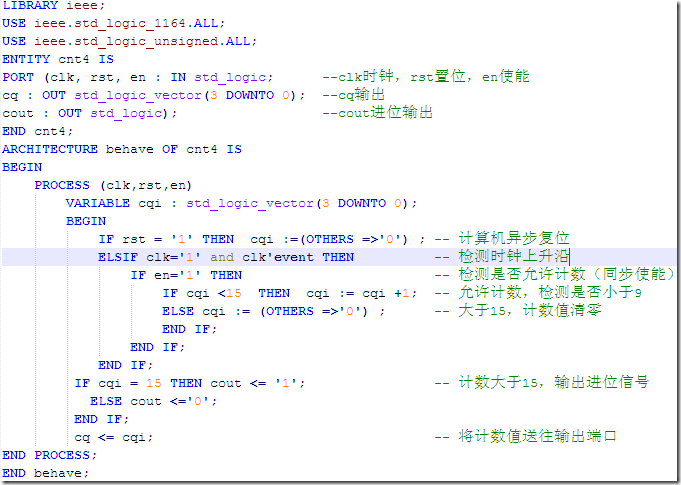

2) 程序设计

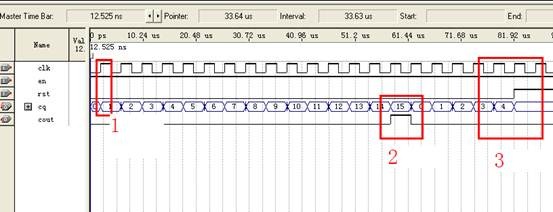

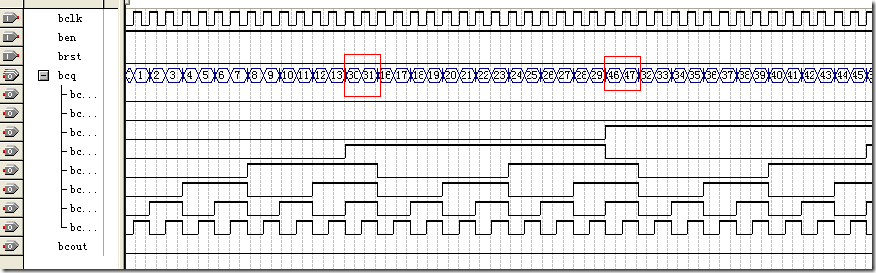

3) 编译仿真波形

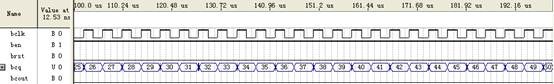

图1 4位加法计数器波形

从图1分析可知,在每一个时钟上身沿到来的时候,4位加法计数器计数值加1(图中1),最大计数值为15,并进行进位输出(图中2);当rst为高电平时,输出清零。

2. 扩展命题

在上述设计基础上,设计具有同步复位和计数值并行预置功能的8位加法计数器。并进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

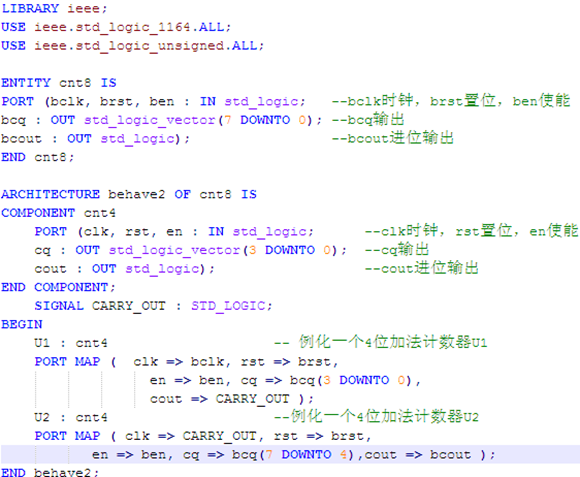

1) 实验原理

由原来的设计的两个4位加法计数器件组成一个8位加法计数器U0。设有两个4位加法计数器U1,U2。我们规定U1为U0的低位,U2为U0的高位。将U1的进位输出cout连接到U2的时钟输入clk;U1和U2的rst连接在一起作为总置位端brst;en也连接在一起,作为总使能端ben。U2的进位输出cout作为总进位输出bcout;

2) 程序设计

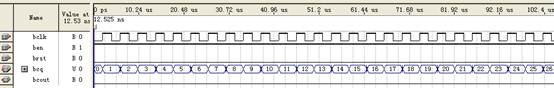

3) 编译仿真波形

图2.1 8位加法计数器从0计数到26

图2.2 8位加法计数器从26计数到50

8位加法计数器可以计数到196,但是后面的计数运行正常且与前面相似,不再截图。

4) 分析结果

从图中可以看出,实验的结果与预期相符。

四、实验设计思路

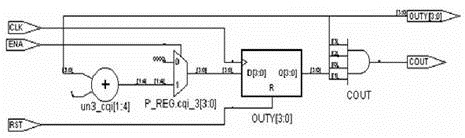

图5-1是一含计数使能、异步复位和计数值并行预置功能的4位加法计数器。如图所示,图中间是4位锁存器;rst是异步清信号,高电平有效;clk是锁存信号;D[3:0]是4位数据输入端。当ENA为‘1’时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为‘0’时将“0000”加载于锁存器。

附图5-1 4位加法计数器的RTL电路图

设计提示:

若目标器件是EP1C6Q240C8,建议选实验电路模式5,用键8(PIO7)控制RST;用键7(PIO6)控制ENA;计数溢出COUT接发光管D8(PIO15);输出Y是计数输出,接数码1(PIO19-PIO16,低位靠右);时钟CLK接clock0,通过跳线选择4Hz信号。引脚锁定后进行编译、下载和硬件测试实验。

五、实验思考题

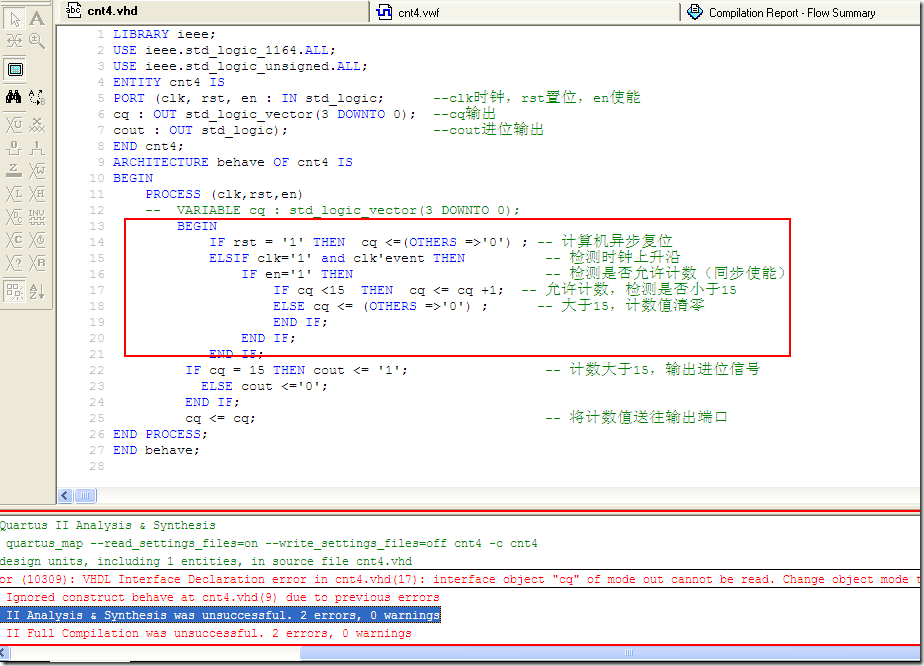

(1)是否可以不定义信号 CQI,而直接用输出端口信号完成加法运算,即: OUTY <= OUTY + 1 ? 为什么?

假设可行,将cnt4中的实验程序修改为直接使用输出端口信号完成加法运算,如图3所示。经分析,程序中的输出cq是不可读的,另外,如果没有一个变量来保存程序的计数值,那么程序就相当于一个组合逻辑电路,不具备计数的功能。

图3直接使用输出端口信号完成加法运算

六、问题的总结

1、Cnt4中的不准确的进位输出,导致cnt8中的计数出错。

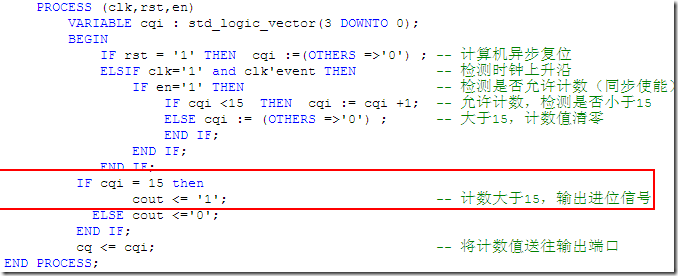

之前在cnt4判断进位的输出的语句如图3 所示。该语句检测当计数值为15的时候,就进行输出。当4位加法计数器的数量为一个的时候,可以正常工作。但是复用cnt4的时候,发现8位加法计数器cnt8的计数出现了如图4的错误。经分析,在cnt8中时,当低位cnt4的计数值为15,同时输出一个进位信号到高位cnt4,照成高位cnt4多计数了一次。由于在下一个时钟到来的时候,低位的cnt4才重新从0开始计数,因此会产生仿真结果与预期不符。只要我们将程序修改为如下方程序块1所示。

图3 进位输出语句

图3 Cnt8计数输出不准确

|

LIBRARYieee; USEieee.std_logic_1164.ALL; USEieee.std_logic_unsigned.ALL; ENTITY cnt4 IS PORT(clk, rst, en :INstd_logic; --clk时钟,rst置位,en使能 cq :OUTstd_logic_vector(3DOWNTO0);--cq输出 cout :OUTstd_logic); --cout进位输出 END cnt4; ARCHITECTURE behave OF cnt4 IS BEGIN PROCESS(clk,rst,en) VARIABLE cqi :std_logic_vector(3DOWNTO0); BEGIN IF rst = '1' THEN cqi :=(OTHERS=>'0');-- 计算机异步复位 ELSIF clk='1' and clk'eventTHEN -- 检测时钟上升沿 IF en='1' THEN -- 检测是否允许计数(同步使能) IF cqi <15 THEN cqi := cqi +1; -- 允许计数,检测是否小于15 ELSE cqi :=(OTHERS=>'0'); -- 大于15,计数值清零 ENDIF; ENDIF; ENDIF; IF cqi =15THEN IF clk='1' and clk'eventTHEN cout <= '1'; -- 计数大于15,输出进位信号 ENDIF; ELSE cout <='0'; ENDIF; cq <= cqi; -- 将计数值送往输出端口 ENDPROCESS; END behave;

|

代码块1 修改后的cnt4代码