一、实验目的

熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序逻辑电路的设计、仿真和测试方法。

二、实验

1. 基本命题

用VHDL文本设计触发器,触发器的类型可任选一种。给出程序设计、仿真分析、硬件测试及详细实验过程。

① 实验原理

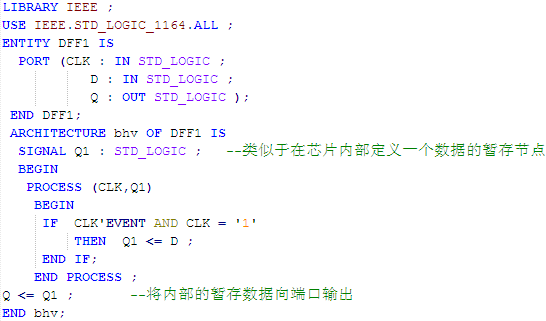

由数电知识可知,D触发器由输入的时钟信号(CLK)、数据输入口(D)和数据输出(Q)构成。本程序通过进程监视CLK和D,当CLK为上升沿的时候,将D赋值给Q,要完成这个赋值操作,必须再借助一个信号S来进行值的传递。

② 程序设计

③ 仿真分析

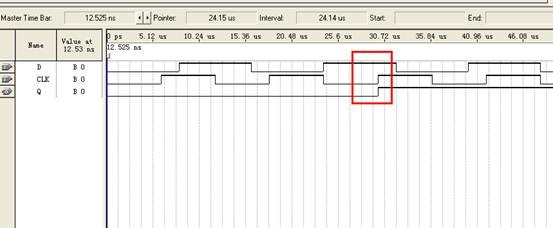

仿真预测:输入一组波形,当且仅当CLK为上升沿的时候,Q输出D的值;否则,Q保持原值不变。

图1 D触发器仿真波形图

结论:仿真的结果与仿真预测一致。

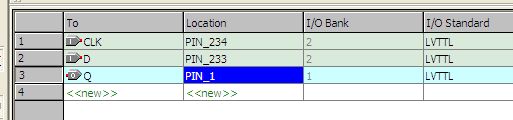

④ 硬件测试

我们通过将输出Q设为为灯泡(D1),按键1为D,按键2为CLK。

表2-1 D触发器在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

输入D |

D |

键1 |

PIO0 |

233 |

模式No.5 |

|

CLK |

CLK |

键2 |

PIO1 |

234 |

|

|

输出Q |

Q |

D1 |

P108 |

1 |

如表2-1所示完成元件D触发器与实验板引脚的绑定。如图2所示

图2 D触发器与实验板引脚的绑定

2. 扩展命题

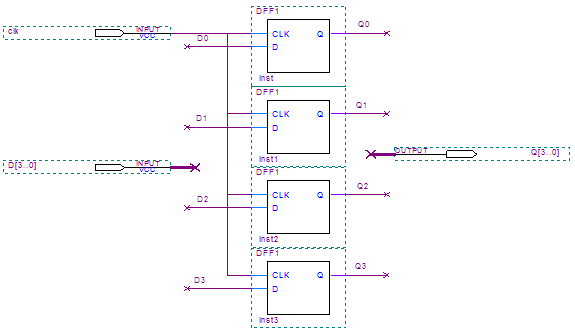

将设计的触发器看成是一个元件,利用元件例化语句设计如图4-1所示4D透明锁存器。给出程序设计、仿真分析、硬件测试及详细实验过程。

图3 4D透明锁存器

① 实验原理

依据图3 ,我们将所有触发器的时钟输入端接入同一个时钟,将第一个触发器的输入端接入D0输入,第一个触发器输出Q0接入Q0。其他的D触发器按照第一个触发器的接法,按输入、输出口下标的递增顺序与对应的输入、输出总线相连。根据锁存器的特性,在程序设计中,我们通过监视CLK的电平,当CLK为高电平时,将输入原样输出;否则保持输出状态。

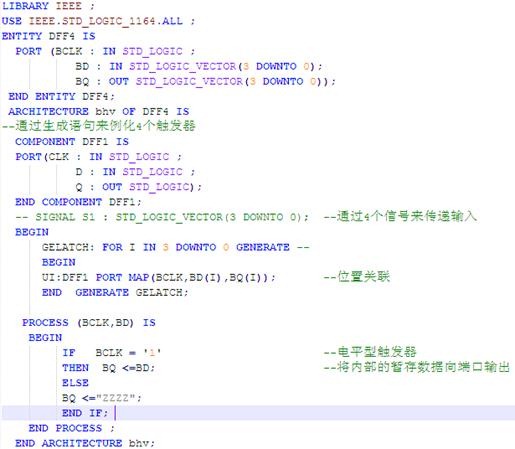

② 程序设计

③ 仿真分析

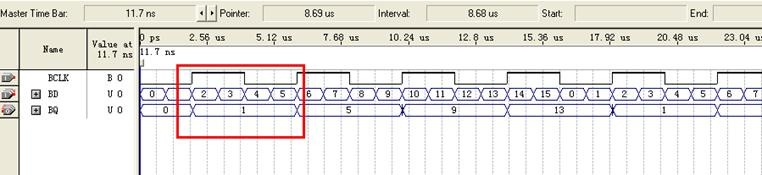

仿真预测:输入一组波形,当且仅当BCLK为高电平的时候,BQ输出BD的值;否则,BQ输出高阻态。

图4 4D透明锁存器仿真波形图

实验原理:为了让实验的效果明显,我们取的BCLK周期为BD的两倍。

结论:仿真的结果与仿真预测一致。

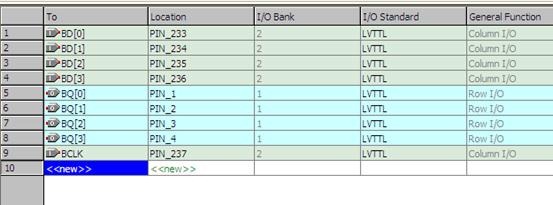

④ 硬件测试

我们通过将BD(1)、BD(2)、BD(3)、BD(4)设为按键1、2、3、4,D1,D2,D3,D4为BQ(1)、BQ(2)、BQ(3)、BQ(4),CLK设置为按键5。

表2-2 4D透明锁存器在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

输入D |

BD |

键1,2,3,4, |

PIO0,PIO1,PIO2,PIO3 |

233,234,235,236 |

模式No.5 |

|

CLK |

BCLK |

键5 |

PIO4 |

237 |

|

|

输出Q |

BQ |

D1 |

P108,P109,P110,P111 |

1,2,3,4 |

如表1-1所示完成元件4D透明锁存器与实验板引脚的绑定。如图5所示

图5 4D透明锁存器与实验板引脚的绑定