在很多情况下,需要使用双向IO。不过最好谨慎使用,在top层使用。网上很多描述的代码甚至是不可以综合并且有语法错误的,还是老实自己写个模块吧。

新版本如下:

使用inout口,直接定义个inout口。

然后用使能控制就好了,如果是作为输入,则直接把inout赋值给reg型变量就行。

如果作为输出,则使用使能控制,输出则把寄存器的值赋给inout,不输出则赋值z。表示输出高阻态,处于输入模式中。

inout io_sdio;//定义一个inout r_sdi_shift<={r_sdi_shift[6:0],io_sdio}; //采集数据 assign io_sdio = r_oe_n ? 1'bz : r_sdo_shift[23] & (~o_csn); //输出

三行代码解决一切问题。

老版本不再使用,如下:

如果你需要一个口既做输入端口也做输出端口,那么你就需要去描述一个双向的IO。

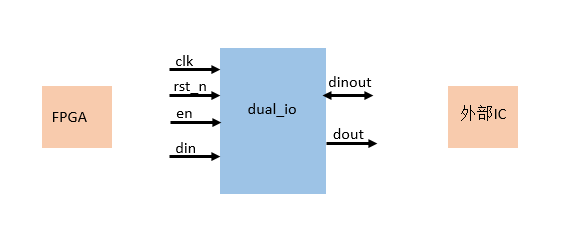

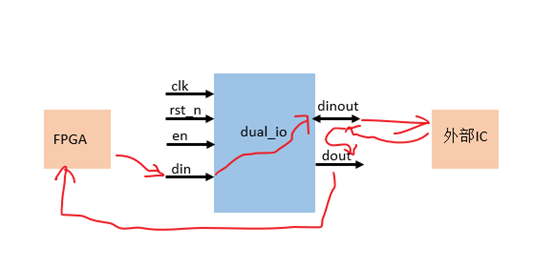

1.电路框图:

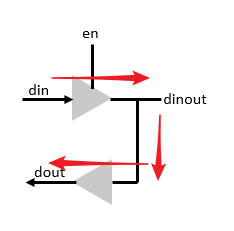

2.数据流向:

当en=0的时候,三态门选通,dinout当输出口使用,数据从din到dinout。

当en=1的时候,三态门关闭,dinout当输入口使用,输出呈现高阻态,数据从dinout到dout。

3.代码:

//************************************************ // Filename : dual_io.v // Author : kingstacker // Company : School // Email : kingstacker_work@163.com // Device : Altera cyclone4 ep4ce6f17c8 // Description : dual io,wwidth can be change; //************************************************ module dual_io #(parameter WIDTH = 8)( /*i*/ input wire clk , input wire rst_n , input wire en , input wire [WIDTH-1:0] din , inout wire [WIDTH-1:0] dinout , /*o*/ output wire [WIDTH-1:0] dout ); reg [WIDTH-1:0] din_reg; reg [WIDTH-1:0] dout_reg; always @(posedge clk or negedge rst_n) begin if (~rst_n) begin din_reg <= 0; dout_reg <= 0; end //if else begin if (~en) begin din_reg <= din; end else begin dout_reg <= dinout; end end //else end //always assign dinout = (~en) ? din_reg : 8'hzz; assign dout = dout_reg; endmodule

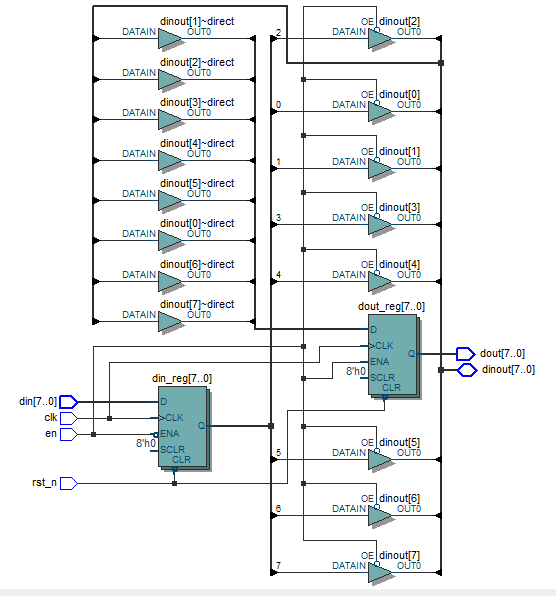

4.综合一下看看:三态门实现双端口。

以上。