什么叫时序?

时间与动作的相互关系,什么时间干什么活。

同步时序:单一时钟源,所有寄存器在单一时钟源下同步工作。

异步时序:多个时钟源,除使用带时钟的触发器之外,还可以使用不带时钟的触发器与延时元件作为存储元件。

组合逻辑:任意时刻的输出仅仅取决于该时刻的输入。

时序逻辑:任意时刻的输出不仅取决于当前时刻的输入信号还取决于电路原来的状态。

时序分析有哪两种?优缺点?

动态时序仿真与静态时序分析。

动态时序仿真:施加激励产生输出,主要验证功能的正确性。但随着电路规模的增长,验证所需要的时间也越来越长。用户难以提供完备的激励文件,在分析中可能会遗漏一些关键路径。

静态时序分析:采用穷举分析法提取整个设计所有的时序路径,通过计算信号在路径上的传播延时来计算设计的各项时序性能指标。仅仅聚焦于时序性能的分析,并不涉及设计的逻辑功能。速度快,设计约束覆盖面广。但目前只能分析同步时序电路,对异步电路的分析还不够成熟。

什么叫建立时间?保持时间?

建立时间:时钟有效沿到来之前,数据需要保持稳定的时间。

保持时间:时钟有效沿到来之后,数据还需要维持不变的时间。

两者在时钟有效沿前后定义了一个时间窗,窗口内数据不能发生改变,否则时序违例。

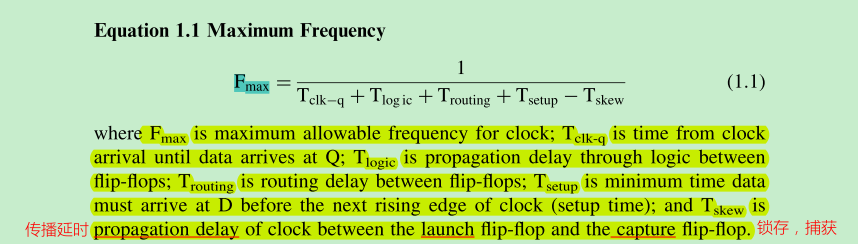

总结如图:

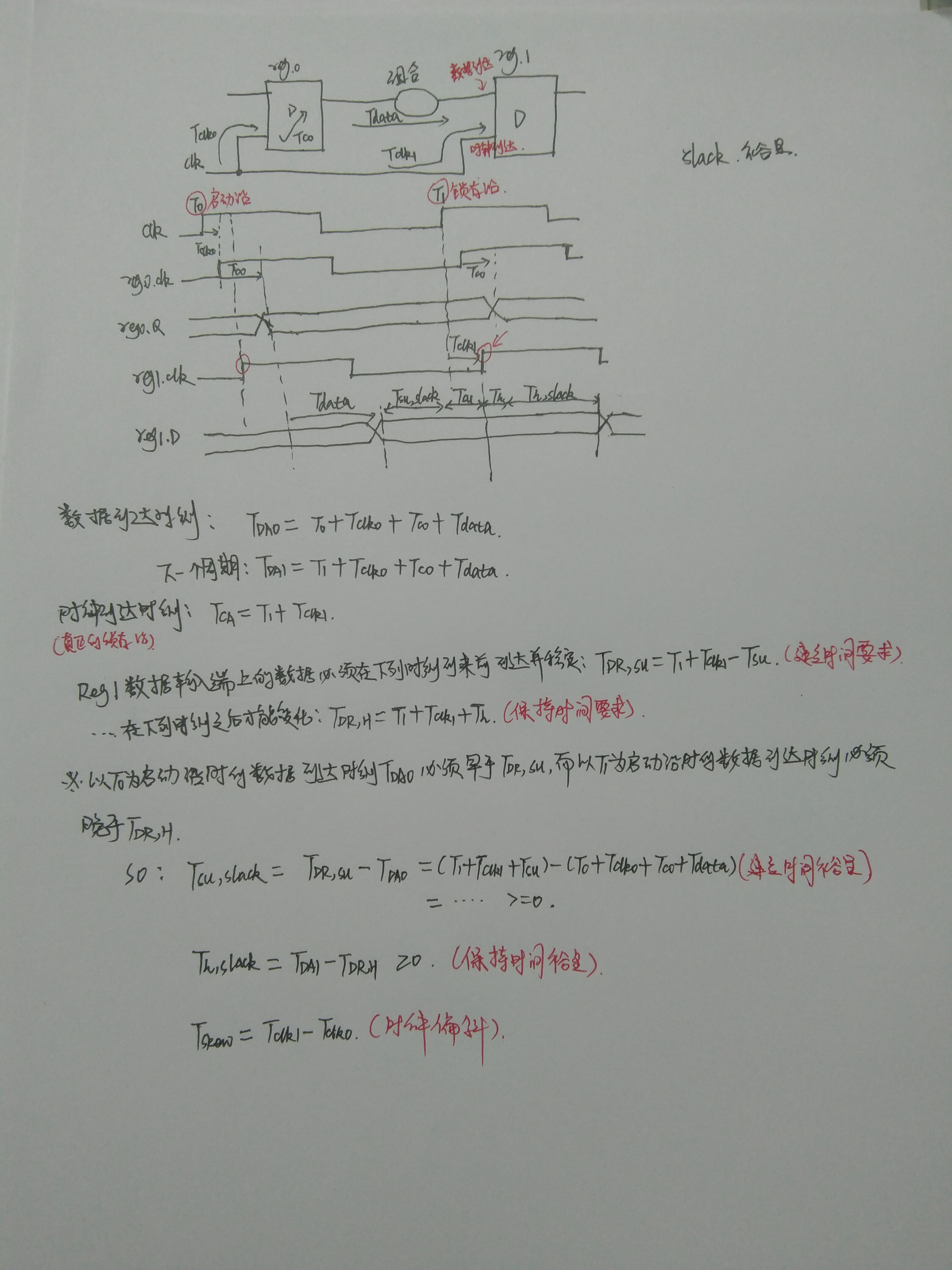

同步路径分析:

Tco:触发器固有属性,时钟有效沿后数据从D到Q的延时。

Tclk0:寄存器0的时延。

Tdata:两个寄存器节点之间的延时,包括组合延时和布线延时。

Tclk1:寄存器1的时延。

系统Fmax的定义:电路最高能跑多快,超过这个Fmax电路会跑崩。要提升Fmax,主要降低Tdata。其他Tco,Tsu固有属性无法改变。

异步路径分析:

待续。。。。

以上。