分析几个芯片的控制接口,为下一步写verilog代码做准备。

首先,受限于adc的work频率最大27mhz,整个控制模块的平台 clk=20mhz,50ns。

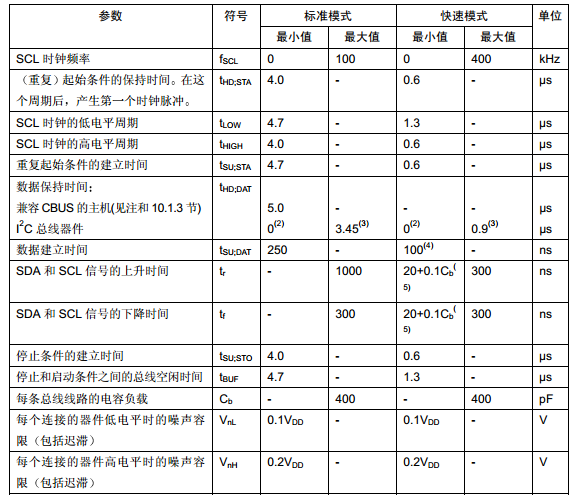

供电芯片 4个共用一个spi接口,通过/sync[4:1]来区分,相当于片选信号

时序分析:

t1=20ns(min)@3.3V,sclk的速率最大达到50MHz;

t4=10ns(min),/sync=low理论上可以和sclk的rising一起动作;在rising送数据/移位,芯片在falling采样sdi,从bit28到bit0;

t6=5ns(min),t5=150ns(min);t7=5ns(min);t8=7ns(min);/sync=high需要等一拍;

t9=75ns(max),t10=1.65us(1DACx1)2.3us(2DACx1)2.95us(3DACx1)3.6us(4DACx1)270ns(other)

检测/busy=low的状态,抓到/busy=high后释放。

操作指导:

一般情况,每个指令下发后,都需要等待busy时间才能释放,接着bram才能读取下个指令。t10是us级的。

建议,每次都先读busy状态,然后再发指令。这样指令生效的busy时间跟bram读下条指令的时间重叠,节省时间。

下发一串指令29*50ns*2=3us,读一次bram参数5*50ns*2=0.5us,接近busy最大的3.6us,很合理。

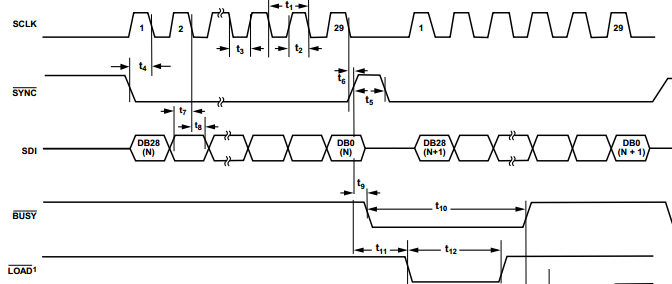

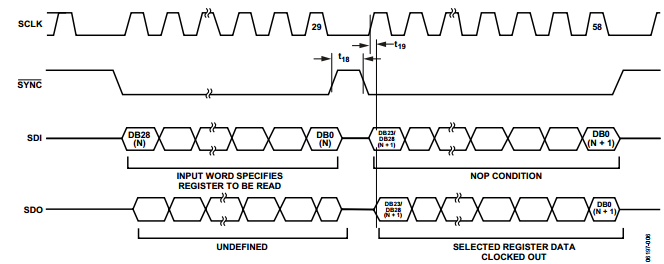

ADC采样芯片:采用read-only的spi接口

时序分析:

tCLK=37ns(min),最大工作时钟27MHz,外部用了一个20Mhz的有源晶振;最好让fCLK/fSCLK成倍数关系,取10Mhz;

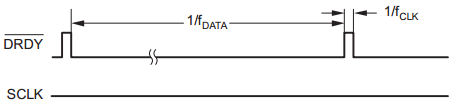

抓/DRDY-falling,第一个bit先输出MSB,然后在SCLK的falling沿,其他23个bit再依次输出,所以user应该在sclk的rising沿sample数据;

那么数据采样过程应该是,/DRDY下降沿,采样MSB@SCLK-rising,然后发falling让ADC出数据,接着在rising采样。

转换周期tCONV,在high-speed模式下典型值是256个clk周期(20mhz下就是12.8us)(25mhz的clk下需要10.24us)

其中读取数据的时间是24个bit的时间是24*50ns*2(只占用其中的2.4us)。在连续指令下可以不遗漏地抓取每次更新值。

一定要抓取/DRDY的falling,而不是低电平。如果采样的是靠后的low,有很大概率抓到正在刷新的数据,采样到错误数据。

所以等采样命令下达后,再抓DRDY下降沿发出sclk的话,最大的间隔是1个CONV周期,12.8us;(推荐)(conv决定了采样刷新率)

如果每次DRDY都默认存数据,采样指令到达直接拿数据,每次的时间间隔还是1个CONV周期,而且sclk一直在工作,且需要刷新标志,不推荐这种方式;

DRDY空跑的高脉宽是一个clk周期,采样该高电平是否有问题?

从空闲态抓取falling确实只有一个clk间隙,一旦开始采data,高电平将会占大多数的conv时间。

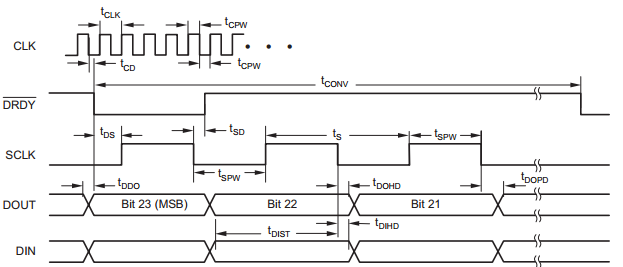

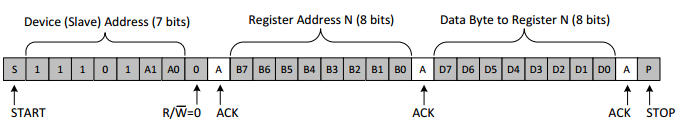

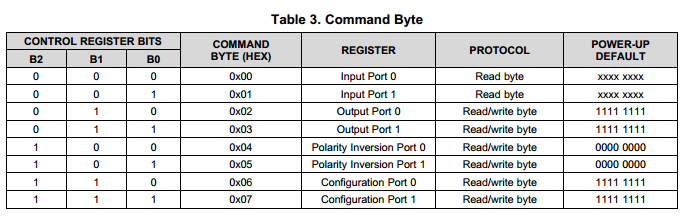

IIC扩展IO:

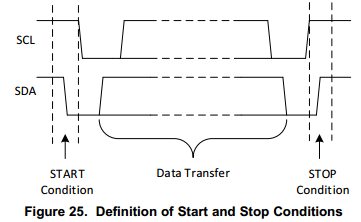

采用IIC的fast-mode-400khz,scl的高电平0.6us-min,低电平1.3us-min;

start/stop的建立保持时间也是0.6us-min;所以最小逻辑节拍是0.6us;

sda数据在scl高电平期间要保持稳定,sda数据在scl-rising出现前100ns就要建立,保持到scl-falling处即可;

可以按照L0.6us-H0.6us-L0.6us来分配节拍;

数字电位器:

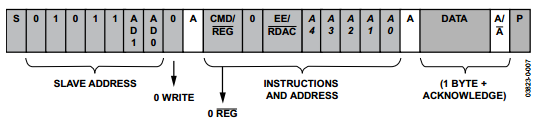

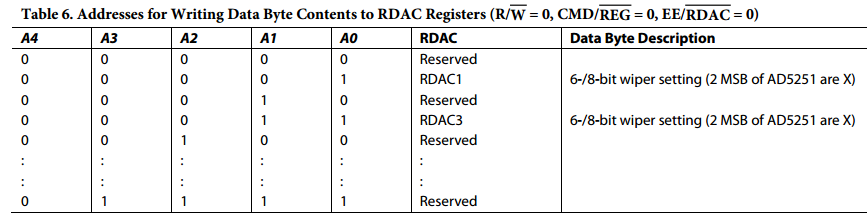

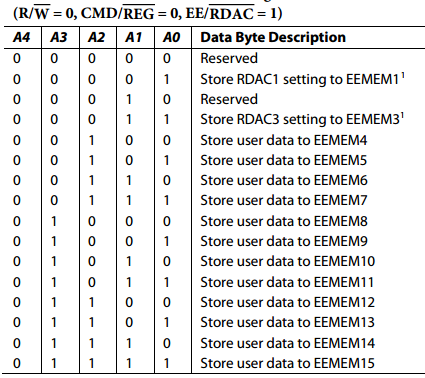

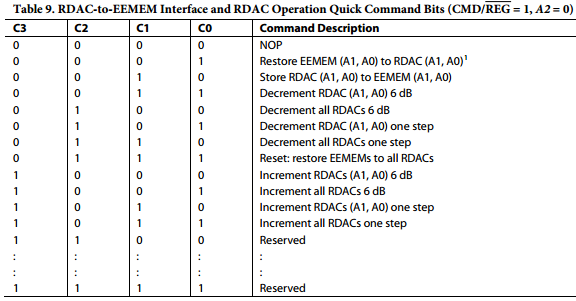

注意区分 CMD与REG EE与RDAC。REG=0,先调整RDAC,调整完毕写EE。

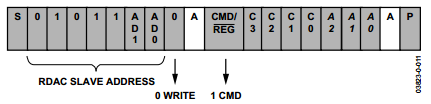

Quick Command的模式跟上面不一致,暂时不使用。

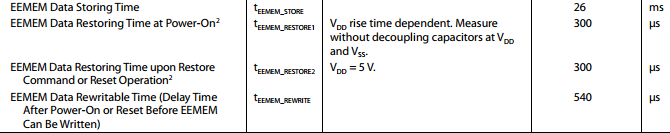

附上IIC总线规范之AC特性