- 最早的时候发现读取bram的addr必须+4而不是+1。

主要就在是否勾选“Byte Write Enable”,即是否按字节来操作。

在BRAM Controller模式下,默认勾选,PortA和PortB都是32bit位宽的,按照字节就是4个byte,所以会有we[3:0]共4个we信号。

在Stand Alone模式下,默认是不勾选的;如果选择了“Generate address interface with 32 bits”,这个enable就再次被默认勾选。

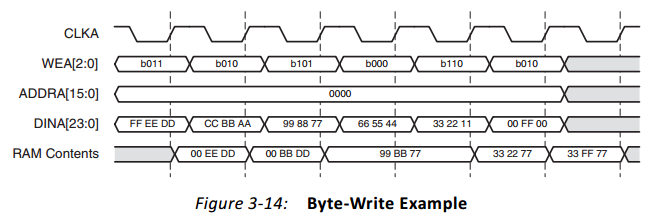

Byte-Writes

按照bytes操作数据,比如32bit位宽,是4个byte,对应4个we信号。比如使能we[3:0]=4'b0010,那么只有第二byte会被写入数据,其他位不变。

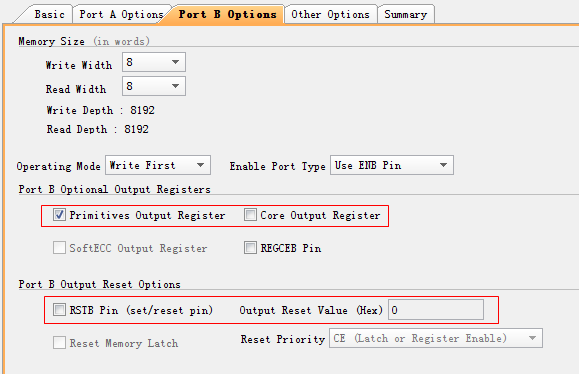

Optional Output Registers

这种output reg的作用就是改善输出路线上的delay和latency。

primitive output register:原语之后的reg就是用ram做的,所以默认就有配置。

core output register:需要单独勾选。

如果都没选,在原语上也会有个latch,在原语reg之前。

Optional Pipeline Stages

如上图,当用户bram是由多个bram拼凑的,在输出口就会有MUX负责处理共用。但这样的组合结构对数据不好,所以也在会前面加几级pipeline来优化结构。

只有当core output register被勾选的时候,才能选择这个属性。

但是这些reg属性都会增加input与output之间的节拍。erg1即primitive,reg2和3是pipeline,dout是core output reg。

如果primitive和core以及pipeline的reg都没有的话,din和dout之间只相差一个节拍。

Optional Set/Reset Pins

rst信号控制最后一个output reg,结合上面的reg设置。

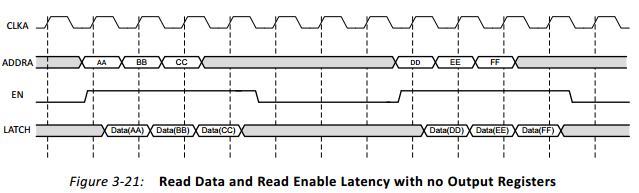

Memory Output Flow Control

把en、rst、regce结合起来,可以控制不同的输出方式。

The LATCH signal is the data at the output of the primitive

REG1 is the data at the output of the primitive output register