什么是时钟?SOC为什么需要时钟?

- 时钟是同步工作系统的同步节拍。

- SOC内部有很多器件,譬如CPU、串口、DRAM控制器,GPIO等内部外设,这些东西要彼此协调工作,需要一个同步的时钟系统来指挥。

时钟的获得?

SOC时钟获得一般有:

- 外部直接输入时钟信号,SOC有一个引脚用来输入外部时钟信号,用的很少

- 外部晶振+内部时钟发生器产生时钟,大部分低频单片机这么工作

- 外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频得到各种频率的时钟

s5pv210属于第3种,为什么这么设计?

- 第一问:为什么不用外部高频晶振产生高频率信号直接给cpu?

主要是因为芯片外部电路不适宜使用高频率,因为传到辐射比较难控制:高频率的晶振太贵了。

- 第二问:为什么要内部先高频,然后再分频?

主要因为SOC内部有很多部件都需要时钟,而且各自需要的时钟频率不同,没法统一供应,因此设计思路是PLL后先得到一个最高的频率(1GHZ、1.2GHZ),然后各个外设都有自己的分频器再分频得到自己想要的频率。

时钟和系统性能之间的关系,超频,稳定性

- 一般SoC时钟频率都是可以认为编程控制的频率的高低对系统性能有很大的影响

- s5pv210建议工作频率800MHZ~1.2GHZ,我们一般设置为1GHZ主频。如果你设置到1.2GHZ就叫超频。超频的时候系统性能会提升,但是发热也会增大,因此会影响系统稳定性。

时钟与外设编程的关系?

- 每个外设工作都需要一定频率的时钟,这些时钟都是由手中系统提供的,时钟系统可以编程控制工作模式,因此,我们程序员可以为每个外设指定时钟来源,时钟分频系数,从而指定外外设的工作时钟。

时钟与功耗控制之间的关系?

- SoC中各种设备工作中,时钟频率越高,功耗越大,越容易不稳定,需要的外部的散热条件也越苛刻。

- SoC内部有很多外设,这些外设不用的时候最好关掉(不关掉会一定程度的浪费电),开关外设不是通过开关,而是通过时钟,也就是说,我们给某个外设断掉时钟,这个外设就关掉了。

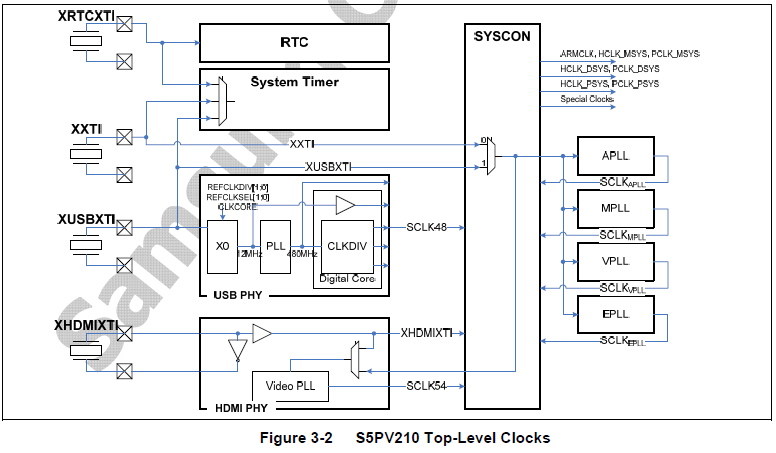

s5pv210时钟系统详解

时钟域:MSYS、DSYS、PSYS

由于210内部的各个模块的彼此工作时钟速率差异太大,所以有必要按照高速和低俗进行分类

因为s5pv210的时钟系统比较复杂,内部外设太多,因此把整个内部的时钟划分为3大块,叫做3个域

- MSYS:CPU(Cortex-A8内核)、DRAM控制器(DMC0、DMC1)、IROM&IRAM........

- DSYS:都是和视频显示编解码有关的模块

- PSYS:和各种内部外设的时钟有关,譬如串口、I2C、AC97、PWM、USB等

时钟来源

s5pv210外部有四个晶振接口,我们设计板子硬件时,可以根据需要决定在哪里接晶振。接了晶振之后上电相应的模块就能产生震荡,产生原始时钟,原始时钟经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频信号,高频信号再经过分频到达芯片内部各个模块上。(有些模块,譬如串口在内部还有进一步的分频器进行再次分频使用)

PLL:APLL、MPLL、EPLL、VPLL

- APLL:Cotex-A8内核 MSYS域

- MPLL&EPLL:DSYS PSYS

- VPLL:Video视频相关模块

MSYS域

- ARMCLK:给cpu内核工作的时钟,也就是所谓的主频

- HCLK_MSYS:MSYS域的高频时钟,给DMC0和DMC1使用

- PCLK_MSYS:MSYS域的低频时钟

- HCLK_IMEM:给iROM和iRAM(合称iMEM)使用

DSYS域

- HCLK_DSYS:DSYS域的高频时钟

- PCLK_DSYS:DSYS域的低频时钟

PSYS域

- HCLK_PSYS:PSYS域的高频时钟

- PCLK_PSYS:PSYS域的低频时钟

- SCLK_ONENAND:

总结:210内部的各个外设都是接在(内部AMBA总线)总线上面的,AMBA总线有一条高频分支叫做AHB,有一条低频分之叫APB。上面的各个域都有对应的HCLK_XXX和和PCLK_XXX,其中,HCLK_XXX就是XXX这个域的AHB总线的工作频率。PCLK_XXX就是这个域中APB总线的工作频率。

SOC内部的各个外设其实是挂在总线上工作的,也就是说这个外设的时钟来自于他挂在的总线,譬如UART就挂在PSYS域下的APB总线上,因此串口的时钟来源就是PCLK_PSYS

各时钟的典型值

- 当210刚上电时默认是外部晶振+内部时钟发生器产生的24MHz频率的时钟直接给ARMCLKS,这时系统的主频就是24MHz,运行非常慢

- iROM代码执行时,第6 步中初始化了系统时钟系统,这时给了默认推荐运行的频率。这个时钟频率是三星推荐的210工作性能和稳定性最佳的频率。

各时钟的典型值:

• freq(ARMCLK) = 1000 MHz

• freq(HCLK_MSYS) = 200 MHz

• freq(HCLK_IMEM) = 100 MHz

• freq(PCLK_MSYS) = 100 MHz

• freq(HCLK_DSYS) = 166 MHz

• freq(PCLK_DSYS) = 83 MHz

• freq(HCLK_PSYS) = 133 MHz

• freq(PCLK_PSYS) = 66 MHz

• freq(SCLK_ONENAND) = 133 MHz, 166 MHz

时钟框图讲解

时钟体系框图的位置:数据手册P361页Figure3-3

两张图之间是渐进关系。第一张图从左到右一次完成了原始时钟生成-------->PLL倍频得到高频时钟------>初次分频得到各种总线时钟:第二张图是从各中间时钟(第一张图中某个步骤生成的时钟)到各个外设自己使用的时钟(实际就是个别外设自己再额外分频的设置)。可见第一张图是理解整个时钟体系的关键,第二张图是进一步分析各外设时钟来源的关键。

- MUX开关就是或门,实际对应某个寄存器的某几位的某几个bit位的设置。设置值决定了走哪条通道,分析这个可以知道右边的时钟是从左边的哪条路过来的,进而知道右边时钟是多少。

- DIV分频器,是一个硬件设备,可以对左边的频率进行n分频,分频后的低频时钟输出到右边。分频器在编程实实际对应某个寄存器的某几个bit位, 我们可以通过设置这个寄存器的这些对应bit位来设置分频器的分频系数

- clock source x就是在设置MUX开关;

- clock divider contorl寄存器就是在设置分频器分频系数。

时钟设置的关键寄存器

- xPLL_LOCK:主要控制寄存器的锁定周期。

- xPLL_CON:主要用来打开/关闭PLL电路,设置PLL的倍频参数,查看PLL的锁定状态

- CLK_SRCn(n:1~6):用来设置时钟来源的

- CLK_SRC_MASK:用来决定MUX开关n选1后是否继续通过,默认的时钟都是打开的,好处是不会因为某个模块的时钟关闭而导致莫名其妙的问题,坏处是功耗控制不够精细。

- CLK——DIVn:各模块的分频器参数设置

- CLK_GATE_x:类似于CLK_GATE_MASK,对时钟进行开关控制。

- CLK_DIV_STATn和CLK_MUX_STATn:用来查看DIV和MUX的状态是否已经完成还是在进行中。

汇编实现时钟设置代码

- 第一步:先不使用PLL。让外部晶振24MHz直接过去。

- 第二步:设置锁定时间。默认值为0xFFF,我们可以设置为最大值0xFFFF

- 第三步:设置分频系统,决定由PLL出来的最高时钟如何分频得到各个时钟

- 第四步:设置PLL,主要是设置PLL的倍频系统,决定由输入端24MHz的原始频率可以得到更多大的输出频率。我们按照默认设置值设置输出为ARMCLOCK为1GHz

- 第五步:打开PLL。前面4步已经设置好了所有的开关和分频系数,本步骤打开PLL后PLL开始工作,锁定频率后输出然后经过分频得到各个频率。

源代码

// 时钟控制器基地址 #define ELFIN_CLOCK_POWER_BASE 0xE0100000 // 时钟相关的寄存器相对时钟控制器基地址的偏移值 #define APLL_LOCK_OFFSET 0x00 #define MPLL_LOCK_OFFSET 0x08 #define APLL_CON0_OFFSET 0x100 #define APLL_CON1_OFFSET 0x104 #define MPLL_CON_OFFSET 0x108 #define CLK_SRC0_OFFSET 0x200 #define CLK_SRC1_OFFSET 0x204 #define CLK_SRC2_OFFSET 0x208 #define CLK_SRC3_OFFSET 0x20c #define CLK_SRC4_OFFSET 0x210 #define CLK_SRC5_OFFSET 0x214 #define CLK_SRC6_OFFSET 0x218 #define CLK_SRC_MASK0_OFFSET 0x280 #define CLK_SRC_MASK1_OFFSET 0x284 #define CLK_DIV0_OFFSET 0x300 #define CLK_DIV1_OFFSET 0x304 #define CLK_DIV2_OFFSET 0x308 #define CLK_DIV3_OFFSET 0x30c #define CLK_DIV4_OFFSET 0x310 #define CLK_DIV5_OFFSET 0x314 #define CLK_DIV6_OFFSET 0x318 #define CLK_DIV7_OFFSET 0x31c #define CLK_DIV0_MASK 0x7fffffff // 这些M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。 // 这些配置值是三星推荐的,因此工作最稳定。如果是自己随便瞎拼凑出来的那就要 // 经过严格测试,才能保证一定对。 #define APLL_MDIV 0x7d // 125 #define APLL_PDIV 0x3 #define APLL_SDIV 0x1 #define MPLL_MDIV 0x29b // 667 #define MPLL_PDIV 0xc #define MPLL_SDIV 0x1 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) #define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV) #define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) .global clock_init clock_init: ldr r0, =ELFIN_CLOCK_POWER_BASE // 1 设置各种时钟开关,暂时不使用PLL ldr r1, =0x0 // 芯片手册P378 寄存器CLK_SRC:Select clock source 0 (Main) str r1, [r0, #CLK_SRC0_OFFSET] // 2 设置锁定时间,使用默认值即可 // 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间 ldr r1, =0x0000FFFF str r1, [r0, #APLL_LOCK_OFFSET] str r1, [r0, #MPLL_LOCK_OFFSET] // 3 设置分频 // 清bit[0~31] ldr r1, [r0, #CLK_DIV0_OFFSET] ldr r2, =CLK_DIV0_MASK bic r1, r1, r2 ldr r2, =0x14131440 orr r1, r1, r2 str r1, [r0, #CLK_DIV0_OFFSET] // 4 设置PLL // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz ldr r1, =APLL_VAL str r1, [r0, #APLL_CON0_OFFSET] // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz ldr r1, =MPLL_VAL str r1, [r0, #MPLL_CON_OFFSET] // 5 设置各种时钟开关,使用PLL ldr r1, [r0, #CLK_SRC0_OFFSET] ldr r2, =0x10001111 orr r1, r1, r2 str r1, [r0, #CLK_SRC0_OFFSET] mov pc, lr