前言

上一篇就已经介绍串行口通信相关概念,寄存器。对串行口通信已经有一定的了解。还介绍串行口工作方式1,这个方式所用最多,务必会用。现在来介绍工作方式0,2,3。下面来了解一下。

串行口方式0

串行口的工作方式0为移位寄存器I/O方式,可外接移位寄存器,一扩展I/O口,也可外接同步I/O设备。

发送操作:当执行一条“SBUF=A”指令时,启动发送操作,由TXD输出移位脉冲,由RXD串行SBUF中的数据。发送完8位数据后自动置TI=1.请求中断。要继续发送时,TI必须有指令清零。

接收操作:REN是串行口接收允许控制位。REN=0时禁止接收;REN=1时允许接收。当软件将REN置“1”时,即开始从RXD端口以fosc/12波特率输入数据,当接收到8位数据时,将中断标志RI置“1”。再次接收数据之前,必须用软件将RI清0。

这个方式中,RXD为数据输入输出引脚,TXD为时钟输出引脚。主要用来拓展IO口。这个方式完成时需要借用外部移位寄存器。74ls164,74ls165两个移位寄存器与串行口方式0相得益彰。下面来介绍这两个寄存器与方式0的配合。

74ls164移位寄存器

概述

74LS164是8位边沿触发式移位寄存器,串行输入数据,然后并行输出。数据通过两个输入端(DSA或DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

引脚功能

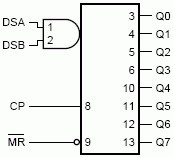

74LS164

74LS164

DSA,DSB:数据输入端

CP:时钟输入(低电平到高电平边沿触发)

MR:中央复位输入(低电平有效)

Q0~Q7:数据输出端

GND:地

VCC:正电源

真值表

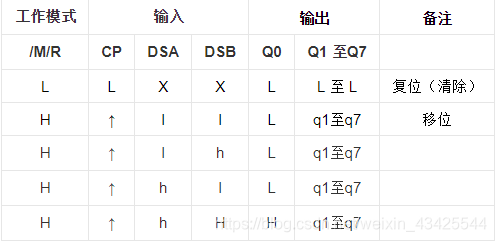

真值表

真值表

H = HIGH(高)电平

h = 先于低-至-高时钟跃变一个建立时间 (set-up time) 的 HIGH(高)电平

L = LOW(低)电平

l = 先于低-至-高时钟跃变一个建立时间 (set-up time) 的 LOW(低)电平

q = 小写字母代表先于低-至-高时钟跃变一个建立时间的参考输入 (referenced input) 的状态

↑ = 低-至-高时钟跃变

数据通过DSA,DSB这两个输入端之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。当其中任意一个为低电平,则禁止新数据输入;当其中有一个为高电平,则另一个就允许输入数据。 因此两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

当 MR为低电平时,其它所有输入端都无效,同时所有输出端均为低电平。为高电平时,允许数据一直输出。

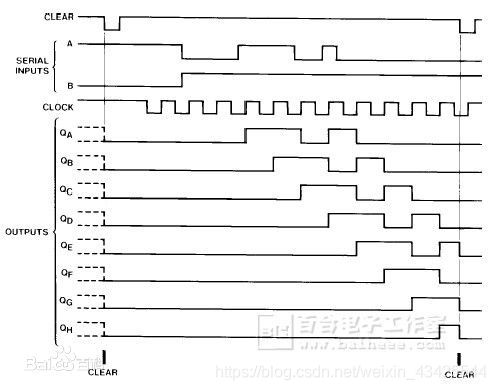

时序图

时序图

时序图

MR为高电平时,数据输入端一个为高电平,另一个输入数据,时钟端一直输入时钟。输出端就移位输出数据。

使用

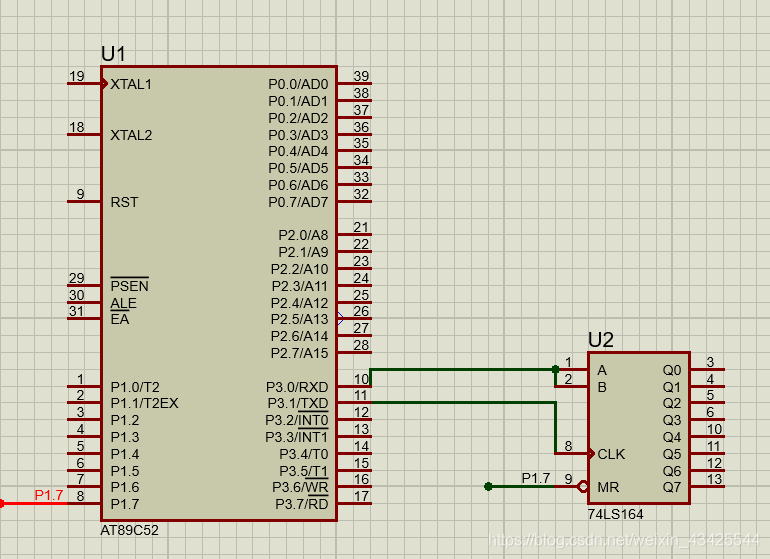

接法

接法

输入端接RXD,时钟端接TXD,MR随便接一控制端(P0口要上拉电阻),输出端随意,根据自己的需求。

#include<reg52.h>

sbit MR=P1^7; //位定义

main()

{

SCON=0X00; //串口方式0.禁止接收数据

IE=0X90; //打开总中断,串行口中断

MR=1; //一直允许数据传输,

while(1)

SBUF=0X0F; //发送数据

}

void interrupt_uart() interrupt 4

{

TI=0; //软件置0

}

上面给出简单的示范,看懂程序后就可以自行设计更复杂的程序,可以想一下用它驱动数码管。

74LS165

74LS165芯片,它是 8 位并入串出移位寄存器 (使用移位寄存器芯片可以扩展一个或多个 8 位并行 I/O 口)。

引脚

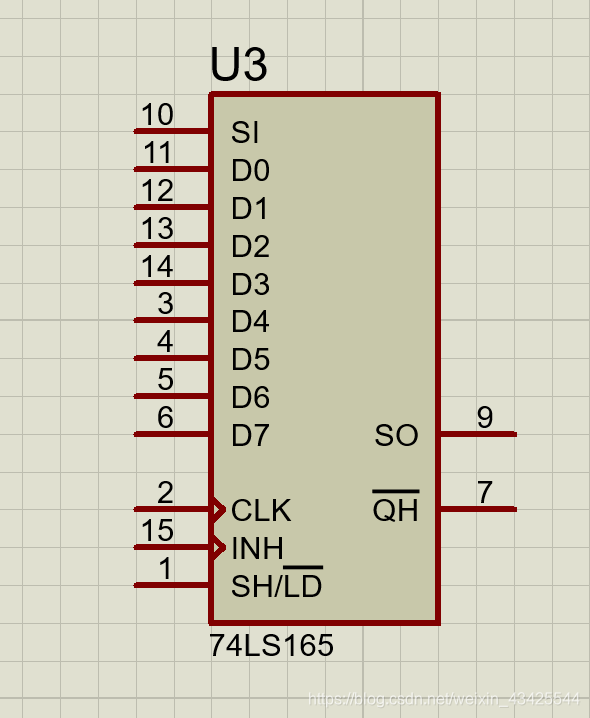

74LS165

74LS165

SH/LD(shift/ load 移位 /置位):移位与置位控制端。高电平时表示移位, 低电平时表示置位。在开始移位之前,需要先从并行输入端口读入数据,这时应将 SH/LD置 0,并行口的 8 位数据将被置入 74LS165 内部的 8 个触发器,在 SH/LD 为 1时,并行输入被封锁,移位操作开始。

INH (clock inhibit 时钟抑制):时钟禁止端。当 INH 为低电平时,充许时钟输入。

CLK(clock) :时钟输入端

D0~D7:并行输入端

SI(serial input 串行输入):串行输入端, 用于扩展多个 74LS165 的首尾连接端。

SO( serial output):串行输出端 .

QH:也是串行输出端,它与 SO 是反相的关系,即 QH=SO.

VCC(16 引脚,在 proteus 中被隐藏 ):已经默认接 +5V 电源端 .

GND(8 引脚,在 proteus中被隐藏 ):已经默认接地

使用

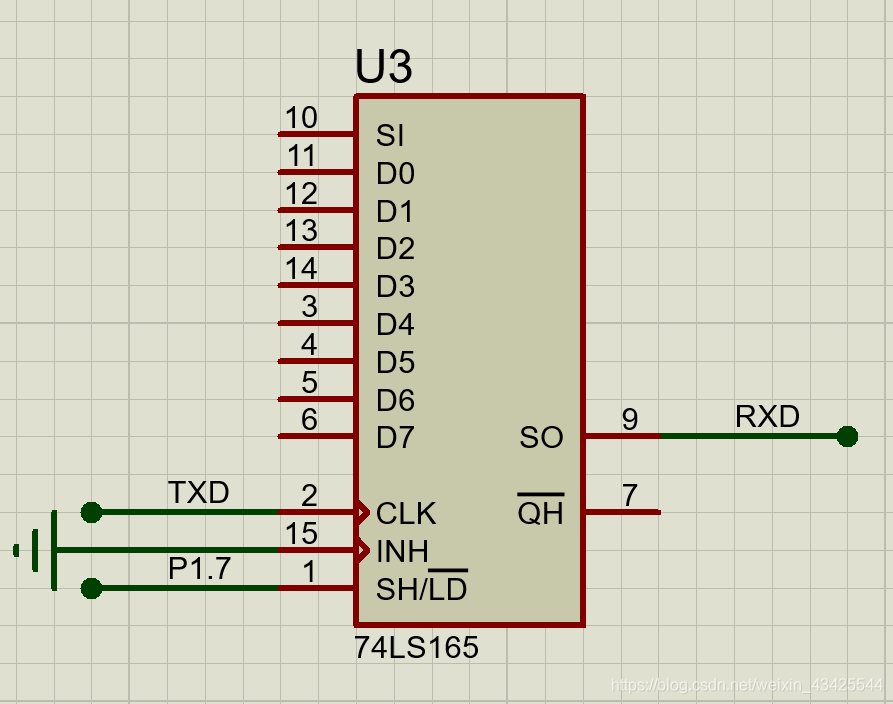

接法

接法

串行口输出端接RXD,时钟端接TXD,移位/置位端接控制端,时钟抑制端接地,允许时钟输出。输入端自行决定,剩下两个端口没有用到就空接。

#include<reg52.h>

unsigned int date;

sbit SH=P1^7; //位定义

main()

{

SCON=0X10; //串口方式0.允许接收数据

IE=0X90; //打开总中断,串行口中断

while(1)

{

SH=0; //置位,将数据存进芯片

SH=1; // 移位,将芯片数据移入rxd

date=SBUF; //读取数据

}

}

void interrupt_uart() interrupt 4

{

RI=0; //软件置0

}

简单程序,看懂就行,简单入门,需要什么功能自行添加。

总结

串行口方式0就只有这么多内容,主要使用来拓展IO口,和外部移位寄存器一起使用。上面的程序简单易懂,主要是为了能快速看懂,当然在实战中不可能这么简单,但会用了,开发就不成问题。方式2和3只在波特率上存在区别,它们主要用在单片机的多机通讯,下一篇将详细介绍。喜欢的朋友点个关注,转发一下吧。