本人最近在做一个小项目,自己取名叫做《基于zedboard的千兆以太网底层设计》,一般我都是写好各模块的verilog代码,确定模块没bug后再做整个系统级联,之后直接先进行综合看看有没有bug,有则改进,没则继续写约束,然后器件实现。

但是这个项目,我在第一步就错了,先把我找到的原因说下:是因为zedboard分为ps和pl端,zedboard的PHY芯片是有ps端控制,而我直接将其引脚用ps端驱动了。出现了以下vivado报错:

废话不多说,来看问题,vivado综合时保持如下:

[Vivado 12-1411] Cannot set LOC property of ports, Site location is not valid ["F:/xilink_file/ethernet_test/ethernet_test.srcs/constrs_1/new/ethernet_constraints.xdc":10]

。。。。。

[Vivado 12-1411] Cannot set LOC property of ports, Site location is not valid ["F:/xilink_file/ethernet_test/ethernet_test.srcs/constrs_1/new/ethernet_constraints.xdc":24]

基本上我是在所有设计都完成时,先约束引脚,最后综合后再做时序约束,再利用singnaltapii(vivado上叫ILA)做板级验证。但是我在综合时遇上上述问题,说明我的引脚不可用。

去查阅xilinx官方论坛与器件商DIGILENT论坛,发现国外一老哥也是做以太网遇到了同样的问题。

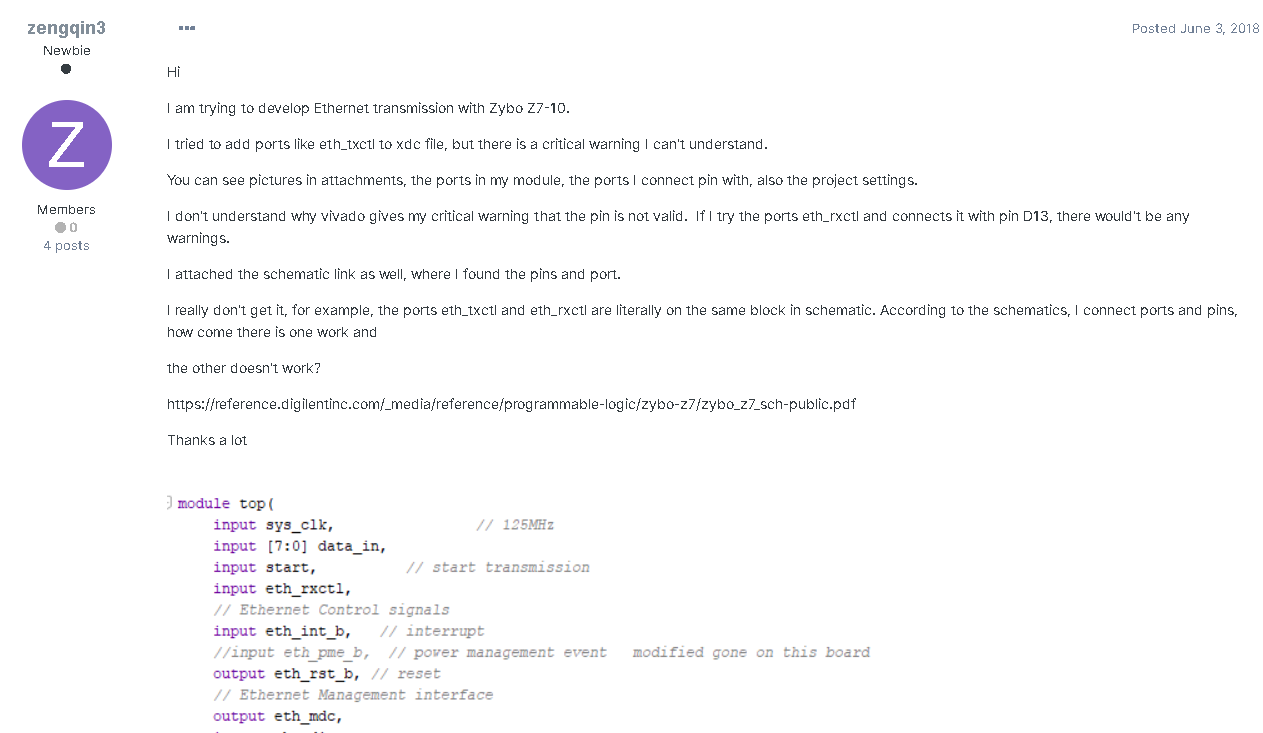

大意是“我用的zedboard z7010开发版写了一个以太网驱动程序,按照原理图上搭配了引脚但是还是出现了严重警告的问题,难度是我原理图拿错了吗?”

大佬的回答是

大意是通过pl(纯逻辑)驱动以太网现在在论坛还处于讨论阶段,因为zedboard上的以太网芯片是直接与PS端(ARM端)相连的,PL端没有与PHY芯片直连,所以没法用纯底层verilog逻辑电路驱动PHY芯片。

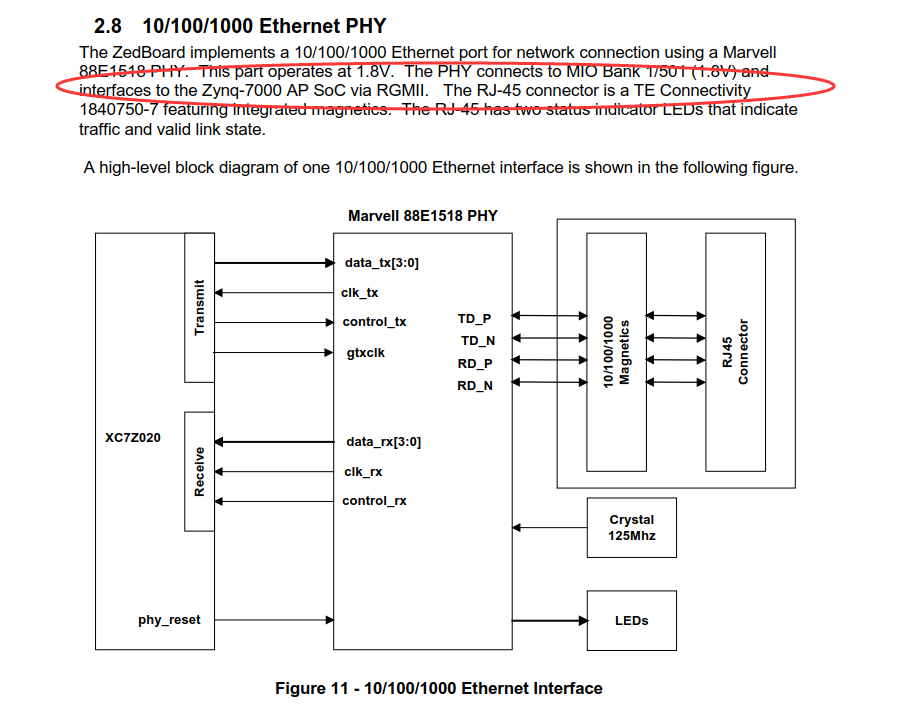

看到这里,我马上又去翻了一下zedboard的用户手册。

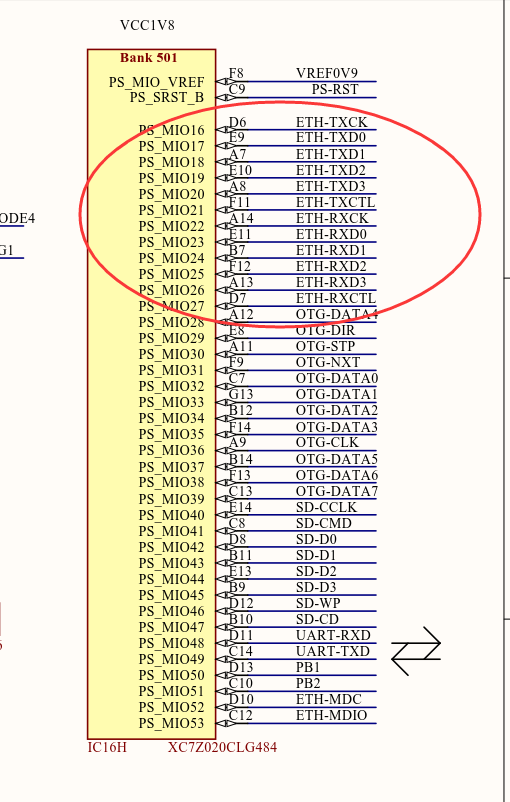

PHY芯片通过MIO Bank连接z7000Soc,也就是说,想要驱动PHY芯片,需要看看MIO Bank是谁家管的引脚(PL还是PS)。我又去翻了下原理图。

果然是PS端控制的引脚,也就是我想驱动zedboard的以太网是绕不开ARM的。算我自己的问题,第一步方向就不对,固定思维让我走向了穷途。

看看有没有大佬有其他的解决办法。

我先尝试去玩玩ARM吧,看看能不能再年前跑起来,感觉在IC设计的道路越走越远:)