恩智浦的i.MX RT1010是跨界处理器产品,作为i.MX RT跨界MCU系列的一个新的切入点,i.MX RT1010是成本最低的LQFP封装方式与i.MX RT系列产品一贯的高性能和易用性的结合产物。

i.MX RT1010处理器基于ARM Cortex-M7平台,它具有较高的CPU性能和最佳的实时响应,并具有丰富的外设资源。其中FlexIO是一个高度可配置的模块,能够模拟多种不同的通信协议,包括UART, I2C, SPI, I2S等。本文介绍如何利用i.MX RT1010的FlexIO外设来模拟SSI接口。

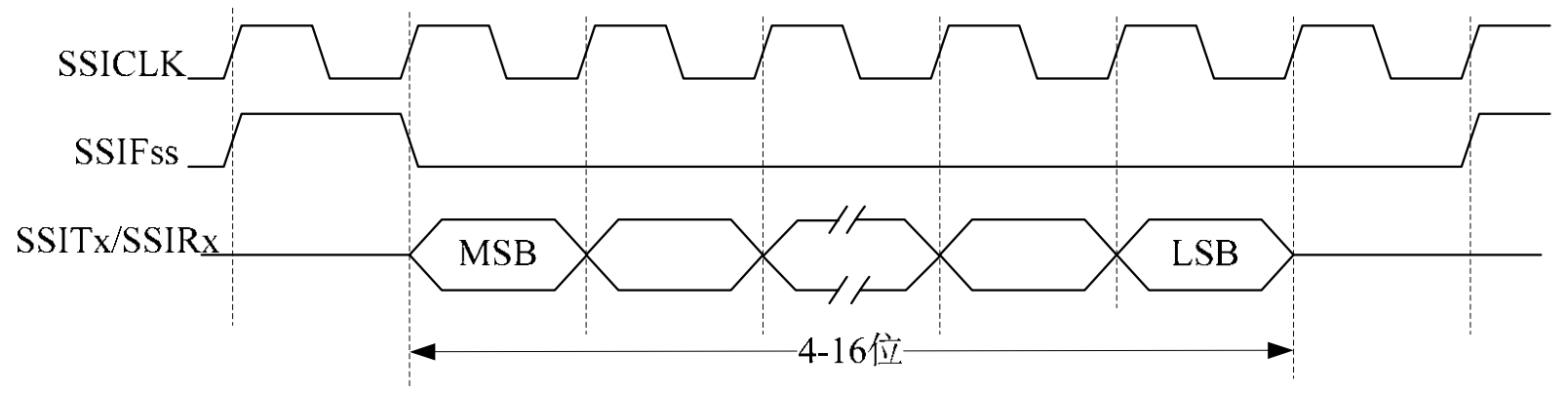

一、SSI介绍

SSI全称Synchronous Serial Interface,即同步串行接口。本文中,i.MX RT1010的FlexIO外设要模拟的SSI接口是一种能够与Texas Instruments(德州仪器,TI)同步串行接口的器件进行同步串行通信的主机或从机接口,它的单次传输通信格式如下所示。

二、硬件平台

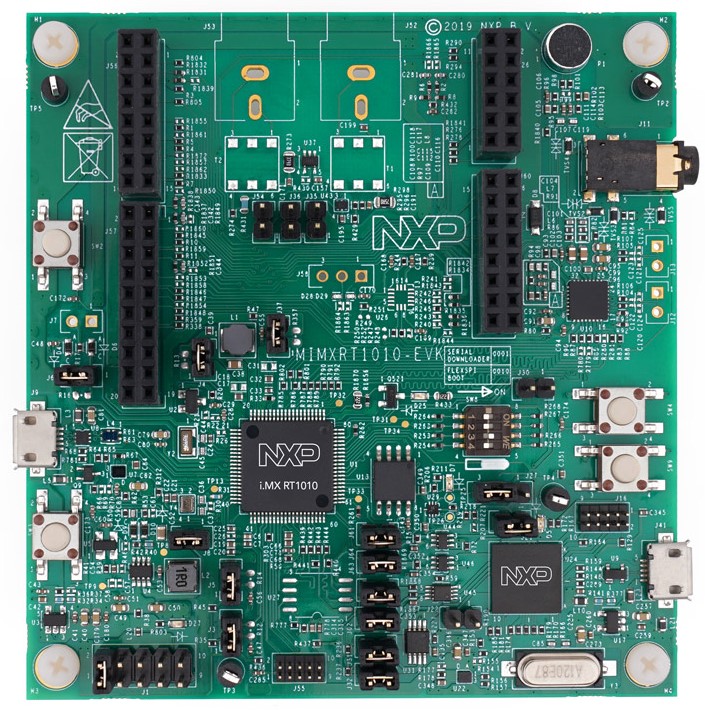

本应用笔记主要介绍如何使用FlexIO模块模拟SSI接口。整个demo基于如下所示的i.MX RT1010 EVK板子进行开发。

为了模拟同步串行接口(SSI)的master(例如控制器)和slave(例如传感器)之间的通信,在此演示中使用了两块i.MXRT1010 EVK板子。 一块板用于模拟SSI master设备,另一块板用于模拟SSI slave设备。另外,为了能够成功演示该demo,需要对i.MX RT1010 EVK板子进行如下操作和改动。

SSI master板子和SSI slave板子之间按如下关系连接:

| 引脚名称 | Master 板子 | -------- | Slave板子 | Slave板子 |

|---|---|---|---|---|

| SSI_RX | J26-4 | <------> | SSI_TXJ26-8 | J26-6 |

| SSI_TX | J26-6 | <------> | SSI_RX | J26-4 |

| SSI_CLK | J26-8 | <------> | SSI_CLK | J26-8 |

| SSI_Fss | J56-10 | <------> | SSI_Fss | J56-10 |

| GND | J1-10 | <------> | GND | J1-10 |

在i.MX RT1010上,FLEXIO共有27个引脚。 在本应用中,有4根FlexIO引脚分别用于模拟SSI_Fss引脚,SSI_RX引脚,SSI_TX引脚和SSI_CLK。 下表给出了这4根FlexIO引脚及板子对应的位置。

| FlexIO Pin | Pin Location |

|---|---|

| flexio1.FLEXIO23 | J26-4 |

| flexio1.FLEXIO24 | J26-6 |

| flexio1.FLEXIO28 | J26-8 |

| flexio1.FLEXIO00 | J56-10 |

对板子进行一些改动:

- 去掉电阻R792,并在RT1010 EVK板R800处焊接0Ω电阻。

- 将ISP拨码开关SW8更改为0b0010模式。

- 将J1-3和J1-4引脚用短路帽连接,然后将USB线插到板上的J41进行电源。

下面就是搭建完毕的硬件演示平台。

三、SSI模拟

3.1 FlexIO介绍

FlexIO是高度可配置的模块,支持各种协议,包括但不限于UART,I2C,SPI,I2S这几种,并提供多种功能,例如:

-

高度灵活的16位定时器,支持各种内部或外部触发,复位,使能和禁用条件。

-

可编程的与总线时钟无关的波特率,在stop模式下支持异步操作。

-

支持中断,DMA或轮询的发送/接收操作。

-

用于并行接口支持的1、2、4、8、16或32位的移位宽度。

-

具有发送,接收,数据匹配模式的32位移位寄存器阵列,双缓冲移位器可实现连续的数据传输。

FlexIO是一个非常灵活的模块。对于固定的时序模拟,其配置方法不是唯一的。通过不限数量的定时器和移位器,以及不同组合的多种配置方法可以实现同样的效果。本应用中分别介绍了一种实现SSI master和SSI slave的配置方法。

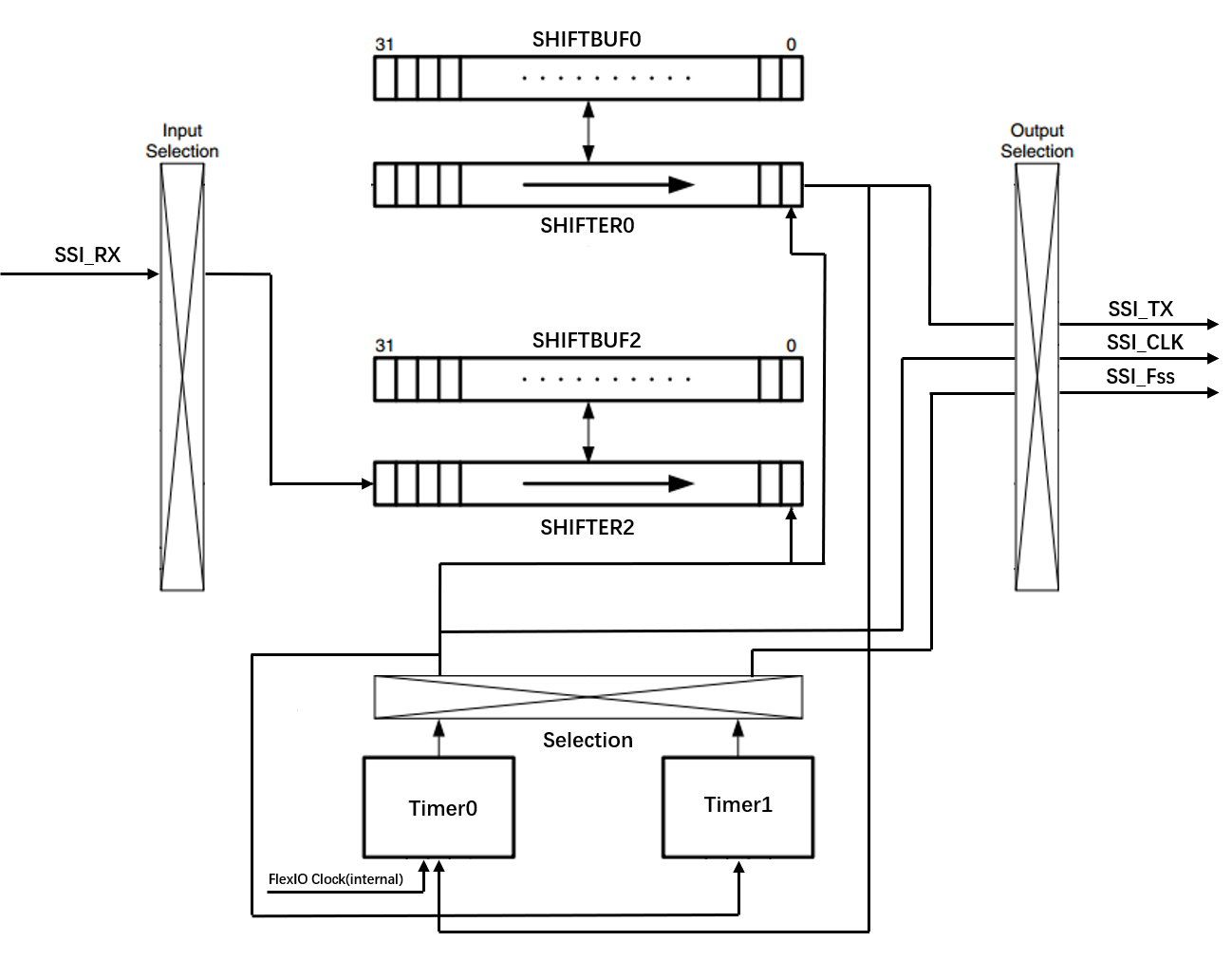

3.2 SSI master配置

总共使用两个Timer,两个Shifter用于模拟SSI master设备。Timer0用于产生SSI_CLK信号,Timer1用于产生SSI_Fss信号。Shifter0连接到SSI_TX引脚,并在SSI_Clk的每个上升沿发送数据,Shifter2连接到SSI_RX引脚,并在SSI_Clk的每个下降沿接收数据。下图显示了FlexIO模拟SSI master接口的内部连接。

Timer0配置为双8位计数器,在触发事件高电平时被使能,在比较事件到来时禁用。Timer0的触发源连接到内部Shifter0,Timer0的计数递减源配置为FlexIO时钟,Shift时钟是由Timer0的每一次计时输出决定的,Timer0的起始位也需要被使能。另外,Timer0需要被配置为能够被Shifter0的状态标志位触发。在此应用中,由于传输频率为200kHz,因此Timer0的Compare寄存器的值经计算得到需配置为0xF1D。

Timer1被配置为16位计数器模式,由Timer0触发,当Timer0被使能时也使能,在比较事件到来时禁用。Timer1的计数递减源设置为触发信号的两个边沿。

Shifter0配置为Transmit模式,并在移位器时钟的上升沿移位,使能移位器起始位并将其设置为逻辑低电平。

Shifter2配置为Receive模式,并在移位器时钟的下降沿移位,使能移位器起始位并将其设置为逻辑低电平。

下面给除了SSI master模式下详细的寄存器配置:

- FlEXIO01.SHIFTCTL[0] = 0x00031502

- FlEXIO01.SHIFTCTL[2] = 0x00801601

- FlEXIO01.SHIFTCFG[2] = 0x00000002

- FlEXIO01.SHIFTCFG[2] = 0x00000002

- FlEXIO01.TIMCTL[0] = 0x01C31A01

- FlEXIO01.TIMCTL[1] = 0x03430003

- FlEXIO01.TIMCFG[0] = 0x00002222

- FlEXIO01.TIMCFG[1] = 0x00102100

- FlEXIO01.TIMCMP[0] = 0x00000F1D

- FlEXIO01.TIMCMP[1] = 0x00000002

当数据从SHIFTER加载到SHIFTBUF寄存器中或数据从SHIFTBUF寄存器加载到SHIFTER中时,如果已经将SHIFTER状态标志位(SHIFTSDEN SSDE)置1,就可以产生一个DMA请求。整个 SHIFTER的微体系结构如图所示,它充分展示了SHIFTER中各个模块之间的关系以及IO引脚输入输出的关系。

3.3 SSI slave配置

SSI slave的配置与SSI master的配置类似,SSI slave的模拟也是需要用到两个Shifter和两个Timer。 Timer0用于检测SSI_Fss信号,Timer1用于检测SSI_CLK信号。Shifter0连接到SSI_TX引脚,Shifter2连接到SSI_RX引脚。下图显示了FlexIO模拟SSI slave接口的内部连接。

Timer0配置为双8位计数器,在触发事件高电平时被使能,在比较事件到来时禁用。 Timer0的触发源是SSI_Fss输入引脚。 Timer0的计数递减源配置为FlexIO时钟,Shift时钟是由Timer0的每一次计时输出决定的,Timer0的起始位也需要被使能。同样,由于传输频率为200kHz,因此Timer0的Compare寄存器的值经计算得到为0xF1D。

Timer1被配置为16位计数器模式,将SSI_Fss引脚的输入作为触发事件,并在触发信号的上升沿使能,在Timer0禁用时也禁用。Timer1的计数递减源设置为SSI_CLK输入引脚的两个边沿。

Shifter0配置为Transmit模式,在移位器时钟的上升沿进行移位操作,Shifter0的起始位禁用并使其在第一次移位操作时加载数据。

Shifter2配置为Receive模式,在移位器时钟的下降沿进行移位操作,Shifter2的起始位禁用并使其在第一次移位操作时加载数据。

下面给除了SSI slave模式下详细的寄存器配置:

- FlEXIO01.SHIFTCTL[0] = 0x00031502

- FlEXIO01.SHIFTCTL[2] = 0x00801601

- FlEXIO01.SHIFTCFG[2] = 0x00000001

- FlEXIO01.SHIFTCFG[2] = 0x00000001

- FlEXIO01.TIMCTL[0] = 0x00400001

- FlEXIO01.TIMCTL[1] = 0x00401A03

- FlEXIO01.TIMCFG[0] = 0x00002402

- FlEXIO01.TIMCFG[1] = 0x01201600

- FlEXIO01.TIMCMP[0] = 0x00000F1D

- FlEXIO01.TIMCMP[1] = 0x0000000F

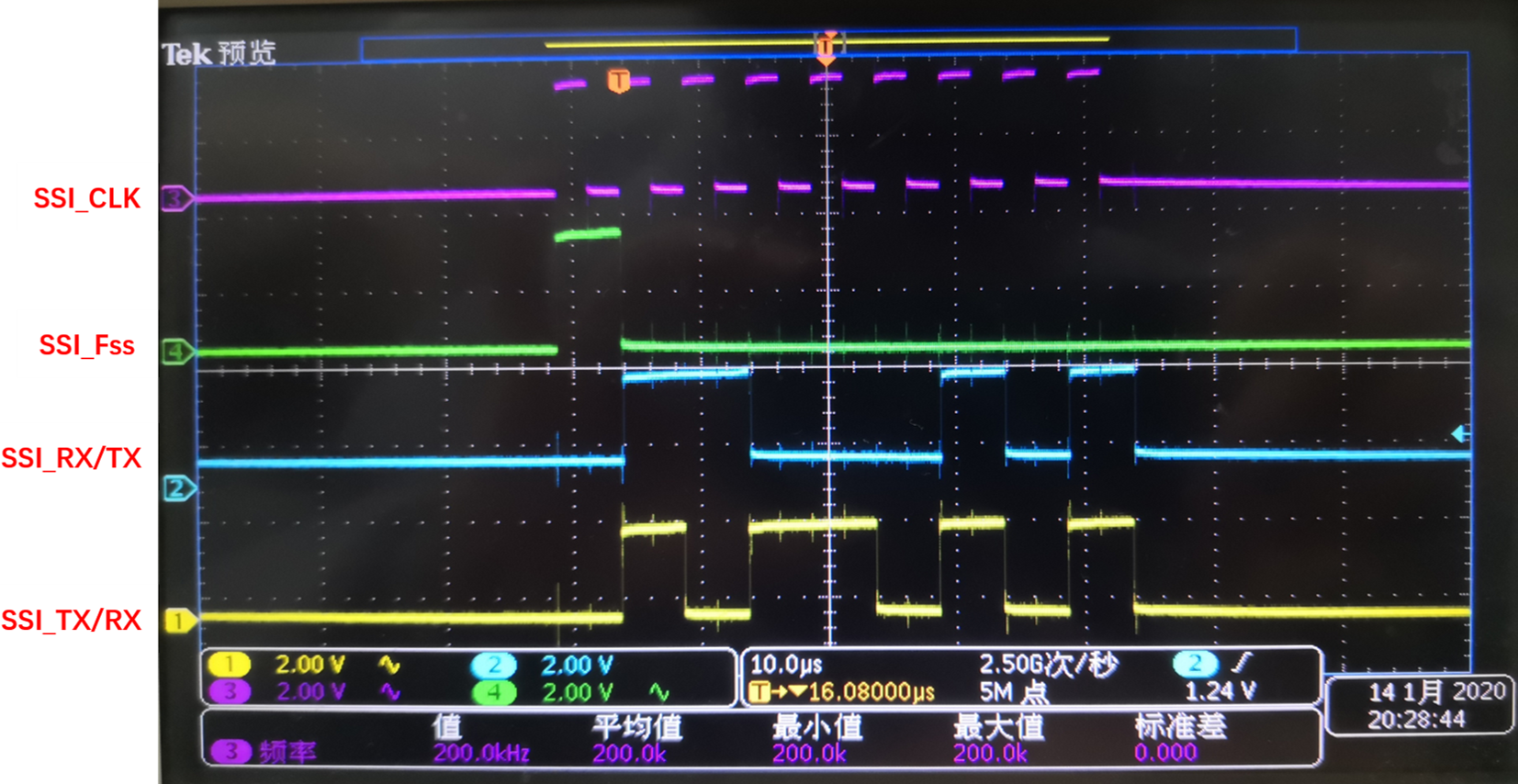

3.4 demo演示

经过上述介绍,FlexIO模拟SSI接口的配置已经介绍完毕,下面以两块i.MX RT1010 EVK板子之间的通信为例进行演示demo。首先,将各个SSI信号引脚连接到示波器,之后将板子上电后,抓取两块板子之间的第一次SSI通信数据,其波形如下图所示。SSI master板子将数据0xC5发送到SSI slave板子,并同时接收到数据0xB5,数据与图中的波形匹配,达到预期的SSI模拟效果。

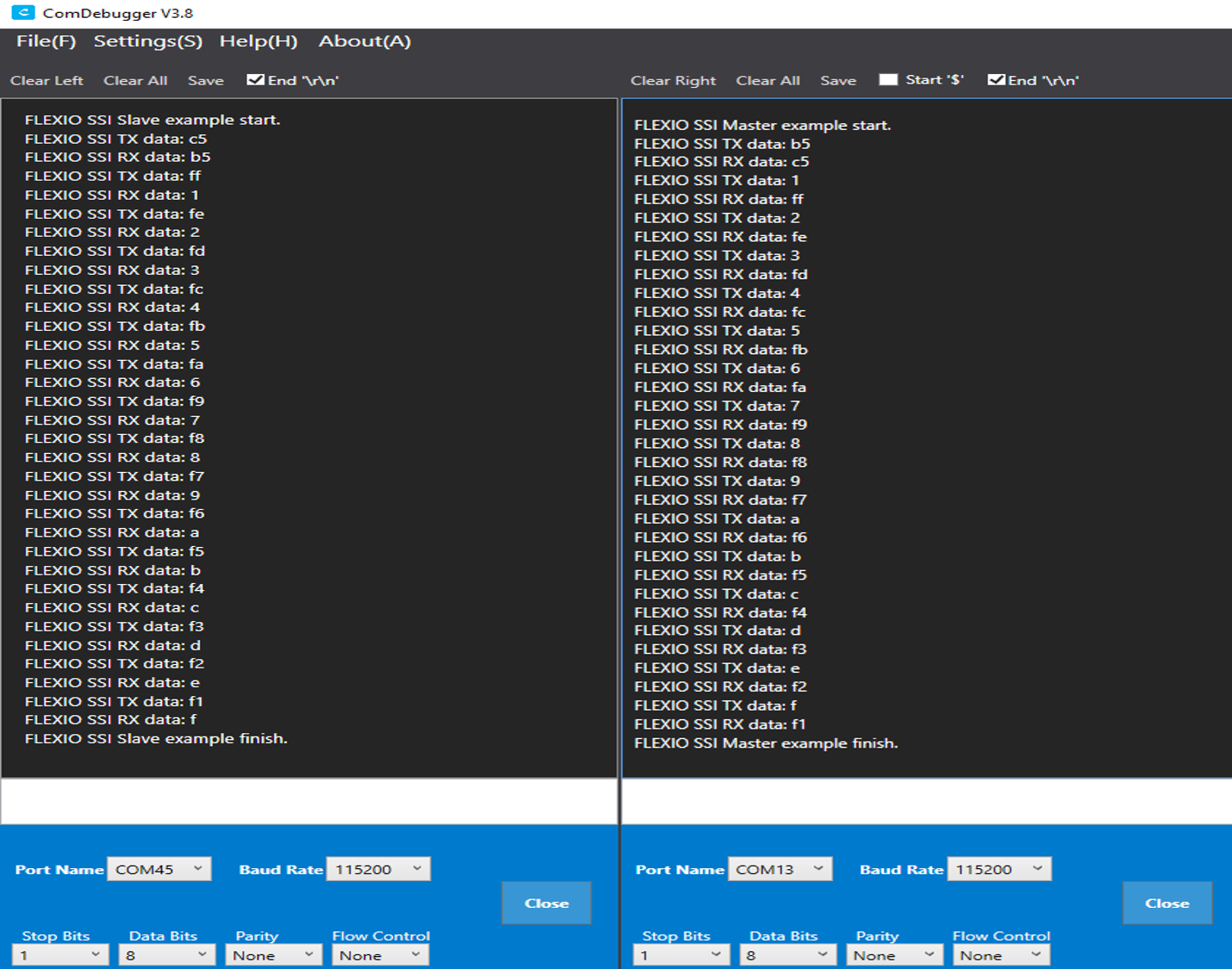

另外打开串口助手,将硬件平台上电后,可以看到如下所示的串口打印信息,至此demo演示完毕。

3.5 注意事项

在利用FlexIO模拟SSI时,需要注意三点:

- 由于FlexIO同步延迟,串行输入数据的建立时间为1.5个FlexIO时钟周期,此时SSI的最大时钟频率应为FlexIO时钟频率的四分之一。

- 由于FlexIO同步延迟,串行输出数据的输出有效时间为2.5个FlexIO时钟周期,此时SSI的最大波特率应为FlexIO时钟频率的六分之一。

- 除了本文给出的Timer和SHIFTER的配置外,读者也可以利用其它配置模拟出SSI接口,这个方法不是唯一的。

至此,i.MX RT1010之FlexIO模拟SSI外设介绍完毕。