iFPGA-Cable调试器使用说明

全文分为7部分:

第0部分:实物、连线及其驱动安装说明

第1部分:Xilinx JTAG下载器

第2部分:UART工具

第3部分:Altera JTAG下载器

第4部分:Lattice JTAG下载器

第5部分:高云 JTAG下载器

第6部分:相关软件及其Demo附件下载地址

第0部分:实物、连线及其驱动安装说明

基本特性:

- Channel A为JTAG,电平1.8~5V,在Xilinx 平台(include ISE 13.2+,Vivado),TCK最大时钟频率30MHz;

- Channel B为UART,电平1.8~5V,波特率的设置满足日常需求,具体更多配置,可参看FTDI官网AN;

- 兼容部分Altera平台Quartus II版本和器件,支持SignalTap在线调试(此功能未在所有版本和器件上全部测试,用户可自行研究);

- 此调试器既可作为Xilinx JTAG下载器,又可作为部分Quartus软件版本和Altera 部分器件下载调试工具,亦可作为串口工具

此举,很好的解决了烧写Flash速度(Zynq平台烧写QSPI Flash速度,优于之前的Cypress方案),同时兼顾串口调试功能,在很多SOC平台,串口PHY无须存在在PCB上,节约板级空间和BOM成本,一举两得!在需要串口时,只需将TX/RX线引出,一个工具,两种功能!

配置:iFPGA-Cable板子一套,1.5米带线圈miniUSB接头线,10pin带线套2.54标准杜邦线!

miniUSB接口线

全新设计

iFPGA-Cable实物图(版本1,版本1与版本2功能没有区别)

连线说明:

JTAG-Vref/USB-Vref,必须供电,否则不能工作!

Power指示灯:下载器电源灯

UART指示灯:串口工作指示灯

JTAG指示灯:JTAG工作指示灯

驱动安装:

在装有ISE版本或者vivado版本的PC端,通过USB连接iFPGA-Cable后,PC端会自动进行驱动安装,如下图所示,安装成功后会有提示

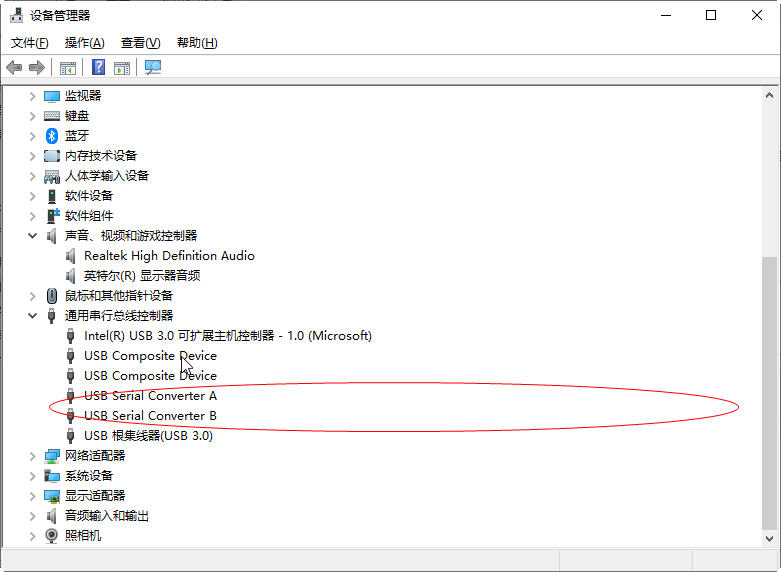

此时在设备管理器中,会看到新增2个设备A和B

打开ISE iMPACT,通过JTAG链路会看到FPGA器件,Vivado类似

在设备管理器中,点击USB Serial Convert B属性

使能VCP功能,虚拟串口功能,如果未安装成功,用户可在官网下载驱动 VCP驱动:https://www.ftdichip.com/Drivers/VCP.htm

重新插拔USB接口,串口安装成功,系统分配COM5口

可以通过串口进行通讯

第1部分:Xilinx JTAG

Vivado识别

ISE识别

ISE烧写SPI Flash

第2部分:UART

我们在验证板子上新建一个MicroBlaze工程,UART 波特率115200

为了验证串口的输入输出有效,在microblaze SDK中增加下述程序

1 #include <stdio.h> 2 #include "platform.h" 3 #include "xgpio.h" 4 #include "xparameters.h" 5 #include "xuartlite.h" 6 XGpio LED; 7 void print(char *str); 8 void Init_Display(void) 9 { 10 xil_printf("******************************************************** "); 11 xil_printf("*Chuangxin Electronic Labs Demo. * "); 12 xil_printf("*http://www.cnblogs.com/ifpga * "); 13 xil_printf("*Test the iFPGA-Cable Tool * "); 14 xil_printf("*Mar. 12, 2018 * "); 15 xil_printf("******************************************************** "); 16 } 17 18 ..... 19 20 void UART_SEL(void) 21 { 22 xil_printf(" Please Select the test: "); 23 xil_printf("*0: 0 Leds on, 8 Leds off . "); 24 xil_printf("*1: 1 Leds on, 7 Leds off . "); 25 xil_printf("*2: 2 Leds on, 6 Leds off . "); 26 xil_printf("*3: 3 Leds on, 5 Leds off . "); 27 xil_printf("*4: 4 Leds on, 4 Leds off . "); 28 xil_printf("*5: 5 Leds on, 3 Leds off . "); 29 xil_printf("*6: 6 Leds on, 2 Leds off . "); 30 xil_printf("*7: 7 Leds on, 1 Leds off . "); 31 xil_printf("*8: 8 Leds on, 0 Leds off . "); 32 xil_printf("*9: 8 Leds blinking . "); 33 34 } 35 36 ... 37 38 int main() 39 { 40 41 int rec_data=0; 42 int KK; 43 Init_Display(); 44 UART_SEL(); 45 Init_Gpio_LED(); 46 while(1) 47 { 48 rec_data = XUartLite_RecvByte(XPAR_UART_1_BASEADDR) ; 49 if(rec_data >= 48 && rec_data <=57) 50 { 51 KK = rec_data - 48; 52 xil_printf(" UART input value is : %d ", KK); 53 Led_drivers( KK ); 54 } 55 else if(rec_data == 13) 56 UART_SEL(); 57 58 } 59 60 61 return 0; 62 }

连接示意图(Vref连接后,指示灯会亮,USB指示灯/JTAG指示灯/串口指示灯)

程序固化后,连接串口27,并进行配置

串口波特率配置

板子输出

键盘可以输出,0~9,板子可以有相关动作

第3部分:Altera JTAG

支持部分Quartus版本,未全测试,如有需要可自行研究

了解JTAGServer所在目录

将jtag_blaster64.dll/jtag_blaster.dll复制到此目录下,打开Altera Quartus II Programmer

可以方便下载,亦可以进行JTAG SignalTap调试

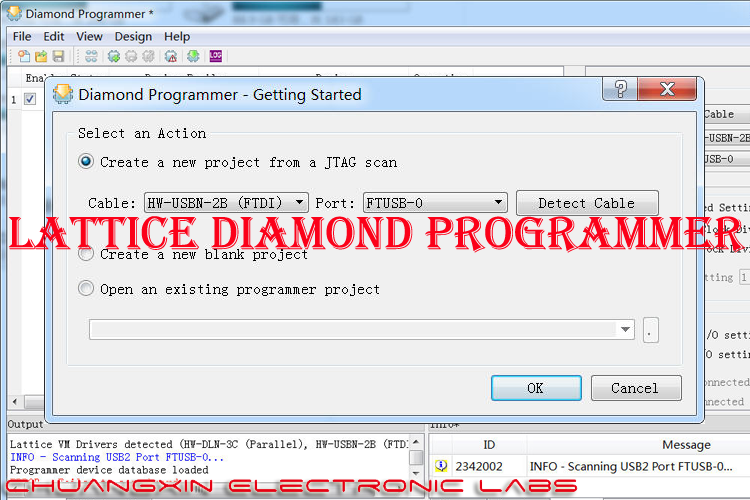

第4部分:Lattice JTAG

支持Diamond环境,免驱动

第5部分:高云下载器

下载前,确保目标板对下载器供电,否则下载器扫描不到器件!

在Programmer中,双击驱动,进行安装(对于用户安装了高云软件)则可以在安装目录查找

安装完成

设备管理器可以看到2个通道的设备

打开下载软件进行设置,默认是2MHz频率

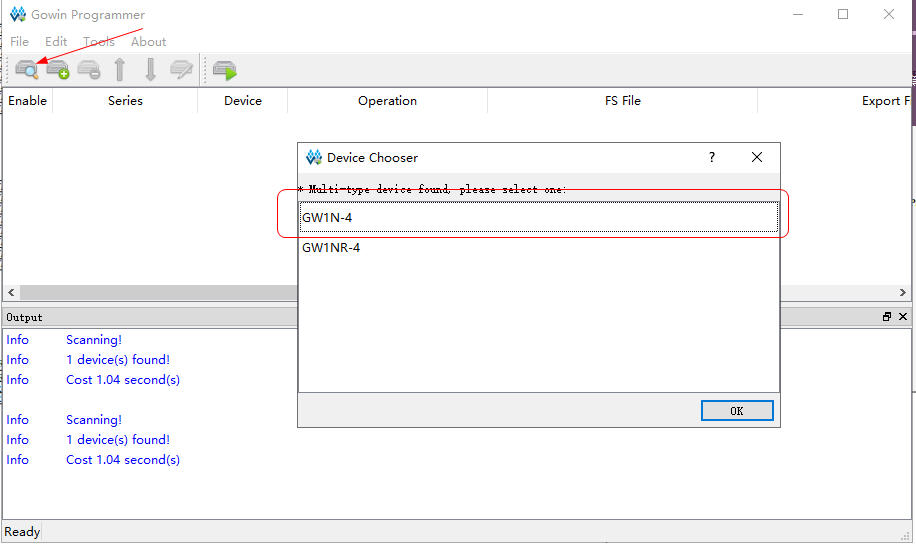

连接好器件,点击Scan device

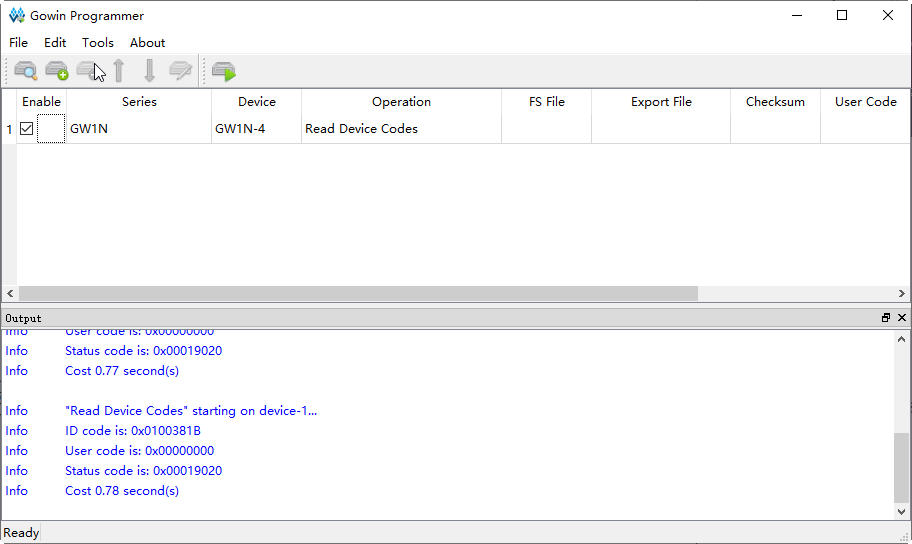

发起读取器件Id操作,JTAG链路建立,后续可进行SPI .SRAM配置下载。

第6部分:相关软件及其Demo附件下载地址

串口工具、测试工程、官方驱动

可通过百度网盘下载

链接:https://pan.baidu.com/s/6YWepeuHuBZlbtaH-Y-L1VA 密码:9srg