一、简单介绍

1.1 概念

PMU,platform measurement unit,平台管理单元。

很多人会将它当做power measurement unit(电源管理单元)的缩写,认为就是管理电源和功耗的。其实PMU除了电源管理功能,还具有其他功能。官方描述如下:

系统启动前的初始化

电源管理

软件测试库执行(可选)

系统错误处理

1.2 总览

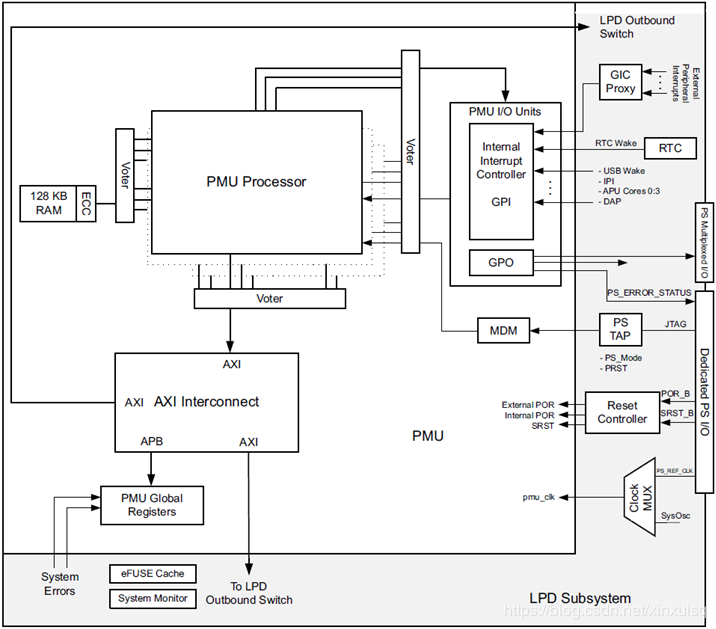

在电源管理章节里,我们简单介绍了Zynq U+里的4个功耗域。其中PMU模块本身处在低功耗域,如下图为PMU的模块框图:

PMU包括以下子组件:

专用的、容错率高的三模冗余处理器

ROM中会存放PMU ROM代码,功能包括PMU的启动顺序、处理电源开关请求的例程和中断

用于存放代码和数据的带ECC功能的128kb内存

只能被PMU访问的PMU本地寄存器

可以被PMU处理器和系统里其他总线的master口访问的PMU全局寄存器。包括所有电源、隔离和复位请求寄存器。还包括错误捕获寄存器和系统电源状态寄存器。

PMU外部的master接口可以通过32位的AXI slave接口访问PMU的RAM和全局寄存器。

PMU中断控制器管理了PMU的23个中断,其中四个来自处理器间的互连(IPI)

PMU/MIO/PL相连的GPI和GPO寄存器接口,以及其他PS和PMU的互联信号:

1) 6个输出,6个输入

2) PMU端有32个GPO输出到PL,PL端有32个GPI输入到PMU

3) 47个系统错误到PMU

4) CSU的错误码

5) 32个MBIST状态信号和32个MBIST完成信号

6) 3个直接复位控制信号

7) 4个AIB状态信号和4个AIB控制信号

8) 11个逻辑清除状态信号

9) DDR保持控制信号

10) 3个从PL端到CSU的可编程配置信号

可以通过PSJTAG接口访问使用PS TAP控制器的PMU MDM控制器

二、PMU功能

2.1 PMU处理器

PMU处理器是一个不带cache的三模冗余处理器。处理系统通过在PMU上应用冗余和在RAM侧应用ECC来提供容错能力。

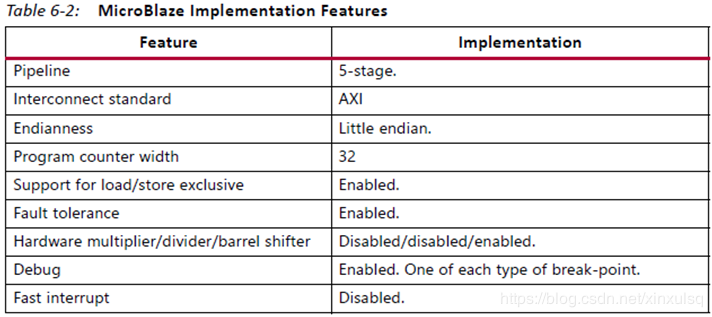

下图为PMU处理器的实现功能(实际主要是一个MicroBlaze核)。

2.2 PMU处理器接口

PMU提供输入和输出信号,这些信号按功能可以分组如下:

32位的AXI master接口和低功耗域(LPD)互连,允许PMU访问其他PS资源,包括SLCR寄存器和IPI块

通过LPD inbound switch的32位AXI slave接口,允许外部处理器访问PMU全局寄存器和PMU RAM

PMU时钟和复位信号。

和PS内所有islands相连的电源控制接口:

1) L2、OCM和TCM RAMs

2) APU_Cores[3:0]

3) 双核Cortex®-R5实时处理器

4) USB0、USB1

5) GPU像素处理器PP0和PP1

6)全功率域和PL功率域的crossing bridges

2.3 PMU时钟

PMU工作在SysOsc时钟(180 MHz±15%),该时钟由位于系统监视器(PS SYSMON)模块内的内部环形振荡器(IRO)提供。时钟一直被门控着直到POR模块检测到VCC_PSAUX升高。一旦电压达到阈值,SysOsc便开始振荡工作。同时,PMU的处理器也跟着复位。复位需要一个时钟沿的触发,等到电压升高,POR_B输入也会跟着起来。这保证了PMU处理器GPOs在器件上电后能够初始化。

2.4 PMU复位

PMU有两个复位,POR复位和系统复位SRST,这两个复位都来自于芯片的复位模块。

POR复位可以完全清除PMU状态,保证所有的电源域上电和所有的隔离被禁用。POR复位后,PMU在低功耗和全功耗域执行scan和BIST清除功能。

另一方面,SRST只能复位PMU处理器子系统、PMU互连以及局部和全局寄存器的一个子集,而将大多数局部和全局寄存器保留在复位之前的状态。当通过SRST触发PMU重启时,将不会清除电源状态,PS的电源状态会被保留。

如果是直接上下电复位,将清除所有RAMs和FIFO电源状态。

2.5 PMU RAM

PMU的很多功能是由PMU处理器执行的软件提供的。ROM内存包含提供默认功能的指令。用户如果要扩展或替换这些功能,或者提供新功能,可以将软件下载到PMU处理器的128kb RAM中。PMU包括一个128kb的RAM和32位的ECC,用于保存数据和代码。PMU RAM可由PMU处理器和外部master接口通过PMU slave接口去访问。

写PMU RAM时,只支持以word为单位,也就是4byte,不支持byte为单位。如果写入的数据少于4个byte,那么必须先读取、修改这4byte,然后将整个4byte数据写回。

外部master通过APB接口访问PMU RAM时PMU处理器必须处于休眠模式。如果PMU处理器没有处于休眠状态时访问,PMU RAM将挂起系统。

2.6 PMU ROM

PMU内有一块ROM空间,包含PMU的引导代码、中断向量和PMU可以执行的服务例程(根据请求执行)。PMU ROM负责PMU中的各种功能,以下是ROM代码可以执行的任务列表:

1) Pre-boot任务

清除PMU RAM空间

使能系统监控器,检查低功耗域是否供电

根据初始化设置配置PLL时钟

触发和排序必要的scan和PS的BIST清除

释放CSU复位

2) Post-boot任务

PS内的功耗域上下电

使能和控制BISR(内置的自修复功能)

当要求或作为主电源的一部分时,充当复位模块

3) 根据要求执行固件代码

2.7 MBIST功能

MBIST,memory built-in self test,存储器内部自测试。

ROM代码可以在除去PMU外的LP域或整个FP域上启动MBIST clear操作。当使用MBIST测试或清除内存时,系统的其余部分可以正常工作。

在用户可以通过配置MBIST_RST、MBIST_PG_EN和MBIST_SETUP寄存器来启动该特定块上的MBIST进程。MBIST_DONE位被用来指示进程是否已经完成,MBIST_GOOD用来指示进程状态,0表示失败1表示成功。

关于MBIST模块的具体功能,这里不做过多描述和解析,可以参考ug1087相关文档,以后有机会也可以单独开章节学习。

2.8 Scan清除功能

归零化过程中,所有的存储元素都要移位归零,然后再验证该操作是否正确。这是由MBIST和scan清除功能实现的。scan清除引擎只能由PMU和CSU处理器通过直接接口进行控制,其他处理器如果要请求启动任何特定的can清除引擎都必须通过SCAN_CLR_REQ寄存器。当scan清除引擎启动时,来自引擎的完成状态信号从1变成0,这个信号直接路由到PMU的LOGCLR_ACK寄存器,将引擎的完成状态传递给PMU。当一个scan清除引擎完成它的操作时,它的完成状态位从0变成1,生成一个到PMU的中断信号。清除操作是否成功可以通过PMU LOGCLR_STATUS全局寄存器中的位来检查。

2.9 PMU Interconnect

PMU包含一个2*3的互连,支持2个AXI master,2个APB slave和1个AXI slave。

2个AXI master口中,其中一个是32bit,来自三模冗余处理器;另外一个master口来自低功耗电源域的主互连,该接口允许系统中的任何主机访问PMU从机。

2个APB slave口是PMU RAM和PMU全局寄存器文件。

1个AXI slave口在路由到LPD交换机的端口上,只允许被PMU处理器发起访问。

2.10 PMU I/O寄存器

PMU IO寄存器包括所有和中断、GPI/GPO以及可编程间隔计时器PITs相关的寄存器。PMU_IOMODULE寄存器控制中断控制器、GPI{0:3}、GPO{0-3}和PIT0-PIT3。PMU_GLOBAL寄存器使能系统处理器来控制中断并触发PMU服务请求。PMU处理器的Memory空间如下表:

2.11 PMU全局寄存器

全局寄存器集包括用作PMU和其他块之间的通信手段的寄存器,以同步有关电源/系统管理和复位的活动。

2.12 GPIs和GPOs

PMU处理器包括4个本地的GPI banks和4个GPO banks。其中,GPI0和GPO0保留给专用的PMU处理器子系统特性,GPI3和GPO3保留给和PL的通信。GPI1、GPI2、GPO1和GPO2用于PS硬件特性与PMU之间的通信。具体的寄存器描述这边不做深入研究,大家可以看看ug1085。

2.13 PITs

PMU处理器包括4个32bit的可编程间隔计时器PITs。PITs的时钟源是PMU的固定系统振荡器SysOsc。这些是通用计时器,用于作为延迟计数器或事件调度,可以通过GPO0配置。

2.14 PMU中断

当PMU处理器接收到一个中断时,它会分流到PMU的ROM,ROM代码必须在PMU I/O模块的中断控制器中检查正在挂起的中断寄存器并分流到ROM或RAM对应的中断服务例程里。挂起中断之间的优先级可以由PMU固件强制执行,如果不存在,则由ROM来管理优先级。

2.15 PMU的错误处理和自救逻辑

PMU对每个错误负责获取、上报并采取合适的处理。每个系统错误都定义在PMU_GLOBAL错误状态寄存器中。PMU还包括处理此功能所需的寄存器、逻辑和接口。

具体如何处理和自救,这里先不详细描述,可以参考ug1085。

————————————————

版权声明:本文为CSDN博主「xinxulsq」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/xinxulsq/article/details/103239535