本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

本章节介绍CMOS技术的基础知识以及执行静态时序分析所涉及的术语。

2.1 CMOS逻辑设计

2.1.1 基本MOS结构

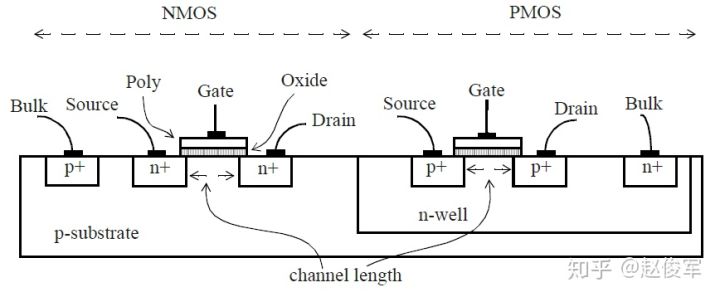

MOS晶体管(NMOS和PMOS)的物理实现如图2-1所示。源极(source)和漏极(drain)区域之间的距离(channel length)是MOS晶体管的长度,用于构建MOS晶体管的最小长度即为CMOS技术工艺的最小特征尺寸(feature size)。例如,0.25um技术允许制造具有0.25um或更大沟道长度的MOS晶体管。 通过缩小沟道的几何形状,晶体管的尺寸会变小,这样就可以在同样的面积上封装更多的晶体管。 正如我们将在后面章节看到的那样,更小的晶体管尺寸同样还可以使设计以更高的速度运行。

2.1.2 CMOS逻辑门

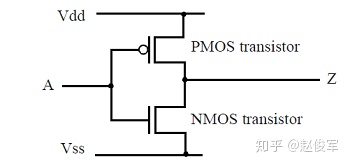

CMOS逻辑门使用NMOS和PMOS晶体管搭建而成。图2-2给出了CMOS反相器(inverter)的示例。CMOS反相器有两种稳定状态,具体取决于输入的电平状态。 当输入A为低电平(Vss或逻辑0)时,NMOS晶体管截止,而PMOS晶体管导通,导致输出Z的电平被上拉至逻辑为1的Vdd。当输入A为高电平(Vdd或逻辑1)时,NMOS晶体管导通,而PMOS晶体管截止,导致输出Z的电平被下拉至逻辑为0的Vss。在上述两种状态中的任何一种状态下,CMOS反相器都是稳定的,不会从输入端A或电源Vdd汲取任何电流。

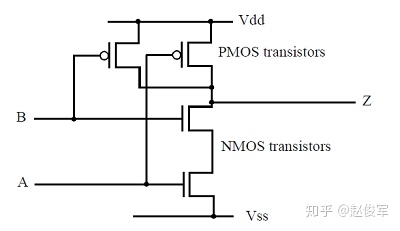

CMOS反相器的特性可以扩展到任何CMOS逻辑门。在CMOS逻辑门中,输出节点通过上拉结构(由PMOS晶体管构成)连接至Vdd,并通过下拉结构(由NMOS晶体管构成)连接至Vss。例如,图2-3展示了一个两输入CMOS与非门(nand)。在该例中,上拉结构由两个并联的PMOS晶体管组成,下拉结构由两个串联的NMOS晶体管组成。

对于任何CMOS逻辑门,上拉和下拉结构是互补的。对于逻辑0或逻辑1的输入,如果上拉结构开启,则下拉结构将关闭;类似地,如果上拉结构关闭,则下拉结构将开启。下拉和上拉结构由CMOS门实现的逻辑功能控制。例如,在CMOS与非门中,控制下拉结构的功能是“(A&B)”,即当A和B都为逻辑1时下拉被接通。类似地,控制上拉结构的功能是“(overline{A}|overline{B})”,即当A或B处于逻辑0时上拉被打开。这些特性确保了控制上拉结构的功能将输出节点的逻辑上拉至Vdd。由于下拉结构由互补函数控制,因此当上拉结构函数的值为0时,输出节点处于逻辑0。

对于逻辑0或逻辑1的输入,由于上拉和下拉结构不能同时开启,因此处于稳态的CMOS逻辑门不会对输入或电源汲取任何电流。CMOS逻辑的另一个重要方面是,输入仅对前一级构成容性负载。

若CMOS逻辑门是一个反相门,这意味着单个输入的变化(上升或下降)只能使输出往相反的方向改变,也就是说,输出无法与输入同相变化。但是,可以将CMOS逻辑门级联起来以实现更复杂的逻辑功能。

2.1.3 标准单元

芯片中的大多数复杂功能通常是使用基本构建块(basic building block)来设计的,这些基本构建块实现了简单的逻辑功能,例如与、或、与非、或非、或与非,与或非以及触发器(flip-flop)。这些基本构建块是预先设计的,称为标准单元(standard cell)。标准单元的功能和时序已预先确定,可供设计人员使用。然后,设计人员可以使用标准单元作为基本构建块来实现所需的功能。

前面小节中描述的CMOS逻辑门的关键特性适用于所有CMOS数字设计。当输入处于稳定的逻辑状态时,所有数字CMOS单元的设计都能够保证不从电源汲取电流(漏电流除外)。因此,大多数功耗与设计的功能有关,并且是由设计中CMOS单元输入端的充放电引起的。

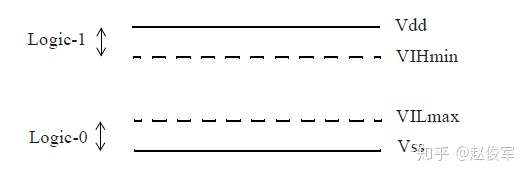

什么是逻辑1或逻辑0?在CMOS单元中,VIHmin和 VILmax这两个值定义了范围:高于VIHmin的电压值被认为是逻辑1,低于VILmax的电压值被认为是逻辑0。如图2-4所示,0.13um工艺下一个具有1.2V Vdd电源的CMOS反相器单元的典型VILmax值为0.465V、VIHmin值为0.625V。 VIHmin和VILmax的值是从标准单元的直流传输特性中得出的。直流传输特性会在接下去的6.2.3节中有更详细的描述。

2.2 CMOS单元建模

如果一个单元的输出引脚驱动多个扇出单元,则该单元的输出引脚上的总电容等于该单元正在驱动的单元的所有输入电容的总和加上构成该网络所有走线电容之和再加上驱动单元的输出电容。注意,在CMOS单元中,输入引脚仅呈现电容性负载。

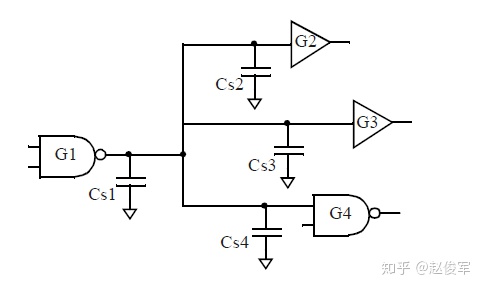

图2-5是一个单元G1驱动其他三个单元G2、G3和G4的示例。 Cs1,Cs2,Cs3和Cs4是组成该网络的走线电容值,因此G1输出引脚的总电容=G2单元的输入电容+G3单元的输入电容+G4单元的输入电容+G1单元的输出电容+ Cs1+Cs2+Cs3+Cs4 。这个值就是G1单元进行电平切换时需要充放电的电容值,因此该总电容值会影响G1单元的时序特性。

从时序角度来看,我们需要对CMOS单元建模,以帮助我们分析通过该单元的时序。每个输入引脚必须指定一个输入引脚电容,而大多数CMOS逻辑单元可以不包括输出引脚的引脚电容,但也可能存在输出引脚电容。

当输出为逻辑1时,输出级的上拉结构导通,并提供了一条从输出到Vdd的路径。同样,当输出为逻辑0时,输出级的下拉结构提供了一条从输出到Vss的路径。当CMOS单元切换电平状态时,切换的速度取决于输出引脚上的电容被充放电的速度。输出引脚上的电容(图2-5)分别通过上拉和下拉结构充电和放电。注意,上拉和下拉结构中的通道会对输出的充放电路径构成电阻,充放电路径的电阻是决定CMOS单元速度的主要因素。上拉电阻的倒数称为单元的输出高电平驱动(output high drive)。输出上拉结构越大,上拉电阻就越小,即单元的输出高电平驱动就越大,较大的输出结构也意味着该单元的面积较大。而输出上拉结构越小,单元的面积就越小,其输出高电平驱动也就越小。上拉结构的相同概念可用于下拉结构,下拉结构决定了下拉路径的电阻值以及输出低电平驱动(output low drive)。通常,单元的上拉和下拉结构具有相似的驱动强度。

输出驱动决定了可以驱动的最大电容负载,最大电容负载又决定了扇出的最大数量,即可以驱动多少个其他单元。较高的输出驱动对应较低的输出上拉/下拉电阻,这使单元可以在输出引脚上对较大的负载进行充电和放电。

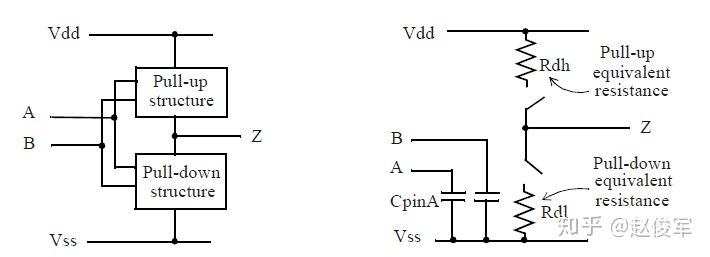

下图2-6是CMOS单元的等效抽象模型。该模型的目的是抽象单元的时序行为,因此仅对输入级和输出级进行建模,此模型无法捕获单元的固有延迟或电学行为。

CpinA是单元在输入A上的输入引脚电容;Rdh和Rdl是单元的输出驱动电阻,可根据单元所驱动的负载确定输出引脚Z电平转换时的上升/下降时间,输出驱动电阻还确定了单元的最大扇出限制。

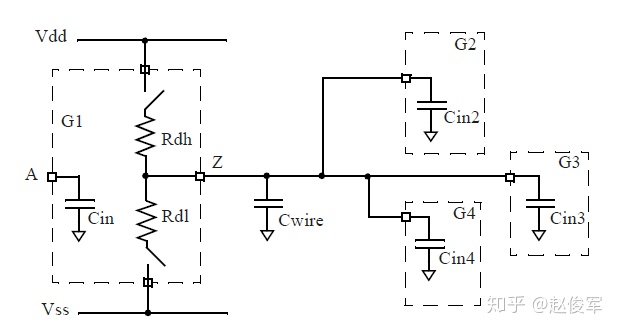

图2-7与图2-5具有相同的网络,但使用等效模型表示了CMOS单元:

-

(C_{wire} = C_{s1}+C_{s2}+C_{s3}+C_{s4})

-

输出充放电延迟 = (R_{out} cdot (C_{wire} + C_{in2} + C_{in3} + C_{in4}))

在上述表达式中,(R_{out})是(R_{dh})或(R_{dl})之一,其中(R_{dh})是上拉的输出驱动电阻,(R_{dl})是下拉的输出驱动电阻。

2.3 电平切换波形

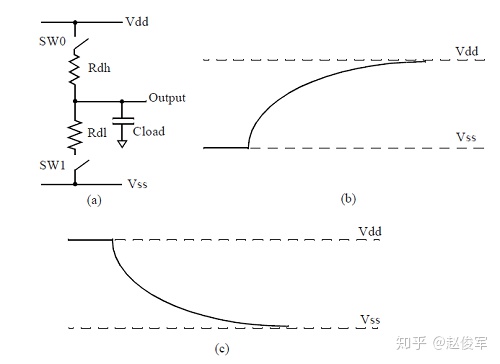

如图2-8(a)所示,通过按下SW0开关将电压施加到RC网络时,输出将变为逻辑1。假设还未按下SW0时输出为0V,则输出电压的变化由以下公式表示:

该上升的电压波形如图2-8(b)所示。乘积(Rdh * Cload)称为RC时间常数(RC time constant),该值与输出的过渡时间有关。

断开SW0开关同时按下SW1开关,输出就会从逻辑1变为逻辑0,输出电压的变化如图2-8(c)所示。输出电容通过按下的SW1开关放电,这种情况下的电压变化由以下公式表示:

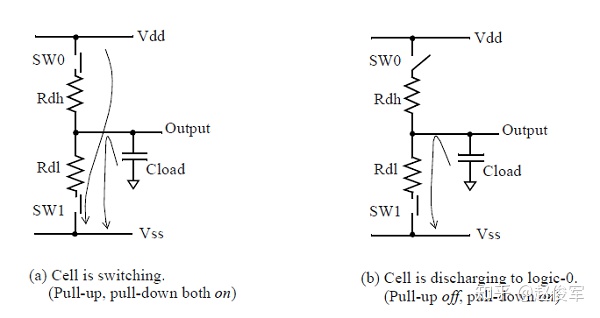

在CMOS单元中,由于PMOS上拉晶体管和NMOS下拉晶体管在短时间内会同时导通,因此输出的充放电波形不会像图2-8的RC充放电波形那样。 图2-9显示了在CMOS反相器单元内,从逻辑1到逻辑0输出切换时各个阶段的电流路径。图2-9(a)显示了当上拉和下拉结构同时开启时的电流流动。随后,上拉结构关闭,电流流向随即如图2-9(b)中所示。输出达到最终状态后,由于电容Cload已完全放电,因此不再有电流流动。

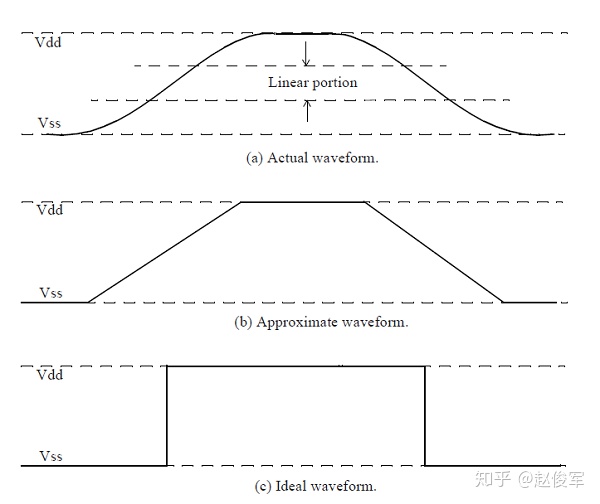

图2-10(a)是CMOS单元输出级的典型波形,请注意观察过渡波形如何逐渐朝向Vss和Vdd弯曲,且波形的线性部分位于中间位置。

在本文中,我们将使用如图2-10(b)所示的简化版来描绘一些波形,简化版的近似波形也是具有一定过渡时间(transition time)的波形,过渡时间是指从一种逻辑状态过渡到另一种逻辑状态所需的时间。图2-10(c)是过渡时间为0的波形,即理想波形。我们将在本文中交替使用(b)(c)这两种形式的波形来解释一些概念,但我们一定要清楚,实际上每个波形都有(a)那样的真实的边缘特性。

2.4 传播延时

考虑一个CMOS反相器单元及其输入和输出波形,单元的传播延时(propagation delay)是由电平切换波形上的某些测量点定义的。使用以下四个变量定义这些测量点:

输入端口下降沿的阈值点

input_threshold_pct_fall:50.0;

输入端口上升沿的阈值点

input_threshold_pct_rise:50.0;

输出端口下降沿的阈值点

output_threshold_pct_fall:50.0;

输出端口上升沿的阈值点

output_threshold_pct_rise:50.0;

以上这些变量是用于描述单元库(cell library)的命令集里的一部分。 这些阈值的单位是Vdd或电源的百分比,对于大多数标准单元库,通常将50%阈值用于计算延时。

上升沿是指从逻辑0到逻辑1的跳变,下降沿是从逻辑1到逻辑0的跳变。

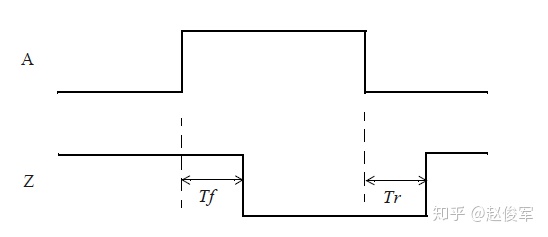

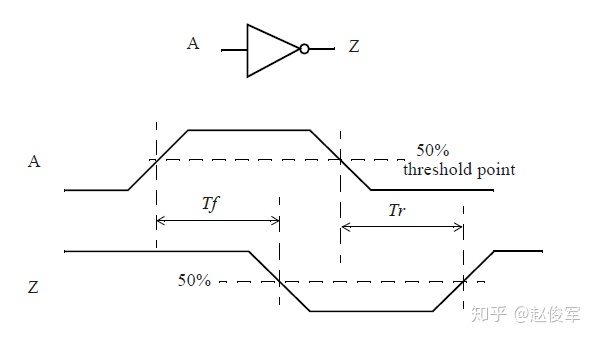

假设有一个CMOS反相器单元,其输入输出管脚的波形如图2-11所示,传播延时是指如下两个值:

1.输出下降沿延时(output fall delay):Tf

2.输出上升沿延时(output rise delay):Tr

通常,这两个值是不相等的,上图2-11也展示了这两个传播延时值是如何测量的。

若使用理想波形来看,则传播延时将仅仅是两个边沿之间的延迟,如图2-12所示: