EDK实用实例之LED

目的:

初学EDK,发现对于高版本的ISE软件,几乎没有比较好的中文教程,对于使用EDK来创建工程和试验整个流程有很大的难度,特此写下我自己的实验流程,以供像我一样想学习EDK的更多的朋友能更好的入门。

实验环境:

软件:Xilinx ISE Design Suite 12.4

板卡:Xilinx SP601开发板

实验内容:

使用Xilinx Platform Studio创建MicroBlaze最小系统,并添加软件工程,驱动XPS中创建的最小系统工作。本次实验主要是驱动开发板上的LED按顺序点亮,然后再依次熄灭。

实验步骤:

第一步:XPS中创建MicroBlaze系统。

1、 打开XPS软件

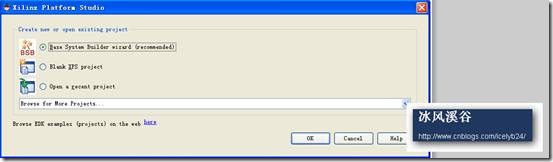

2、 选择Base System Builder Wizard,点击OK。

3、 选择工程保存的路径,填写工程名。

点击OK。稍等片刻。

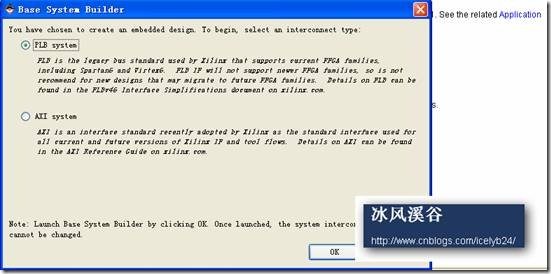

4、 选择总线类型,本次实验选择PLB总线。点击OK后,稍等片刻,进入软核设置界面。

此处PLB总线是Xilix以前的总线类型,现在新出的总线类型为AXI总线,Xilinx以后的总线类型都会成为AXI,感兴趣的朋友可以自己去了解,本次实验还是基于原来的PLB总线。

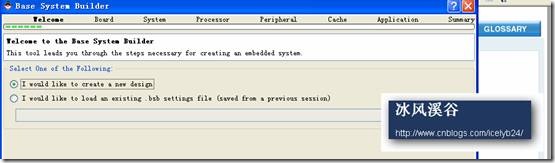

5、 选择新建一个Design,即选择I would like to creat a new design.点击next,进入板卡选择。

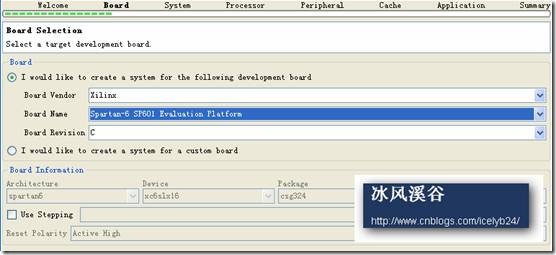

6、 选择板卡型号。此处可以选择Xilinx出的开发板,或者自己做的开发板。无论是哪种板子,请注意请选择正确你使用的FPGA型号,封装等信息。此处选择我们本次实验用的板子SP601,点击next,进入系统设置。

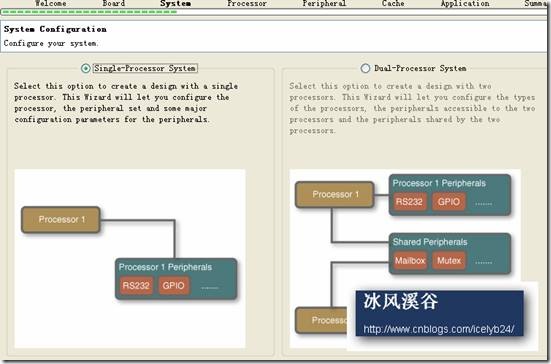

7、 选择单处理器或者双处理器,本次实验为简单的流水灯实验,单处理器即可,点击next,进入系统频率设置。

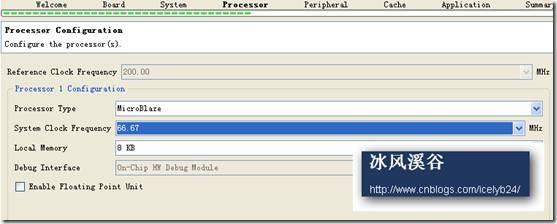

8、选择所需的时钟频率,此处不用使用浮点运算,所以不用选择Enable Floating Point Unit。点击next进入外设的IP核选择界面。

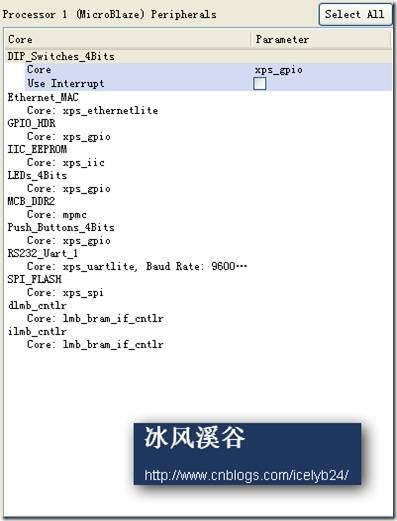

9、 系统默认添加了SP601开发板上的外设所需的IP,

在此,我们只需选择我们需要的外设,其余的外设在本次实验中没有用到,所以可以不用选择,我们通过remove将其移除我们的系统,只保留我们需要的LEDs_4Bits。

在此,我们只需选择我们需要的外设,其余的外设在本次实验中没有用到,所以可以不用选择,我们通过remove将其移除我们的系统,只保留我们需要的LEDs_4Bits。

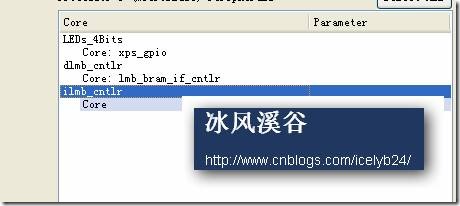

其中dlmb_cntlr为数据总线控制器的IP,ilmb_cntlr为指令总线的控制器的IP,为系统默认加入的,不能去掉。点击next,进入catch配置。

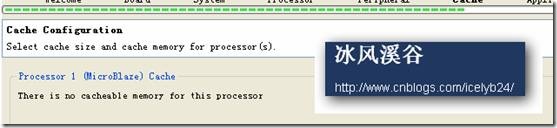

10、 进入Catch Configuration界面,本次实验不需要做修改,直接点击next,进入Applications Configuration。

11、 本次实验也不需要修改Applications Configuration,直接点击next。

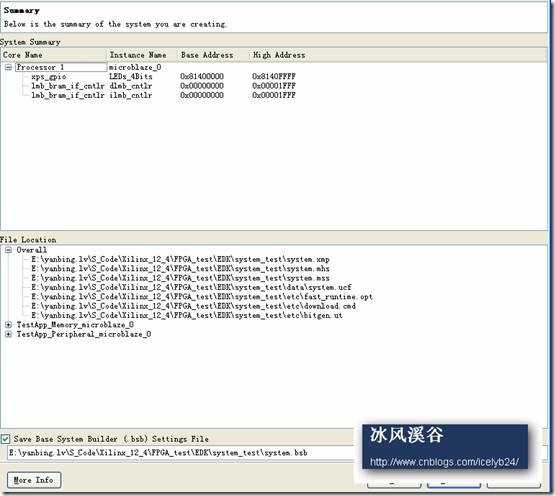

12、 进入Summary,查看系统信息。

点击finish,完成系统配置。

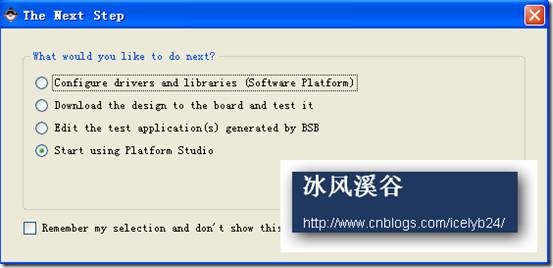

13、 因为工程软件程序还没有编写,所以选择Start using Platform Stdio,进入Platform Stdio中,进行后续的操作。

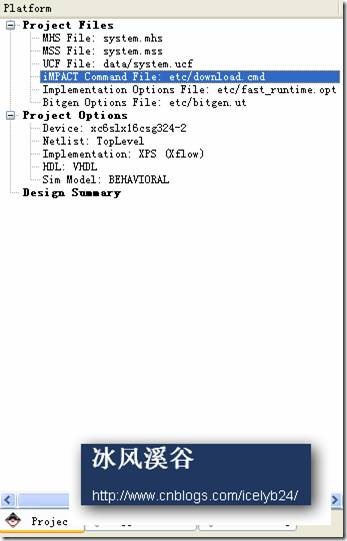

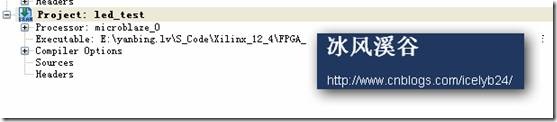

14、 查看硬件工程中生成的一些文件,点击Project,如下图。

在此我们需要注意的文件有:mhs文件、mss文件、ucf文件、cmd文件。

msh文件是对一硬件的描述,包括外围接口配置,MicroBlzae配置,以及其他的器件的配置等。

mss文件是对MicroBlaze软核的描述,主要是对外设的驱动程序的描述,包括它们的版本之类的。

ucf文件是对FPGA的约束文件和引脚分配。(本例中我们采用的是Xilinx的开发板,所以在生成工程后,具体的外设引脚的分配已经都分配好了,如果是自己做的板子,需要对具体的外设按照板子原理图进行引脚分配)

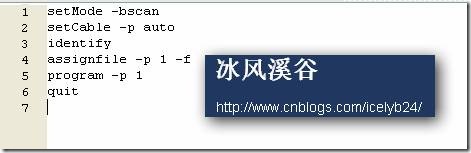

cmd文件是和bitstream的下载有关的问价,里面需要修改FPGA在Jtag链中的位置信息。如下:

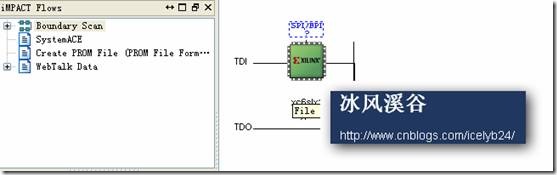

第4行和第5行的1表示的是FPGA下载的位置。因为本次实验使用的SP601的FPGA的位置是第一位,所以默认即可。如果是其他的板子或者自己做的板子,就需要查看FPGA的下载位置,如果是第二位,则需将第4第5行的1修改成2即可。具体修改的数字,以具体板子来定。可以使用Impact中的Boundary Scan进行查看,入下图:

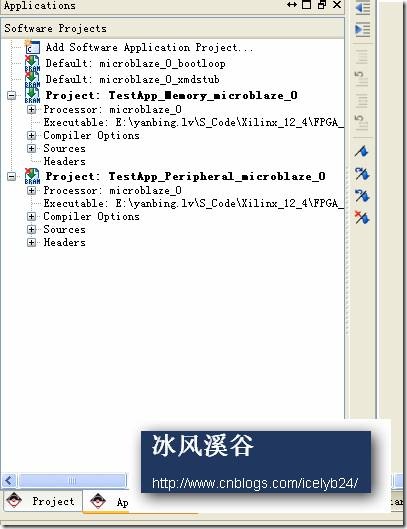

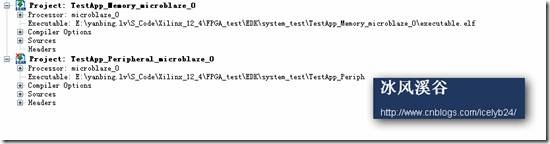

14、点击Applications,

可以看到在Applications中已经有了两个软件的project,这两个是系统在生成MicroBlaze系统的时候XPS软件生成的软件系统,用来测试我们的硬件工程的。在此我们需要重新添加我们自己的软件程序。具体介绍见第二部分。在此我们可以看到

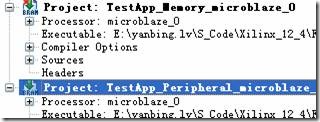

其中第二个工程![]() 有个红色的小叉,这是因为在软件默认在Applications中默认只有一个软件工程被激活,我么可以右键选择需要激活的软件工程选择

有个红色的小叉,这是因为在软件默认在Applications中默认只有一个软件工程被激活,我么可以右键选择需要激活的软件工程选择

选择Mark to Initialize BRAMs,即可激活选中的软件工程,而之前激活的软件工程则会出现一个红色的小叉,用于表示当前未被激活。

自此,我们的硬件系统就全部创建好了。

第二部分:添加软件工程

1、 选择Applications,双击Add Software Application Project…

2、 输入软件工程的名字。

在此我们命名为led_test。

3、 激活所建的工程,方法在第一部分第14步中有讲解。

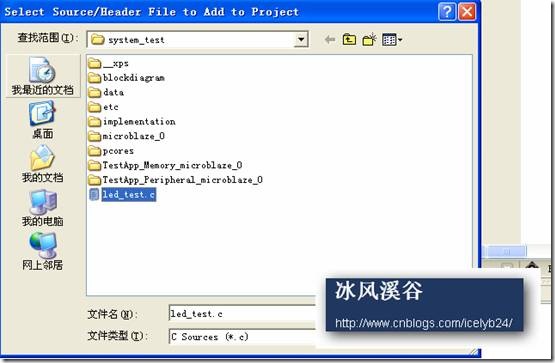

4、 右键点击Sources选择添加C语言代码,此处我选择添加之前准备好的C语言代码,(本人C语言不是很好,此处只是选择了一个例子程序并做了修改,通过编译下载后可以完成此次实验,如果哪位朋友C语言比较好,可以编写更好的程序,在此不对C代码做过多深究)。

5、 添加好了C程序后,就需要开始编译了。此处编译需要分软件编译和之前的硬件系统编译两种。在此我们先做软件编译,选择Software,点击Generate Libraries and BSPs。等编译完成后再点击Build All user Applications。

编译没有问题了,则说明软件程序已经编译成功。

6、 编译硬件工程。选择Hardware,点击Generate Netlist。完成后选择Hardware,点击Generate Bitstream,生成下载的bit文件。

第三部分:下载程序

连接好FPGA开发板,选择Device Configuration,点击Updata bitstream。编译完成后就可以下载了,点击Download Bitstream。下载结束后就可以看到SP601的板子上面的四个led会依次点亮,形成流水灯。

后记:

本实验教程是Xilinx Spartan-6 Sp601开发板上实现的EDK的实验,使用的软件的版本是12.4。如果需要在Spartan-3E的板子或者在其他的自己设计的板子上使用的时候,软件程序和其他的一些设置需要做修改,请读者注意。希望我的这点收获能够给学习EDK的其他的朋友带去一些帮助。文章中还有不足之处,希望学习的朋友发现了问题能够提醒我,以供文档的修改。

附件:工程文件:http://fpga-study-information.googlecode.com/files/system_test.rar

E-mail:ice_lyb@163.com

![clip_image002[4] clip_image002[4]](https://images.cnblogs.com/cnblogs_com/icelyb24/201103/201103260005501848.jpg)