1. 概念

存储器(Memory)是计算机系统中的记忆设备,用来存放程序和数据;

目前主要采用半导体器件和磁性材料作为存储器的存储介质

存储器中最小的存储单位就是一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储元

存储单元由若干个存储元组成,存储器则由若干存储单元组成

每个存储单元可存放一个字节(按字节编址),其位置都有一个编号(即地址),一般用十六进制表示

存储器的存储容量为所有存储单元可存放数据的总和

比如一个存储器的地址码由20位二进制数(即5位十六进制数)组成,则可表示2^20,即1M个存储单元地址

每个存储单元存放一个字节,则该存储器的存储容量为1MB

按用途,存储器可分为主存储器(内存)和辅助存储器(外存)

外存通常是磁性介质或光盘等,能长期保存信息

内存指SOC上的存储部件,用来存放当前正在执行的数据和程序,但仅用于暂时存放;关闭电源或断电,数据会丢失

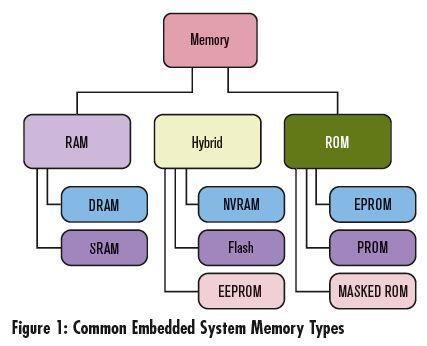

按存储器的读写功能分为只读存储器(ROM)和随机读写存储器(RAM)

ROM: 存储的内容是固定不变的,只能读出而不能写入的半导体存储器

RAM: 既能读出又能写入的半导体存储器,但是断电数据丢失

TIP: Hybrid Memory指混合存储器,结合了ROM和RAM的长处,不仅具备可读写的性能,同时具备非易失性(断电数据不会丢失).

SRAM: 静态随机存储器,不需要刷新电路,数据也不会丢,速度快,但是价格昂贵,容量小

DRAM: 动态随机存储器,需要刷新电路,列地址可复用,容量大

SDRAM: 同步动态RAM,需要刷新,速度较快,容量大

DDR SDRAM: 双(或多)通道同步动态RAM,需要刷新,速度快,容量大

TIP: SDRAM的同步指的是数据的读写需要时钟来同步

2. SDRAM

2.1 介绍

在嵌入式产品,内存用的都是SDRAM

2.2 地址计算

内存是按字节编址的,所以单位是字节,1字节等于8位的

2^10 = 1024 = 1KB 2^16 = 1024*64 = 64KB 0000H ~ FFFFH( 10000H) 2^20 = 1024*1024 = 1MB 0 0000H ~ F FFFFH( 10 0000H) 2^32 = 1024*1024*4096 = 4GB 0000 0000H ~ FFFF FFFFH(10000 0000H)

其中, 内存容量 = 末地址 - 首地址 + 1

以SRAM 6264芯片为例:

该系列芯片的容量为8K*8bit

地址线至少有13根(8K = 8192 = 2^13);数据线有8根(8bit)

存储器芯片的地址范围为: 0000H(首地址)~1FFFH(末地址)

8K即 2^12(???), 转换为16进制为0x2000(内存容量)

2.3 取址和容量

~1 bank块地址---定位逻辑块

~2 行地址和列地址---定位存储单元,共同定义了多少个存储单元

~3 容量定义: 地址数(Address Width) * 位宽(Data Bus Width) * 存储块(Bank)

SDRAM容量的常用表示方法

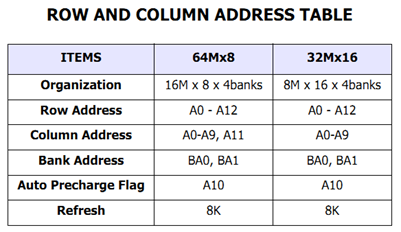

H5DU5162ETR-E3C --- 512Mbit, 8M x 16bit x 4banks

2.4 寻址原理

SDRAM是由多个逻辑Bank组成;每一个Bank是一个存储阵列,就如同一张表格,有行列之分

当访问某个存储单元(某字节)时,先指定行(Row),再指定列(Column),这就是内存芯片寻址的基本原理

寻址时就要先确定是哪个Bank,然后再在这个选定的Bank中选择相应的行与列进行寻址

可见对内存的访问,一次只能是一个Bank工作,每次与CPU交换的数据就是Bank存储阵列中一个"存储单元"的容量

SDRAM一次传输的数据量就是芯片位宽, 那么这个存储单元的容量就是芯片的位宽(也是Bank的位宽)

SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写地址分两次输入到芯片中,每一次由同一组地址线送入,两次送入到芯片上去的地址分别称为行地址和列地址, 它们被锁存到芯片内部的行地址锁存器和列地址锁存器

详细可参考<SDRAM的工作原理>

存储单元数量 = 行数*列数*Bank数,而每个存储单元包含的容量即位宽,以H5DU5162ETR-E3C为例

以8M*16bit*4banks(512Mbit)为例

行数 = A0 ~ A12 (13)

列数 = A0 ~ A9 (10)

8M = 2^13 * 2^10

容量 = 8M * 4(banks) * 16bits = 512MBits = 64MBytes

2.5 引脚信号

SDRAM引脚分为以下几类

控制信号:包括片选、时钟、时钟使能、行列地址选择、读写有效及数据有效

地址信号:时分复用引脚,根据行列地址选择引脚,控制输入的地址为行地址或列地址

数据信号:双向引脚,受数据有效控制。

下图为MT48LC4M4A1 16MB SDRAM引脚图如下

引脚定义:

| 引脚 | 功能 |

| A0 ~ A10 | 地址输入引脚 |

| DQ0 ~ DQ15 | 数据输入输出接口 |

| CLK | 时钟信号输入引脚 |

| CKE | Clock Enable, 高电平时有效. 当这个引脚处于低电平期间, 提供给所有bank预充电和刷新的操作 |

| /CS | Chip Select, 片选. 一般用于多存储芯片架构, 选择进行存取操作的芯片 |

| /RAS | Row Address Select, 行地址选择 |

| /CAS | Column Address Select, 列地址选择 |

| /WE | Write Enable, 写使能信号 |

| BA | Bank地址输入信号引脚, BA信号决定了由激活哪一个bank、进行读写或者预充电操作 |

| DQM | 主要用于屏蔽输入/输出, 功能相当于/OE引脚(Output Enable) |

| VDDQ | DQ供电引脚, 可以提高抗干扰强度 |

| VSSQ | DQ供电接地引脚 |

| VSS | 芯片供电接地引脚 |

| VDD | 芯片供电引脚, 提供+3.3V ±0.3V |

| NC | 空引脚 |

TIP: 前面标有“/”或者“#”标记的表示在低电平下有效

3. FLASH

3.1 介绍

Flash,即Flash memory,通俗的叫法是"闪存",全名称Flash EEPROM Memory.

Flash存储器结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还可以快速读取数据(NVRAM),使数据不会因为断电而丢失

按照内部访问接口不同,Flash分为NOR Flash和NAND Flash两种

NOR Flash: 带有SRAM接口,可在芯片内执行(XIP,eXecute In Place),程序可以直接在Flash上运行

NAND Flash: 共用地址和数据总线,需要额外联结一些控制的输入输出,要完成地址和数据的传输就必须让这些信号轮流传送;其读取是以一次读取一块的形式来进行的,通常是一次读取512个字节,程序不能直接在NAND Flash上运行

3.2 相同点和区别

NOR Flash和NAND Flash的相同点如下

~ 均是非易失存储器,向芯片写数据必须先将芯片中对应的内容清空,然后再写入,也就是通常说的“先擦后写”;只不过NOR只用擦写一个字,而NAND需要擦写整个块

~ 闪存的读写操作不仅仅是一个物理操作,实际上在闪存上存放数据必须使用算法实现,这个模块一般在驱动程序的MTD (Memory Technology Drivers)模块中或者在FTLZ (Flash Translation Layer)层内实现,具体算法和芯片的生产厂商以及芯片型号有关系。

NOR Flash和NAND Flash的区别如下

~ NOR是随机存储介质,存储密度较低,用于数据量较小的场合;NAND是连续存储介质,存储密度高,适合存放大的数据

~ NOR以字节或字为基本单位,以块为擦除单位,以字节或字读写(FLASH中的写也称为编程);NAND基本存储单元是页,并以页为单位读写数据,而以块为单位擦除数据

~ NOR写入速度较慢,读取速度快;NAND写入和擦除速度快,读取慢

~ NOR的可靠性要高于NAND,由于串联的架构,NAND的晶体管之间更容易造成影响,使逻辑0变成逻辑1,即位翻转(Bit-Flipping),这就需要动用EDC/ECC(错误检测码/错误修正码)来进行校正;另外,NAND在使用中还存在着坏块管理的问题

3.3 NAND Flash

3.3.1 概念

NAND Flash中有一些基本概念OOB,ECC和BBT

~ OOB

NAND Flash中每一页对应一块区域,用于存放校验的ECC数据和其他一些信息(如文件系统相关数据和坏块信息)

对于这个区域

在Linux MTD中,被称为OOB(Out of Band)

在Datasheet中,被称为Spare Area

在ID的解释中也叫做Redundant Area

TIP: 通常把每个块第一个page的spare area的第6个byte用来标记该块是否为坏块

~ ECC

ECC即Error detection and correction,是一种用于NAND Flash的差错检测和修正算法

在OOB中有存储ECC校验和,能纠正1个比特错误和检测2个比特错误

~ BBT

BBT,即Bad block table,即坏块表,用来进行NAND Flash坏块管理

各厂家对NAND的坏块管理方法都有差异

如果专门用NAND做存储,会把BBT放到block 0(即第0块),因为第0块一定是好块

如果NAND本身被用来boot,那么第0块就要存放程序,不能放BBT了;

有的厂商把BBT放到最后一块,当然,这一块坚决不能为坏块

BBT的大小跟NAND大小有关,NAND越大,需要的BBT也就越大

tip: OOB是每个页都有的数据,里面存的有ECC等信息, 而BBT是一个FLASH才有一个

关于NAND Flash的坏块,可以参考<NAND bad blocks>

3.3.2 特性

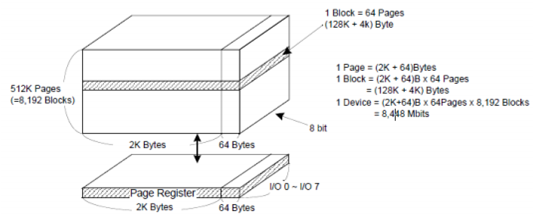

下图是一张NAND Flash示意图如下

NAND Flash的数据存储分层为:

1 Device = 4096 块(Block)

1 Block = 32 页(Page)

1 Page = 528 字节(Byte) = Data(512 Byte) + OOB(16 Byte)

在每一页中,最后16字节(OOB)用于NAND Flash命令执行完后设置状态用,剩余512字节又分为前半部分和后半部分

可以通过NAND Flash命令00h/01h/50h分别对前半部、后半部、OOB进行定位;通过NAND Flash内置的指针指向各自的首地址

存储操作特点是擦除操作的最小单位是块,另外每一位只能从1变为0,而不能从0变为1

所以在对其进行写入操作之前一定要将相应块擦除(擦除即是将相应块的位全部变为1, 即0xFF)

OOB部分的第6字节(即第517字节)标志是否是坏块,值为FF时不是坏块,否则为坏块

除OOB第6字节外,通常至少把OOB的前3字节用来存放NAND Flash硬件ECC码

NAND Flash从技术架构上又可分为SLC, MLC和TLC

SLC: Single-Level Cell , 即1bit/cell, 速度快寿命长, 价格贵(约MLC 3倍以上的价格), 约10万次擦写寿命

MLC: Multi-Level Cell, 即2bit/cell, 速度一般, 寿命一般, 价格一般, 约3000~10000次擦写寿命

TLC: Trinary-Level Cell, 即3bit/cell, 也有Flash厂家叫8LC, 速度慢寿命短, 价格便宜, 约500次擦写寿命

NAND Flash器件使用复杂的I/O口来串行地存取数据,8个引脚用来传送控制、地址和数据信息

由于时序较为复杂,所以一般CPU最好集成NAND控制器

由于NAND Flash没有挂接在地址总线上,所以如果想用NAND Flash作为系统的启动存储器,就需要CPU具备特殊的功能

如s3c2410在被选择为NAND Flash启动方式时会在上电时自动读取NAND Flash的4k数据到地址0的SRAM中

如果CPU不具备这种特殊功能,用户不能直接运行NAND Flash上的代码,那可以采取其他方式

比如除了使用NAND Flash以外,还需要一块小的NOR Flash来运行启动代码

3.3.3 引脚信号

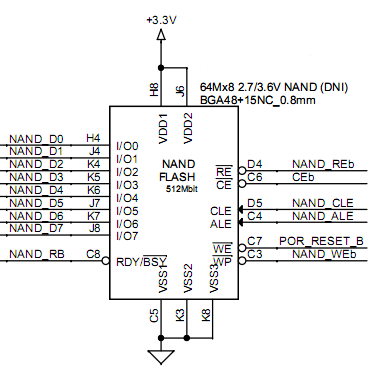

下面介绍NAND Flash的接口引脚(出自63168VX-P302)

引脚定义:

| 引脚 | 功能 |

| I/O 0-7 | 数据输入输出, 地址输入 for x8 and x16 Devices |

| I/O 8-15 | 数据输入输出 for x16 Devices, Not Here |

| ALE | Address latch enable |

| CLE | Command latch enable |

| /WE | Write enable |

| /WP | Write protect |

| /RE | Read enable |

| /CE | Chip enable |

| RDY, /BSY | Ready / Busy |

| VDD 1-2 | Power supply |

| VSS 1-3 | Ground |

一般的NAND FLASH芯片有48 PIN,实际使用时有较多NC

有的同时支持x8和x16,有的仅支持x8

而对于处理器,则需要查看其Datasheet来确定是否支持x16设备

更多NAND Flash的内容,参考<S3C2440对Nand Flash操作和电路原理(基于K9F2G08U0A)>

3.4 NOR Flash

3.4.1 接口

根据外部接口的不同NOR Flash有普通的接口和SPI接口

普通接口的NOR Flash,多数支持CFI接口,所以,一般也叫做CFI接口;

CFI接口,相对于串行的SPI接口来说,也被称为Parallel接口,并行接口;

另外,CFI接口是JEDEC定义的,所以,有的又称CFI接口为JEDEC接口。

所以,对于NOR Flash,CFI接口=JEDEC接口=Parallel接口

Parallel接口NOR Flash的引脚比较多,通常有32/44/48/56/64个(参考MX29F800CTB)

SPI接口NOR Flash针脚通常有8/16个

3.4.2 SPI

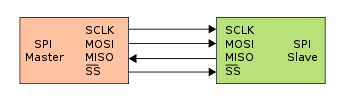

SPI(Serial Peripheral Interface),即串行外设接口

SPI总线是嵌入式设备中的一种常用的串行总线。

SPI接口一般使用4个信号线

- SCLK: 串行时钟线

- MOSI: Master输出/Slave输入数据线

- MISO: Master输入/Slave输出数据线

- /SS : 片选或称从器件使能信号, 低电平有效

更多内容可参考:

<弄懂SPI接口>

<MX25L6445E>

3.5 文件系统

Linux系统中采用MTD来管理不同类型的Flash,包括NAND Flash和NOR Flash

支持在Flash上运行的常用文件系统有SquashFS、Cramfs、JFFS2、YAFFS等

SquashFS: 只读

Cramfs: 只读

JFFS2: 可读写, 用于NOR Flash

YAFFS: 可读写, 用于NAND Flash

更多MTD相关内容, 参考<Linux MTD介绍>