计算机组成

8 存储层次结构

8.4 主存技术的发展

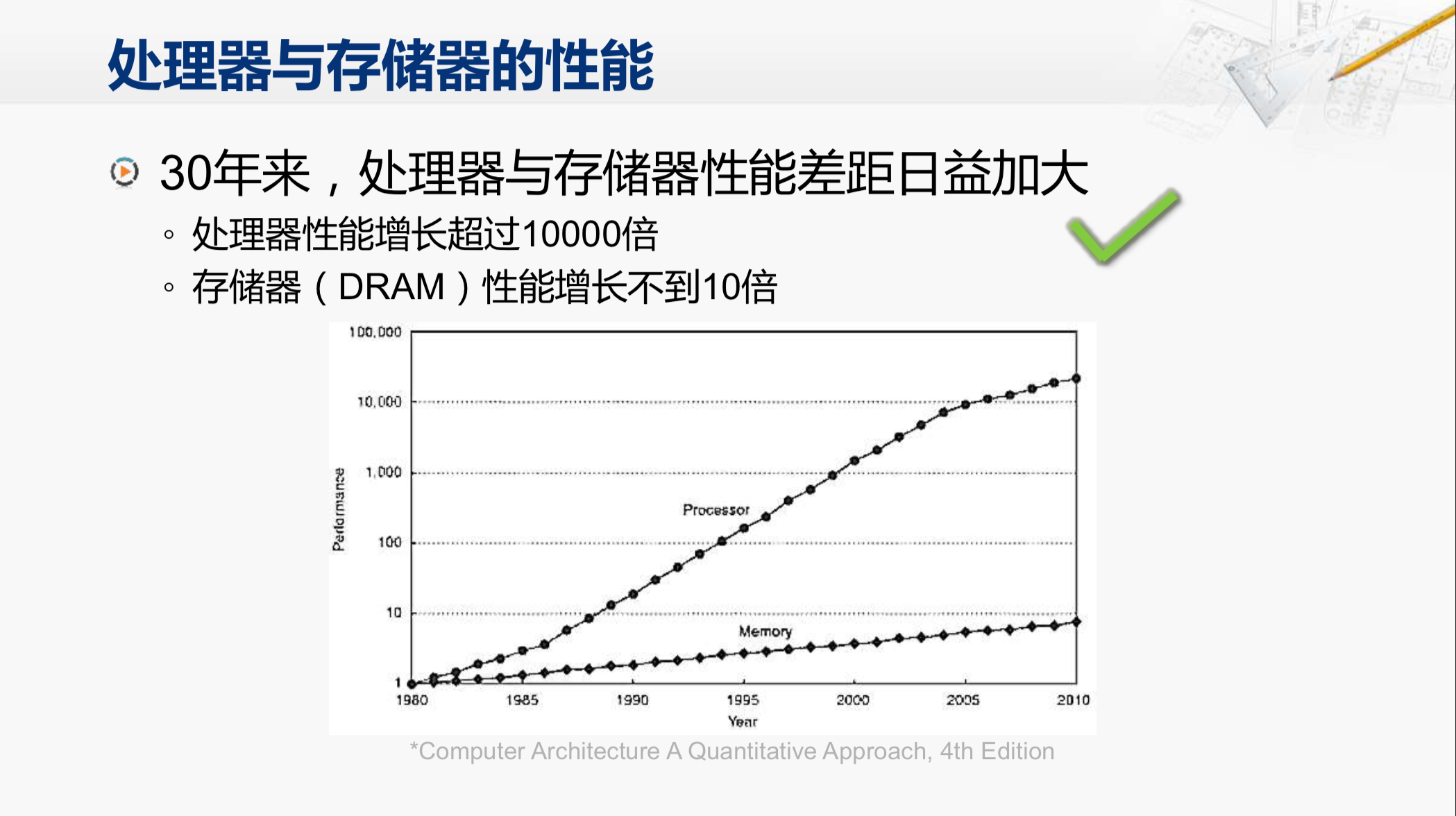

近些年来SDRAM的标准不断地升级换代,其性能也得到很大的提升。那为什么还总是说CPU和内存之间的速度差距越来越大了呢?这一节我们就来探讨这个问题。

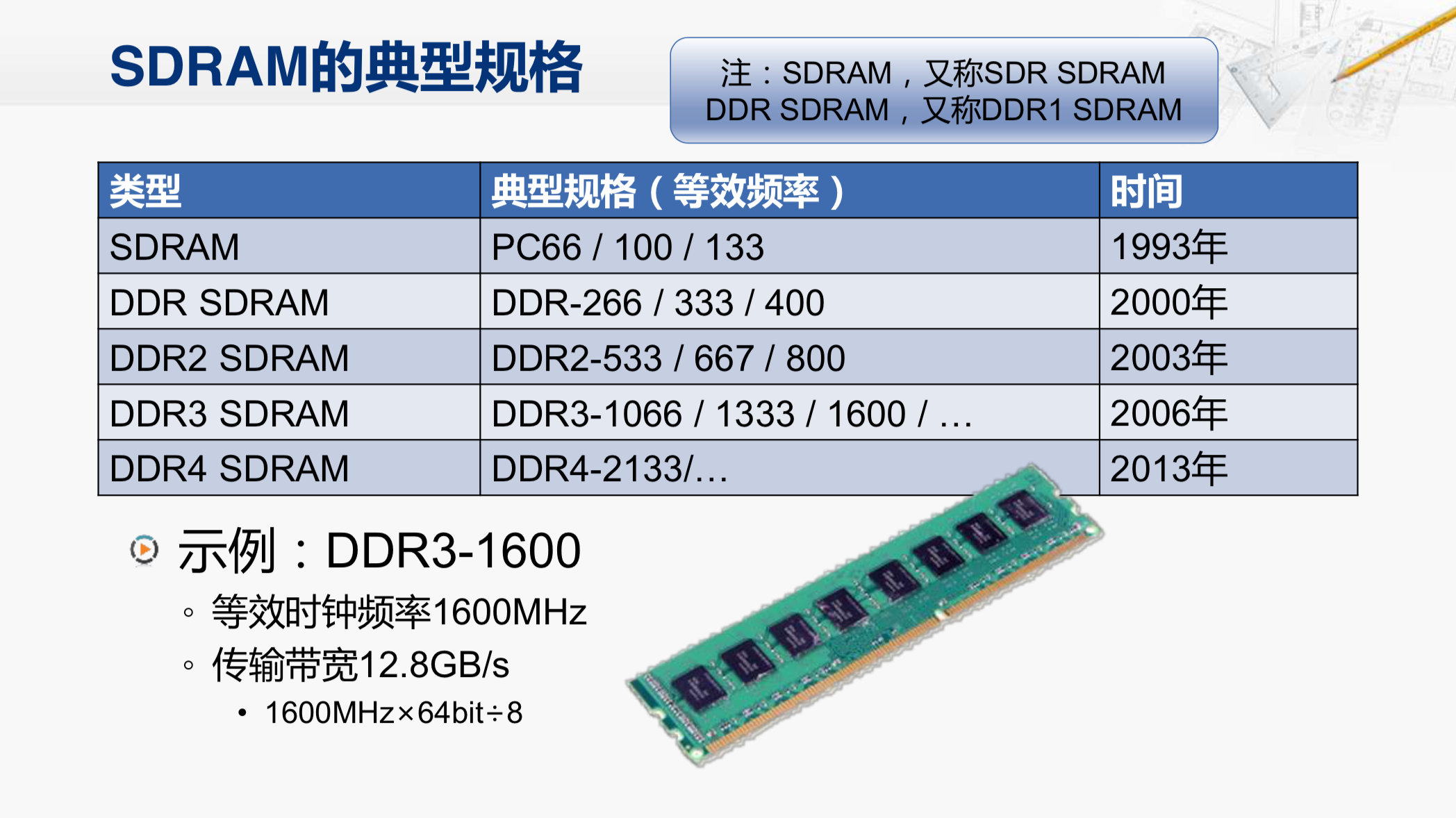

近20年来,流行的内存都采用了SDRAM的结构。需要注意的是虽然平时我们会说以前用SDRAM内存,现在用DDR内存,但这种说法是不规范的。所谓DDR内存也是SDRAM的一种,只不过接口采用了双倍数据率而已。

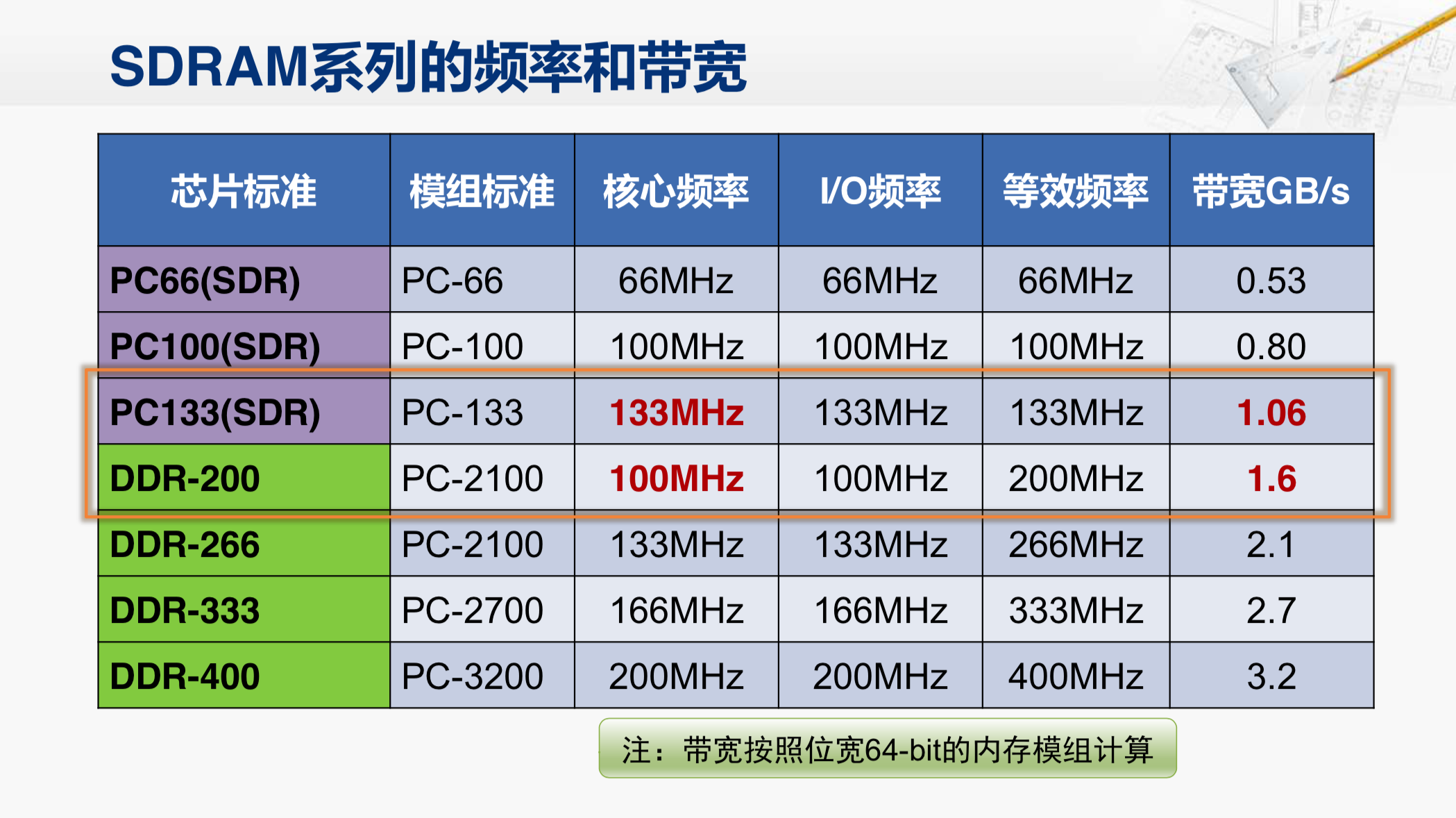

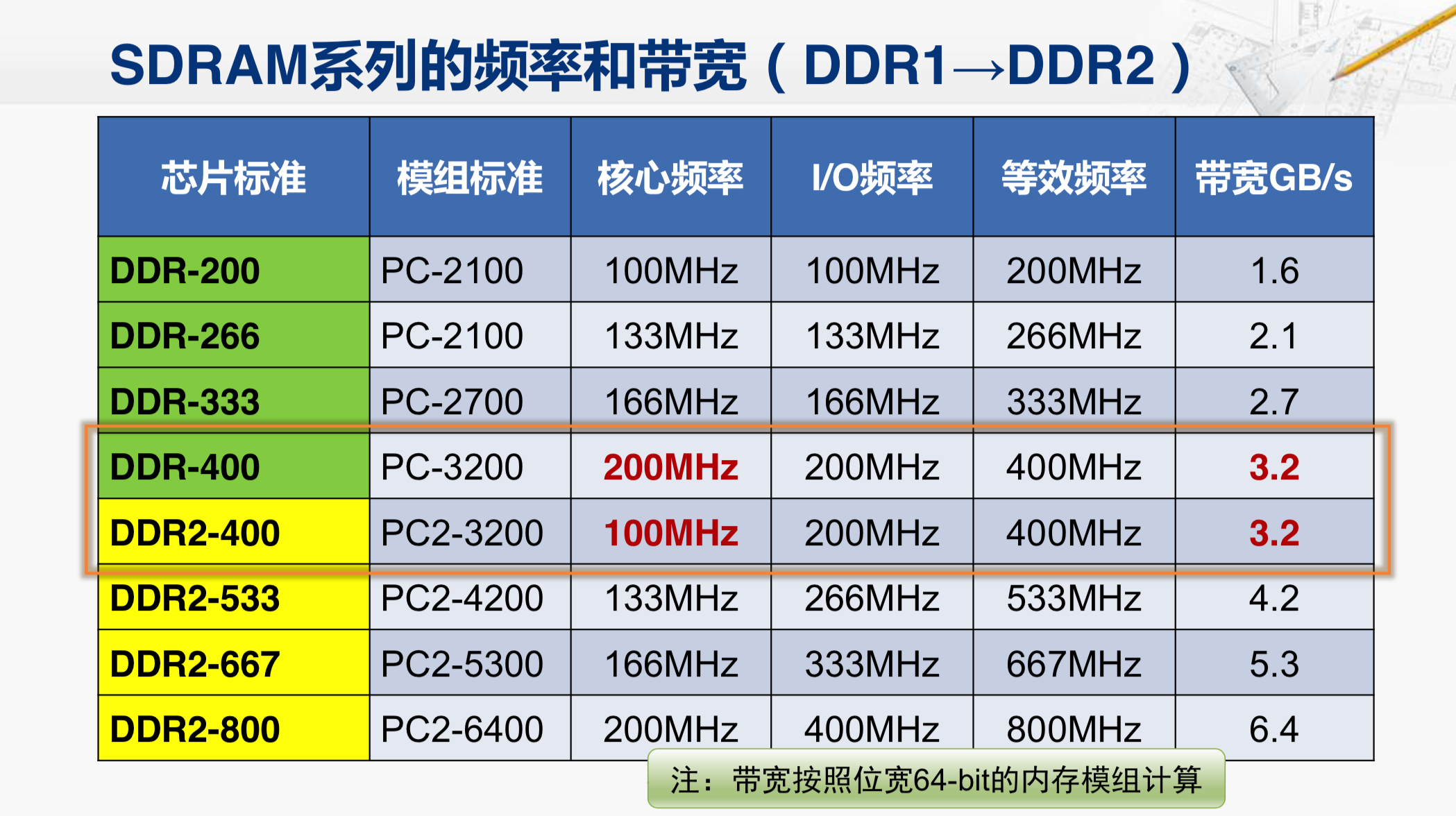

那么有了DDR SDRAM之后,如果要特指之前的SDRAM,可以说是SDR SDRAM。SDR就是单数据率的简称。而DDR之后,又有了DDR2,3,4等后续标准。为了区分明确,也把第一代的DDR称为 DDR1。这些内存规格后面带的数字,比如这里的1600,指的是内存接口的等效时钟频率。借此我们可以计算出内存的传输带宽。

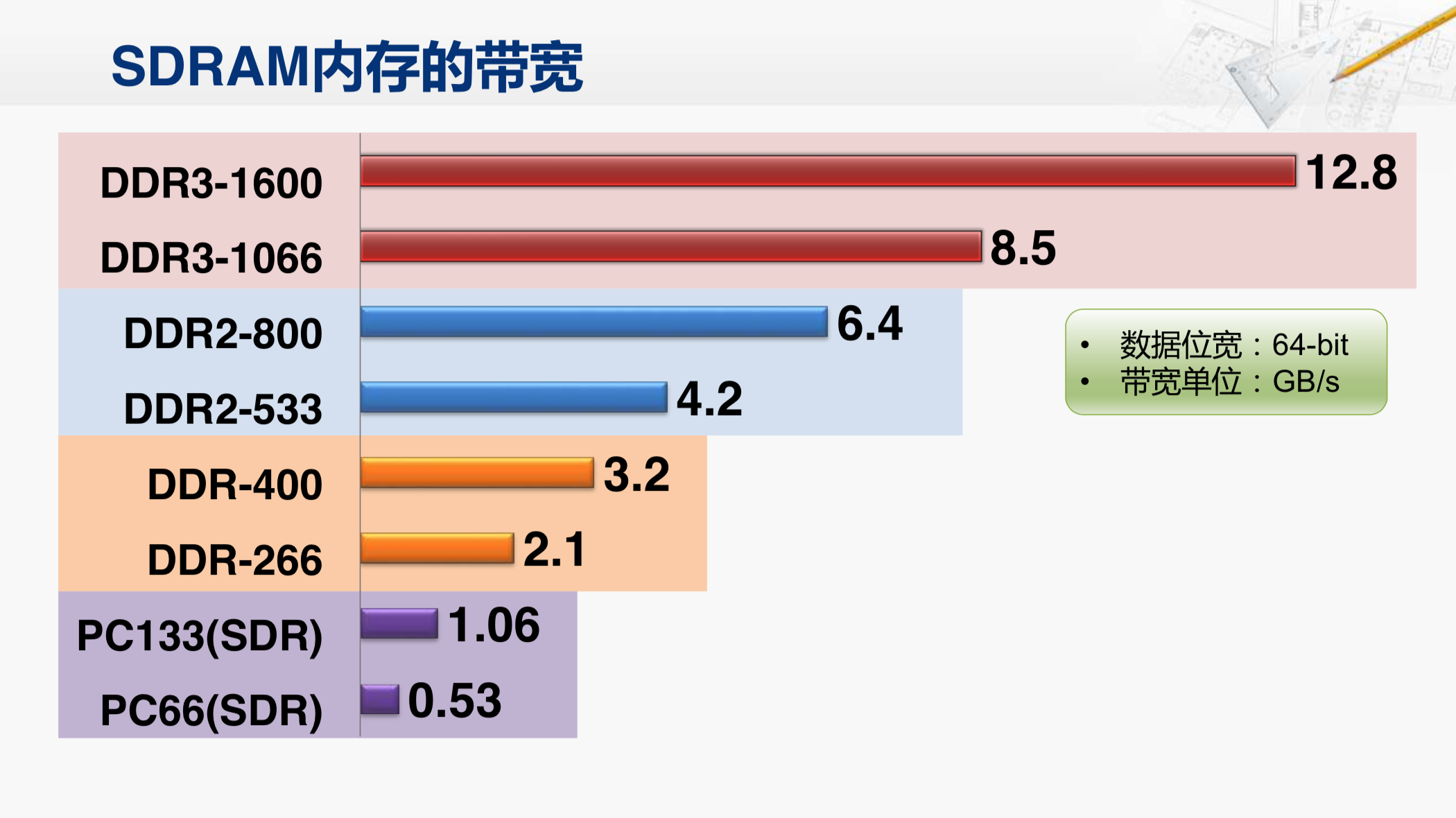

如果按照内存位宽为64比特,由此计算出的内存传输带宽,早期的 PC66 是 0.53GB/s。而到了 DDR3-1600 则达到了12.8GB/s,十几年里增长了二十倍之多。

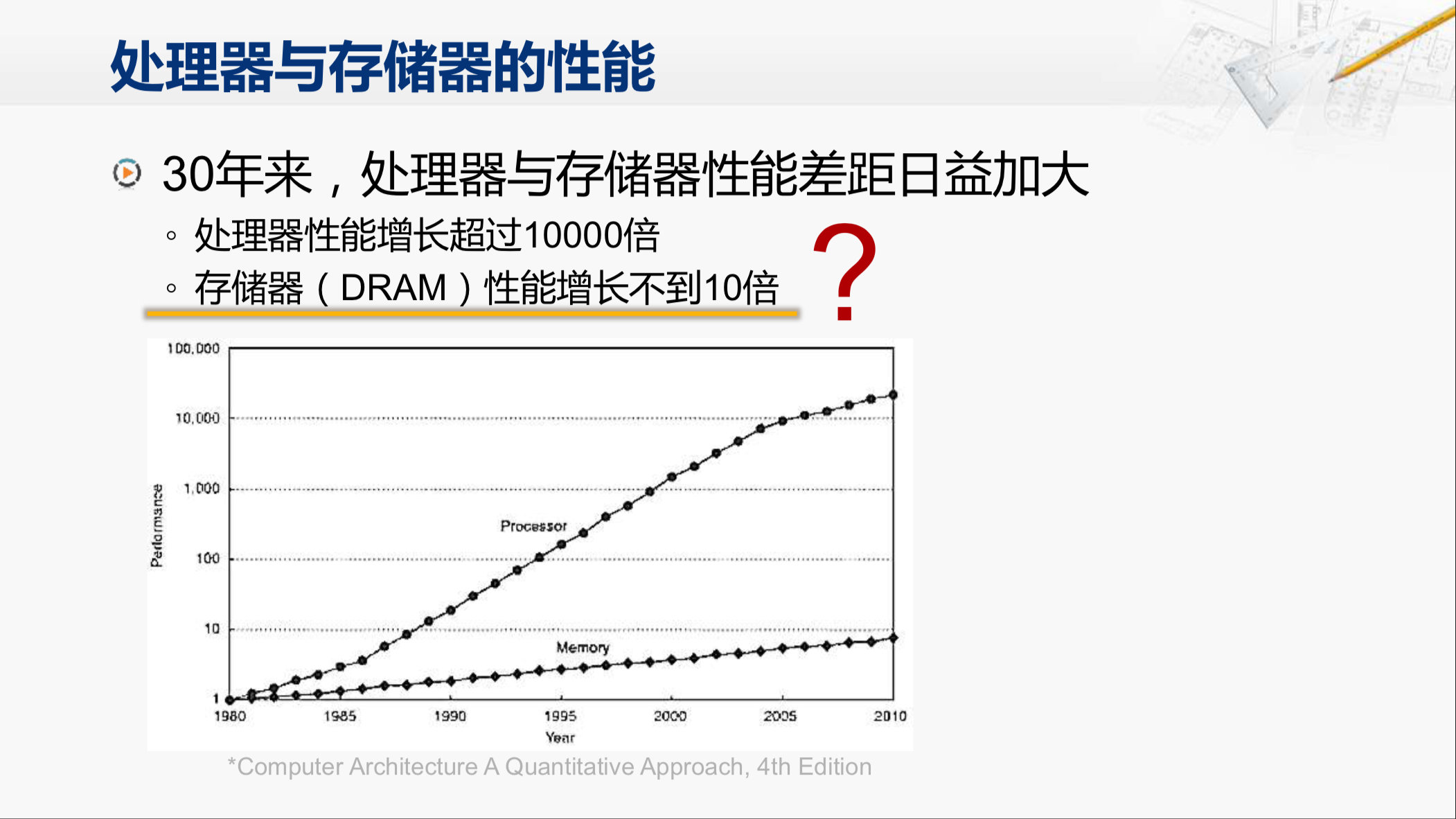

然而,很多经典教材和资料中都会提到,近几十年来,计算机处理器与存储器的性能差距日益加大,存储器性能的增长不到十倍。

那这又是怎么回事呢?这个说法是否有问题呢?

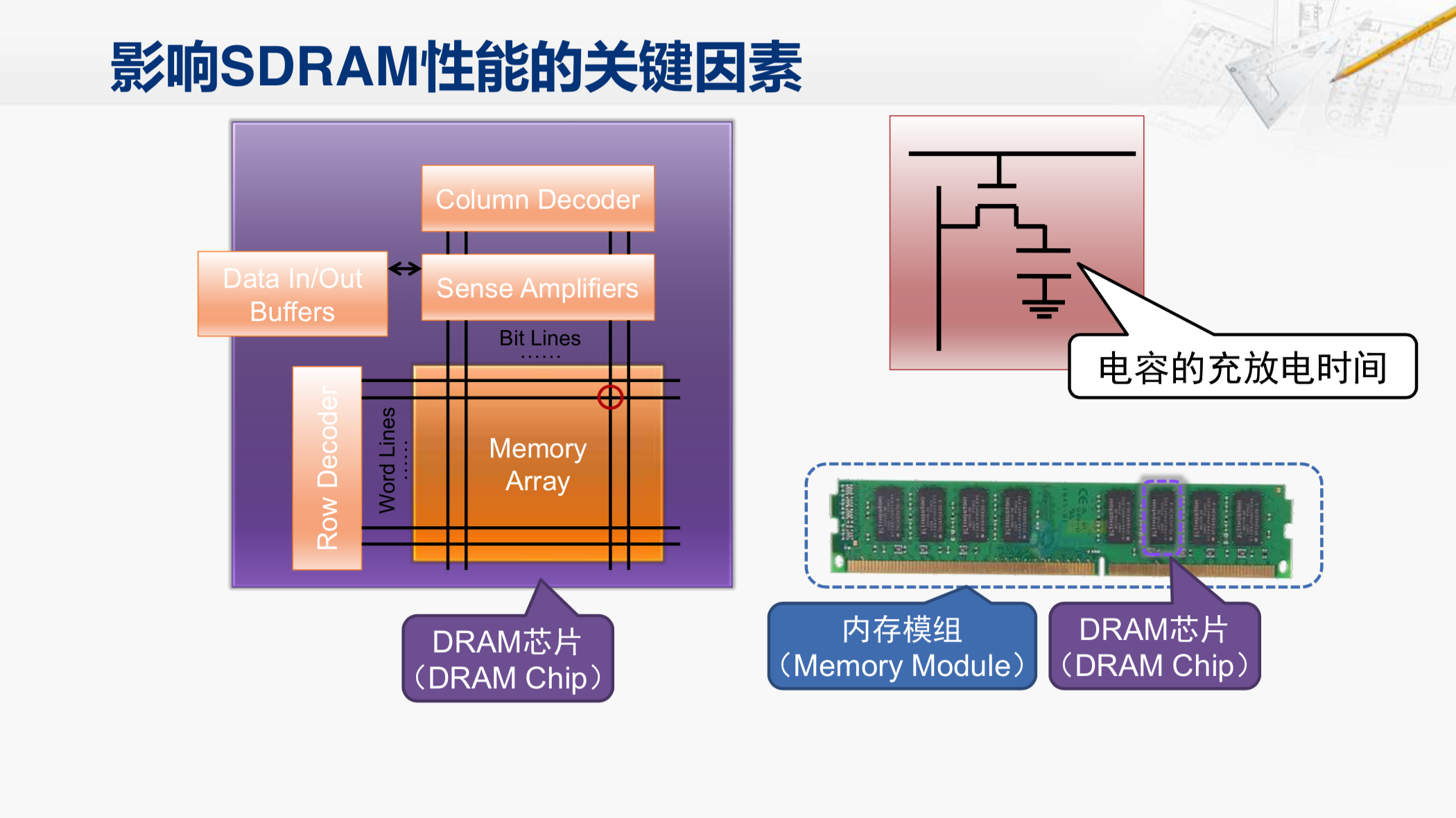

之前我们已经学习过,SDRAM的基本单元是一个电容和一个晶体管。对于SDRAM的读写最终体现在了对电容的充放电,而要减少这个电容的充放电时间,那是非常困难的。因此,在SDR SDRAM的时代,当时钟频率提升到了133MHz之后就很难进一步提升了。

那后来的DDR SDRAM又是如何提升性能的呢?

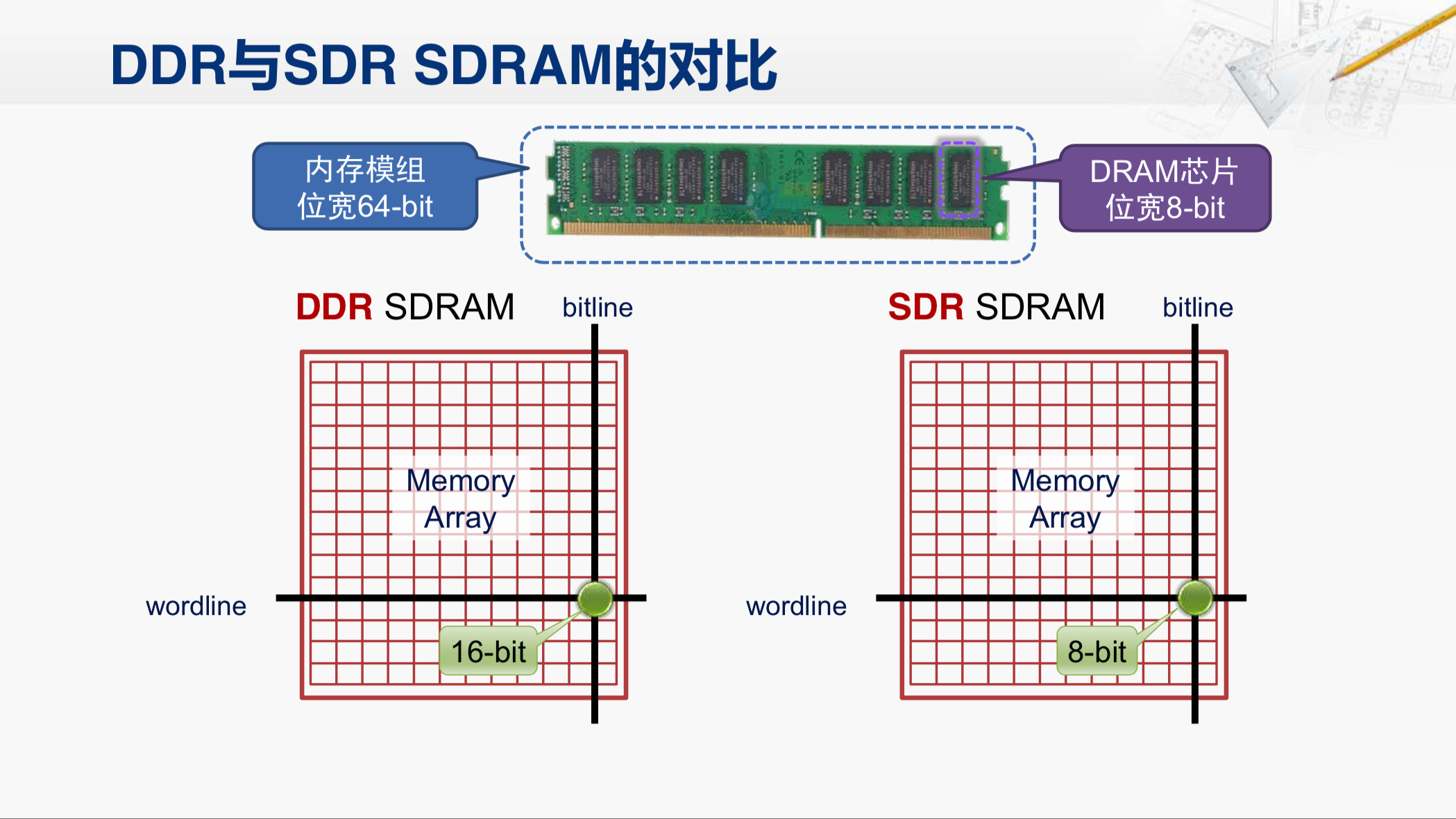

那我们就来看一看内存模组的内部结构。对于一个位宽8比特的SDR SDRAM芯片,每次访问其内部的存储阵列都会取出8比特的数据。而同样位宽的DDR SDRAM芯片,每次访问存储阵列则会取出两倍的数据量。那这16比特的数据是怎么传输的呢?这就要用到双倍数据率的概念。

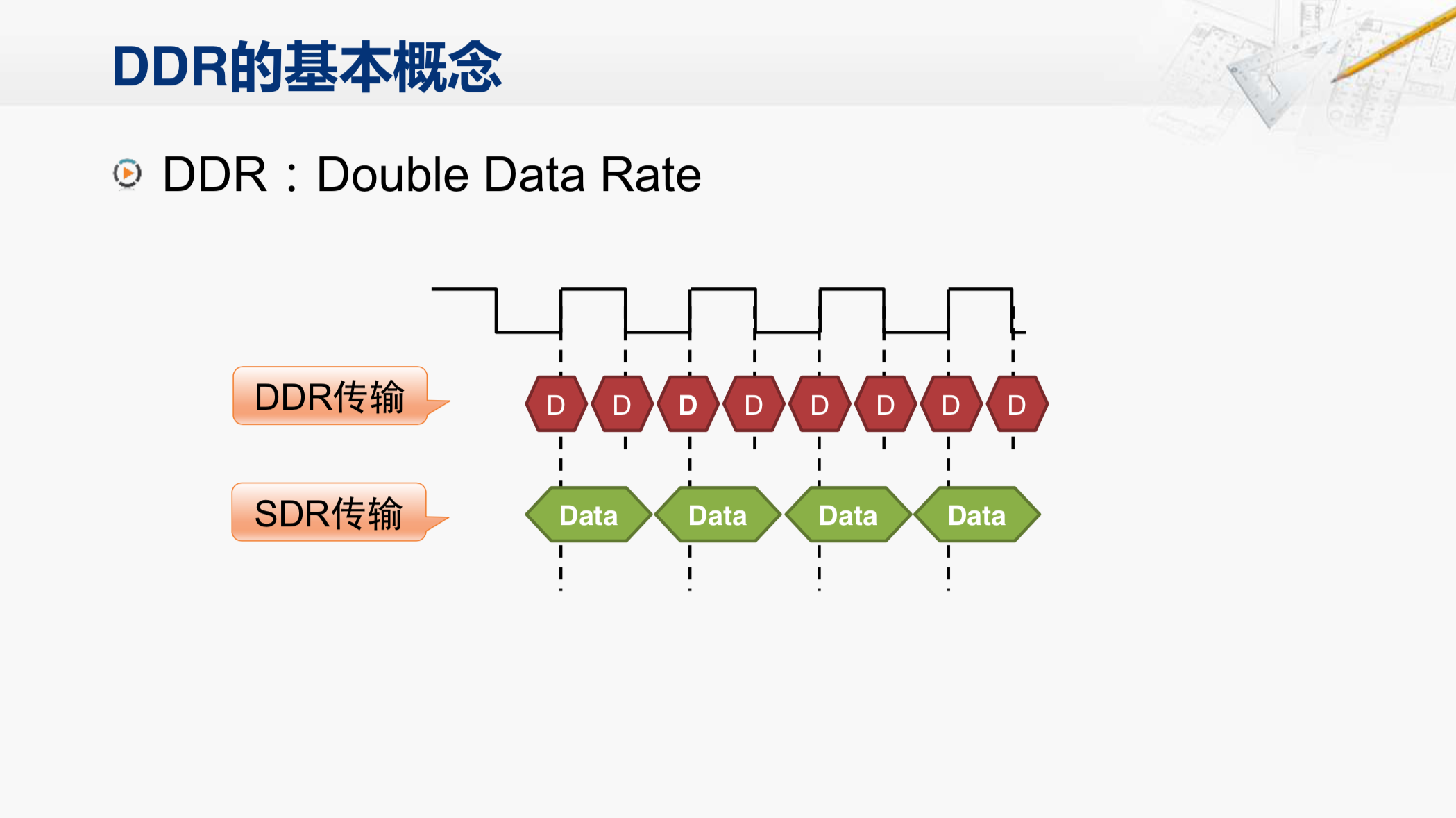

所谓的双倍数据率也就是DDR,相对应的是SDR。

SDR是指毎个时钟的上升沿传输数据,接收端也用时钟的上升沿采样数据;而DDR则是在时钟的上升沿和下降沿都传输数据,这样就可以在同样的时钟频率下传输双倍的数据。需要说明的是,DDR指的是一种传输方式,运用在SDRAM内存上,就有了DDR SDRAM。但它不仅仅用在内存上,还用在其他很多领域。所以,DDR 只是一种传输数据的方式,不能将它等价于我们现在用的内存。

那我们再来看一看DDR SDRAM是如何工作的。

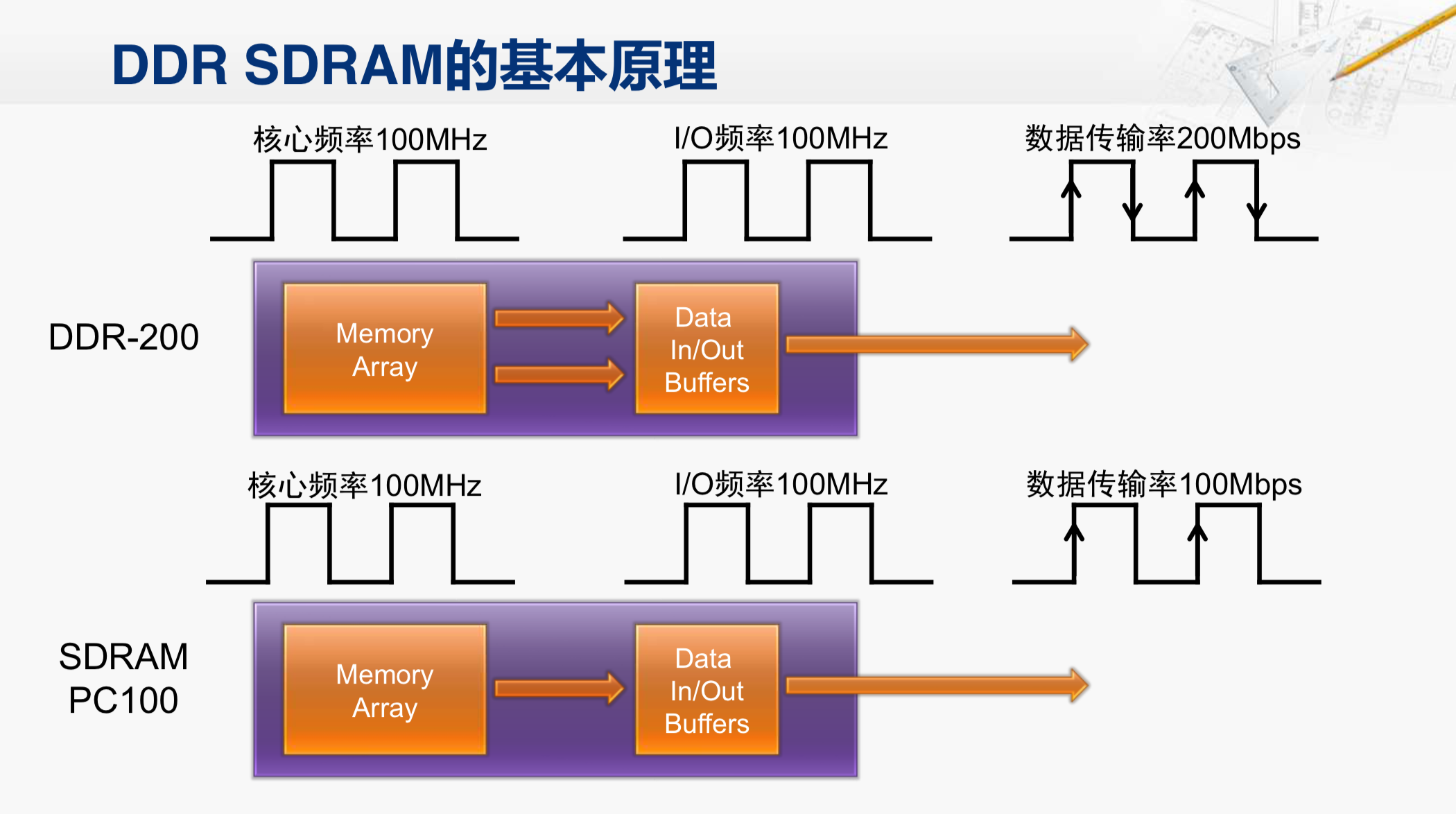

先来看看PC100规格的SDR SDRAM。它的存储阵列的核心时钟频率是100MHz,对外接口的时钟频率也是100MHz。以读操作为例,每个时钟周期从存储阵列中读一个数据并送到芯片的接口信号上。从外部看来每个时钟上升沿传输一个数据,单根数据线上的数据传输率为100Mbps。

而第一代DDR标准及DDR-200,它的存储阵列的核心时钟频率也是100MHz,但是每个时钟周期读出两个数据。接口的时钟频率还是100MHz,但因为在两个时钟沿都传输数据。所以,仍然在一个时钟周期内把这两个数据都传输出去了。从外部看来每个时钟上升沿和下降沿各传输一个数据,单根数据线上的数据传输率为200Mbps,这也就是DDR-200的名称由来。

到这里我们应该发现了一个问题,通常理解的提升内存性能应该是减少读写数据的时间。就像我们去图书馆借书,原来办手续需要十分钟,现在图书馆说要提升一倍的服务效率,我以为会只要五分钟了,但是DDR SDRAM的思路却不一样。它说,你看这样好不好?办手续我们还是保持十分钟,但你不是要借一本数学书吗?我现在多给你一本语文书,也就算我们的服务效率提升一倍了。这算不算欺骗消费者呢?咱们稍后再说。即使是保持办手续还是十分钟这件事情上,它也没有做到。

这张表列出了SDR到DDR1的各代内存的典型规格。我们看到SDR的核心频率从 66M 到 100M 再到133M,性能肯定是越来越好了。但是到了DDR1的第一代,也就是DDR-200,它的核心频率反而下降了,从 133MHz 降到了 100MHz。其实这也容易理解,要从存储阵列中每次取出双倍的数据,虽然改动并不大,但对性能还是有影响的。因此,速度也就慢了下来。

那DDR-200相对于PC133到底提升了什么呢?

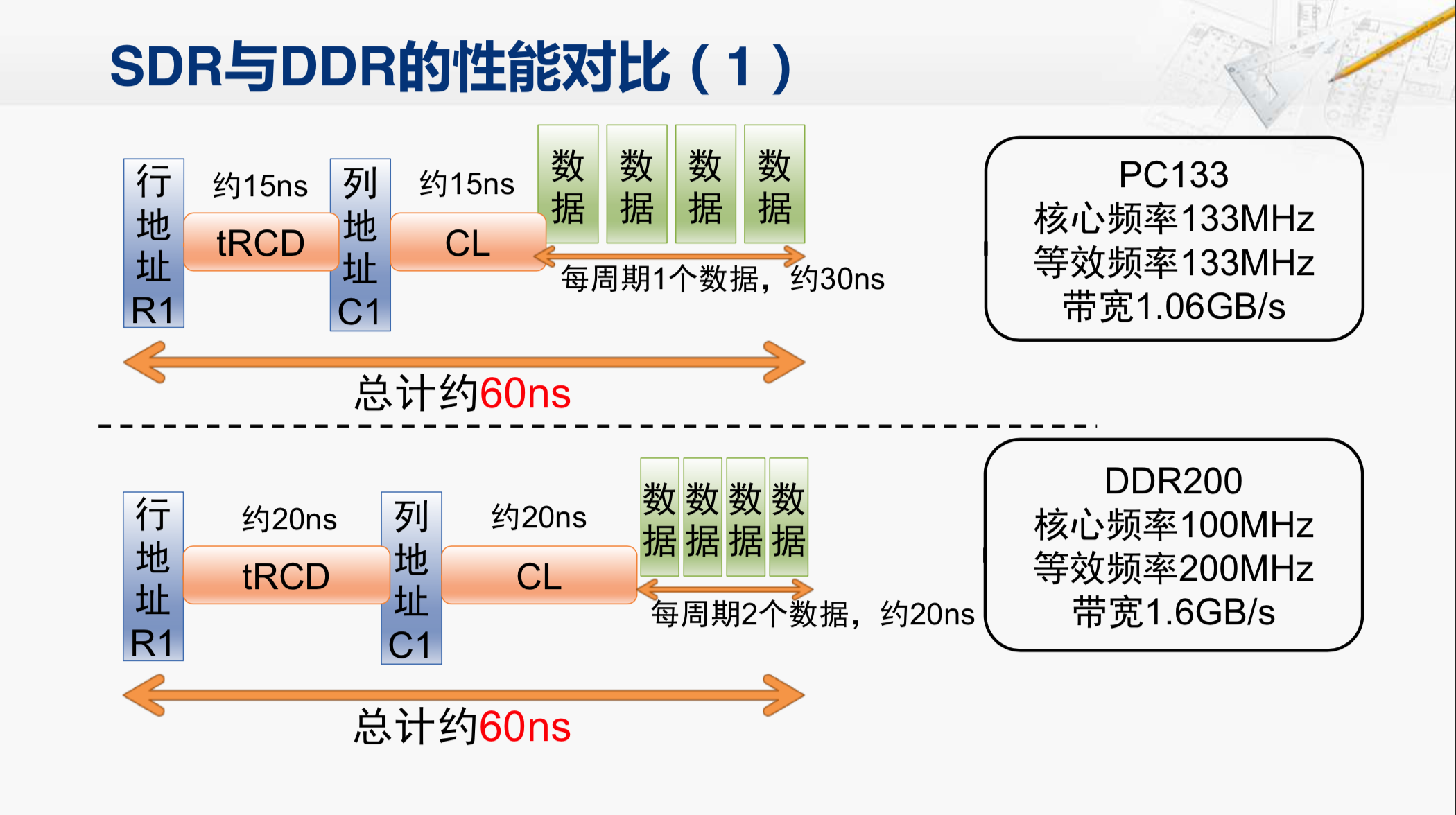

我们先以对PC133的读操作为例。大概需要15个纳秒进行行选,再用15个纳秒进行列选,然后才能得到第一个数据。而与这个数据相邻的后续数据则可以在每个时钟周期送出一个,而从发出地址到传输完这四个数据总共需要60ns。

我们再来看DDR-200。因为要从存储阵列中取出双倍的数据,所以对存储阵列的访问变慢了,大概需要20ns的行选,再加20ns的列选,这样才能得到第一个数据。不过在与这个数据相邻的后续数据则可以在每个时钟周期送出两个。因此,送出这四个数据,大约需要20ns。DDR-200宣称的 1.6GB/s 的传输带宽就是根据最后这一段20ns送出了四个数据计算出来的。这个指标本身没有错,但是评价内存的性能要看两个指标。这个指标称为访存带宽,是内存厂商大力宣传的。另一个重要的指标就是读出第一个数据的时间称为访存延迟,因为CPU真正需要的很可能只是第一个数据,所以访存延迟非常关键。这里DDR-200读出第一个数据用了40ns,比PC133还慢了10ns。即使是看读出这四个数据的总时间,它也用了总共60ns,和PC133是一样的。

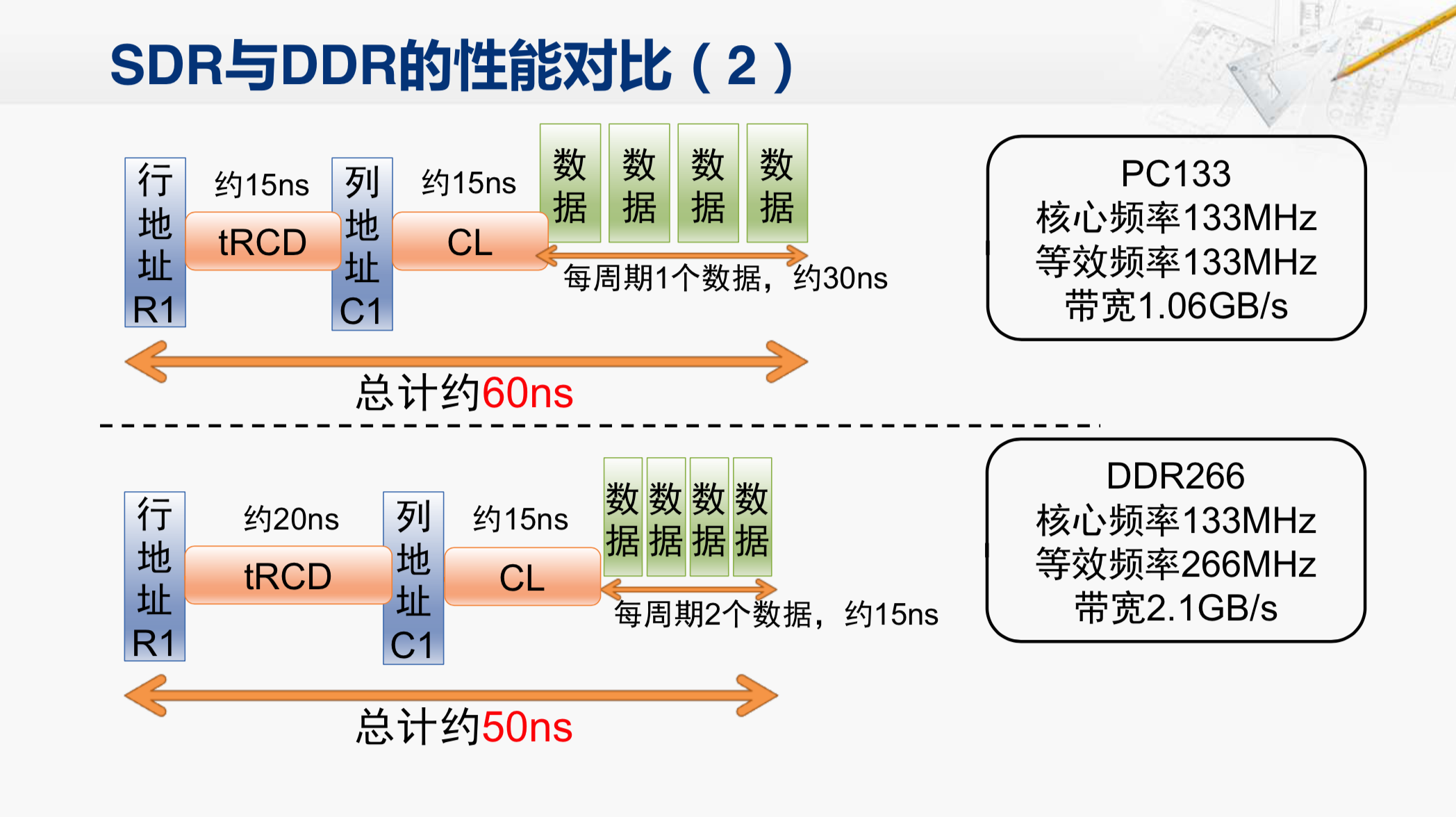

因此,DDR-200的性能表现是要比PC133差的。不过,随着制造工艺的改进到了下一代的DDR-266,情况有了一些改善。

DDR-266的核心频率已经提升到了133MHz,和PC133一样。但是行选的时间还偏慢一些,这样读出第一个数据大约需要35ns,不过连续读出四个数据的总时间已经比PC133要快一些了,大约是50ns。

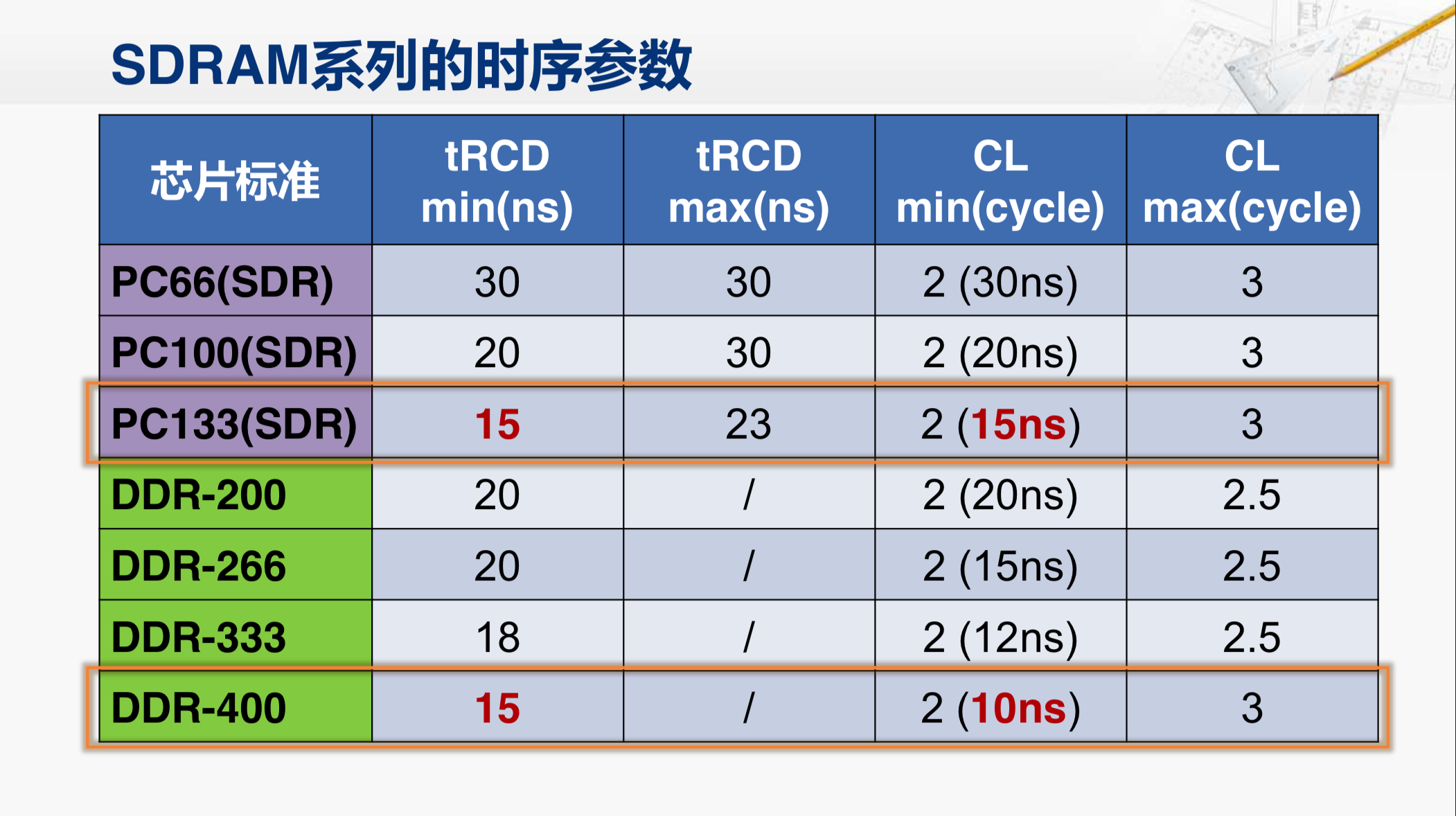

我们再来看一看行选和列选时间的参数的总表。等到了DDR-400的时候,最短的行选时间已经和PC133一样是15ns了;而列选也更快了一些,缩短到了10ns。因此,DDR-400的性能要明显优于PC133了。但是到了这个时候,核心频率的提升又遇到了困难。那么怎么继续提升内存性能呢?

这就轮到DDR2出场了。

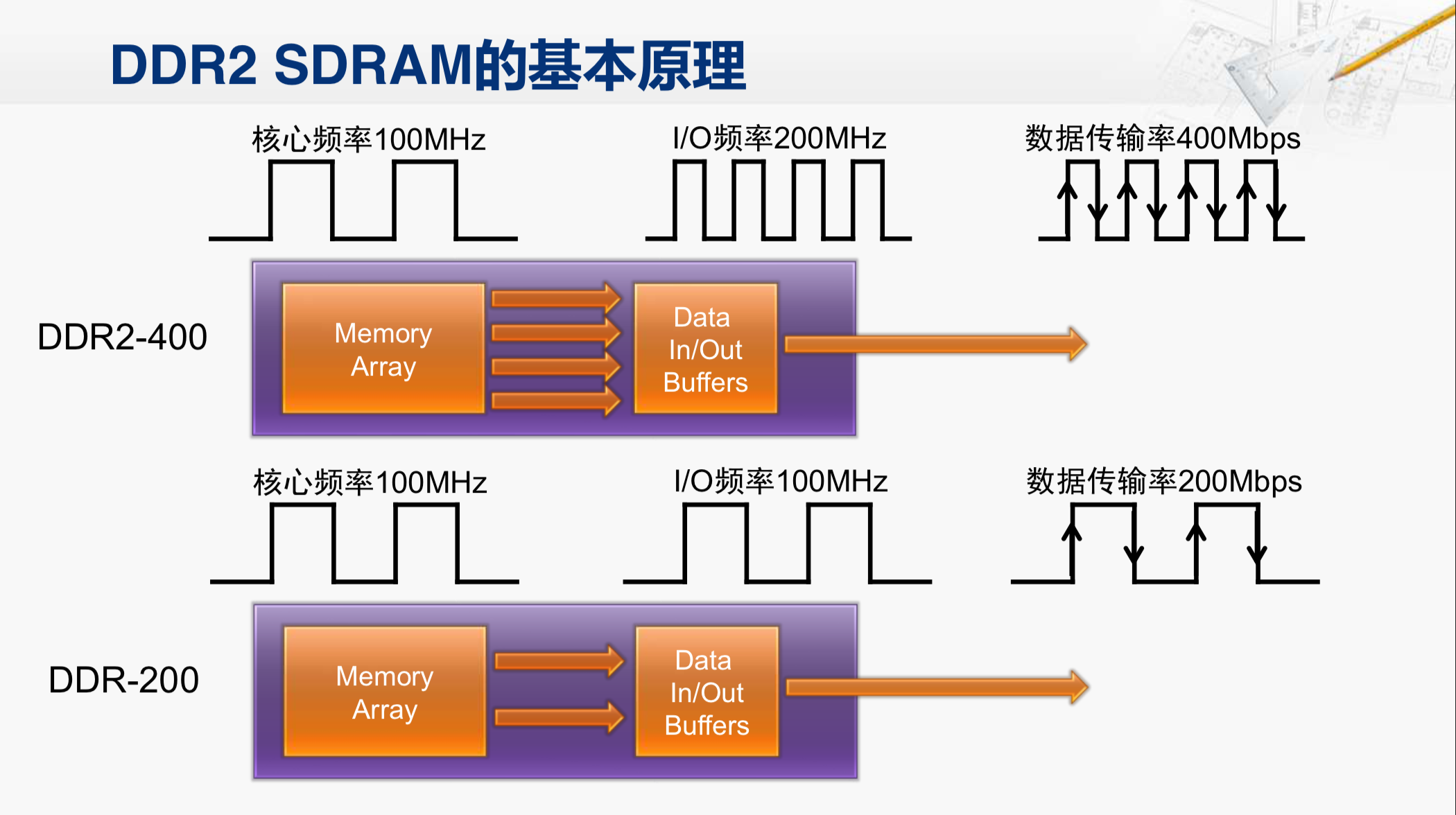

既然提升核心频率有困难,那就再增加预先取出数据的数量。之前是从存储阵列中取出双倍的数据,那现在就取出四陪的数据。例如 DDR-400,它的核心频率只有100MHz,和DDR-200一样,但因为预取了四个数据,从外界看来数据传输率达到了400Mbps。当然这时候单靠双倍数据率的传输也不够了。所以,它的接口时钟频率也提升了一倍,变成了200MHz。这样上下始终沿都传输数据,正好在核心时钟的一个周期内把四个数据都送出去了。

和之前一样,DDR2的第一代标准的性能也不好,其核心频率比当时流行的DDR-400要低一半,不但访存延迟大的多,而且访存带宽也是一样的。所以,DDR2-400的性能表现是全面落后于DDR-400的,很快就被市场淘汰了。随着制造工艺的改进,DDR2的核心频率提高之后,性能才逐渐地超过了DDR1。不过它的核心频率也没有提高多少。

而从DDR2到DDR3的升级,基本上也是一样的套路。

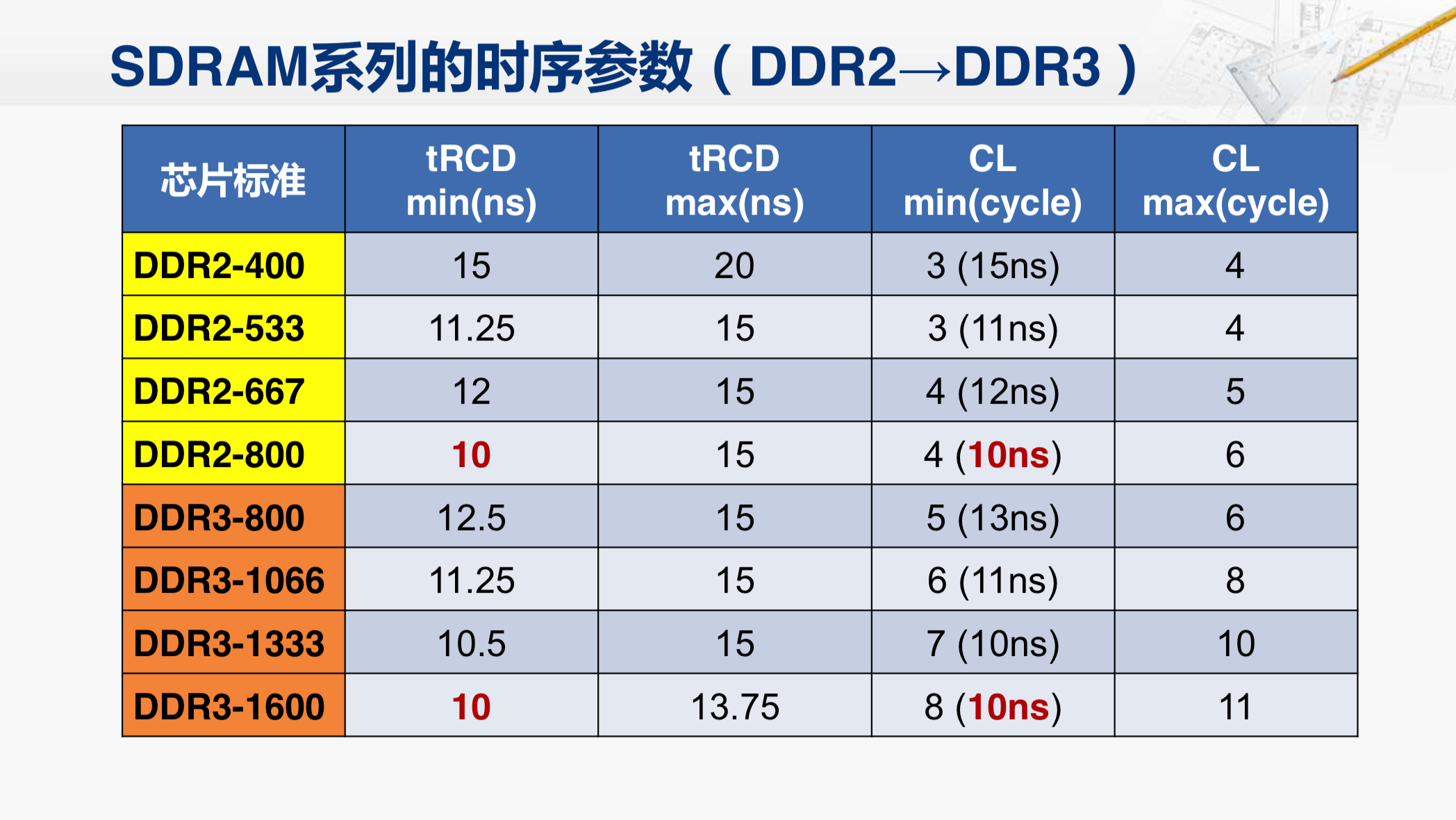

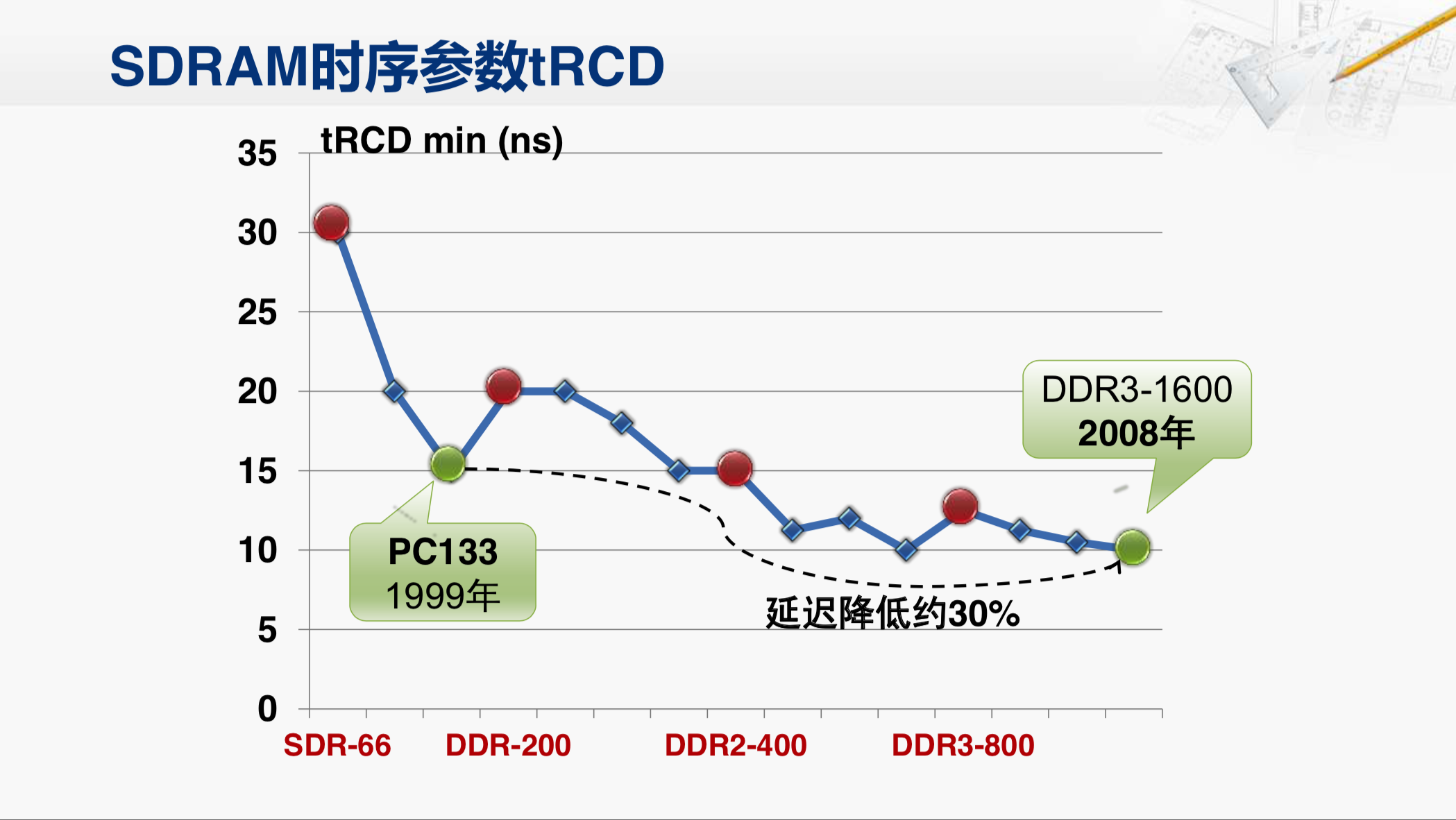

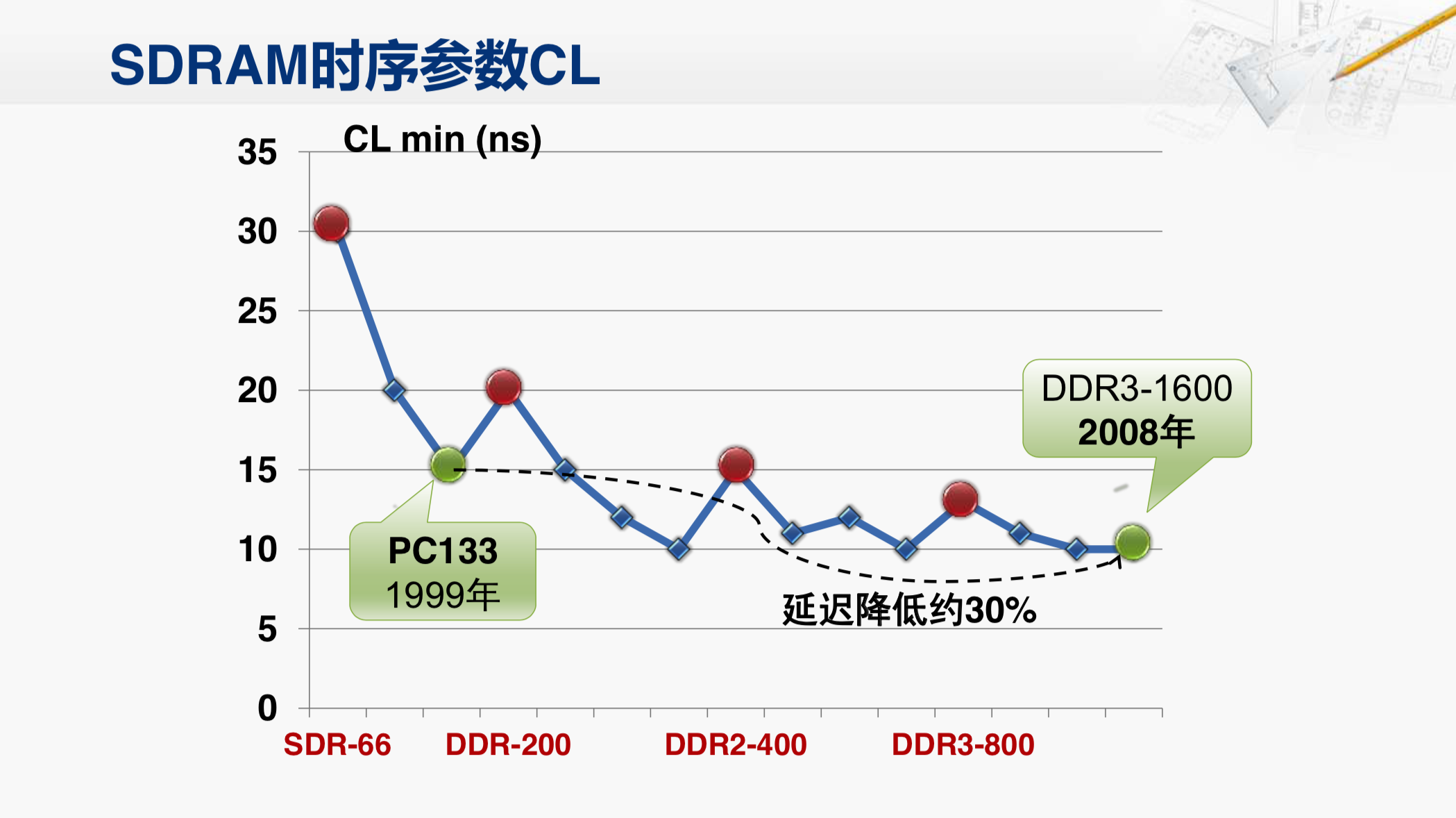

这是内存的行选时间的变化图,图中的每一个红点都是新升级后的第一代。我们可以看出,内存标准的每次升级都会让行选的时间变长,之后再慢慢地缩短。从SDR SDRAM的最后一代也就是PC133,到后来多年占据主流地位的DDR3-1600十几年的时间里行选时间也只是从15ns缩短到了10ns,降低了大约30%。

这是内存列选时间的变化图,情况基本一样。我们可以看出内存的发展过程,基本上就是以牺牲访存延迟为代价,努力提高访存带宽。访存带宽确实有了几十倍的提升,但是访存延迟的优化幅度很有限。这是由SDRAM的基本单元结构决定的,也就是那个电容的充放电过程。如果不从材料和结构上做根本的改变,基于现在的SDRAM结构想要优化访存延迟是很困难的。

所以说,从处理器访存的基本要求来看,读出一个指定数据所需要的时间确实没有多少改善,这个说法是没有问题的。

这就是所谓内存性能越来越高的真相。如果我是CPU,我想要的数据你并不能快一点给我,但你却给了我很多我现在用不着的数,这对性能真的有帮助吗?从现状来看肯定是有的,那这样的帮助是如何实现的呢?这就是我们下一节要探讨的问题了。