一、基本时序路径

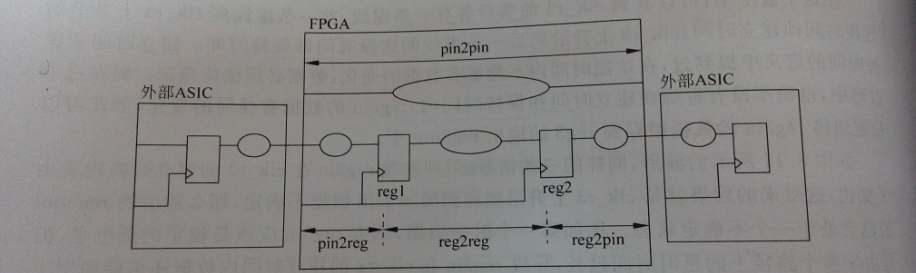

1.FPGA内部来说,常见的基本时序路径(即静态时序分析对象)有以下四类:

(1)内部寄存器之间的时序路径,即reg2reg

(2)输入引脚到内部寄存器的时序路径,即pin2reg

(3)内部寄存器到到输引脚的时序路径,即reg2pin

(4)输入引脚到输出引脚的时序路径,即pin2pin

其中前三类路径是和内部寄存器reg和时钟CLK有关的,因此还需关注内部数据信号与时钟锁存沿的建立时间和保存时间(具体见时序分析一),而最后一类信号的传输通常不经过时钟,因此它的约束也相对简单一些,一般直接约束pin2pin的延时值得范围即可。(另有一种说法是以上的时序分析都是针对时钟驱动的电路进行的,并且分析对象均为‘寄存器-寄存器对’,把引脚pin看作是在引脚外部虚拟一个寄存器做为分析对象,其实怎么看都行),不说了,先上图,四种时序路径如下图1

图1 常见的4种时序路径

2.具体的约束方法:

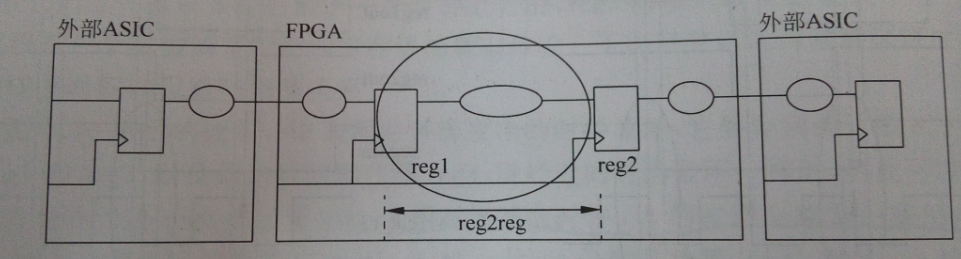

1>.reg2reg的约束对象为路径起始的源寄存器到最终的目的寄存器在FPGA里面的路径,对于reg2reg的约束方法,只要告诉时序约束工具他们的时钟频率(或时钟周期),约束工具就可以让此路径的延时符合时钟频率所要求的范围,其实就是使Setup Slack和Hold Slack大于0;见图2

图2

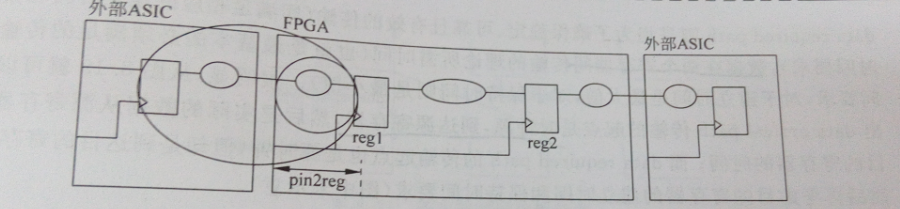

2>.pin2reg必须参考芯片的数据手册给出的时序信息来进行约束,如数据在芯片内部的延时Tco,Tsu和Th等;也可利用图3 pin2reg来约束,即图中大圈表示reg2reg(pin2reg看为其内部的路径),小圈就是pin2reg,而我们就是要约束大圈内小圈外的部分

图3

3>.reg2pin通过芯片给出的引脚信息来约束,跟图3差不多啦,只不过变为输出而已。

4>.pin2pin路径基本是一些组合逻辑和走线延时,在纯组合逻辑内部较常见,无所谓的保持时间和建立时间,我们只需要关心信号通过此路径的延时时间范围,在做约束时,只需要把最大,最小延时值传达给时序设计工具即可。

3.下面直接给出各路径的约束计算公式,说简单点就是满足Setup Slack和Hold Slack就ok啦!

1>.reg2reg:寄存器-寄存器( Register-to-Register)

建立时钟余量:

Clock Setup Slack = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay Source Register+μtco + Register-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu – Setup Uncertainty

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

保持时钟余量:

Clock Hold Slack = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register+μtCO + Register to Register Delay

Data Required Time = Clock Arrival Time + μtH + Hold Uncertainty

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

2>.reg2pin: 寄存器-输出引脚

建立时钟余量:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + Input Maximum Delay of Pin + Pin-to-Register Delay

Data Required Time = Clock Arrival Time – μtsu

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

保持时钟余量:

Clock Hold Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register + Input Minimum Delay of Pin + Pin to Register Delay

Data Required Time = Clock Arrival Time + μtH

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

3>.pin2reg: 输入引脚-寄存器

建立时钟余量:

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register +μtco + Register-to-Pin Delay

Data Required Time = Clock Arrival Time – Output Maximum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

保持时钟余量:

Clock Hold Slack Time = Data Arrival Time – Data Required Time

Data Arrival Time = Launch Edge + Clock Network Delay to Source Register +μtCO + Register to Pin Delay

Data Required Time = Clock Arrival Time – Output Minimum Delay of Pin

Clock Arrival Time = Latch Edge + Clock Network Delay to Destination Register

哈哈,是不是快要看傻了,细心的孩子还是可以发现一点规律的,现在让我们先来分析一下吧,这边的Setup Slack和Hold Slack和《Altera系列FPGA时序分析一》的东西是一样的啦,只做了一下小小的变通哦。先拿Setup Slack来开刀吧。

从上面三组公式可以看出: Data Arrival Time的前两项是相同的; Data Required Time的第一项是相同的; Clock Arrival Time的公式是相同的。

Clock Setup Slack Time = Data Required Time – Data Arrival Time

Data Arrival Time = 时钟到达前级寄存器的时刻 + 前级寄存器时钟到后级寄存器数据输入的延迟。

Data Required Time = 时钟到达后级寄存器的时刻 – 后级寄存器的建立时间。

其中,两个公式的第二项在其他情况下适当修改即可。这就和一些书中讲到时序分析时采用的公式一致了。明白了吗?

现在Hold Slack也就相对简单点了嘛,哈哈,你又要被搞掉了,以下内容留给读者自己去动手解决。

其实嘛,时序约束是一件特别难搞的事,如果你以为你掌握了上述公式就可以做出完美的时序约束来,那你就大错特错了,记得以前我们高中数学老师讲过,任何公式都是有使用前提的,如果忽略了它的使用条件,得出来的结果基本都是错的,就算结果蒙对了,思维还是不够严谨的,看来我宽哥威武啊!好啦,再来说说Launch Edge和Latch Edge;

建立时间检查须满足的条件如下:信号从Launch Edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太慢,时间不能太长,否则会侵占后级寄存器数据输入Pin相对于Latch Edge的建立时间。刚好满足后级寄存器建立时间的数据到达时间是Data Required Time( 相对于Latch Edge计算),实际的数据到达时间是Data Arrival Time(相对于Launch Edge计算)。显然,在建立时间检查中,Data Arrival Time要小于Data Required Time,否则就会造成建立时间违规。也就 是说,Data Required Time是Data Arrival Time的最大值。二者之差就是建立时间的时序余量。建立时间检查时,Timequest分析每个寄存器至寄存器通路的Launch Edge和 latch edge来确定建立关系。对于目标寄存器的每个Latch Edge, Timequest使用最靠近源寄存器的前一时钟的边沿做为Launch Edge。

保持时间检查须满足的条件如下:信号从Launch Edge开始计时,经过一系列的时序路径,到达后 级寄存器的数据输入Pin的速度不能太快,时间不能太短,否则会侵占后级寄存 器数据输入Pin相对于上一个Latch Edge的保持时间。刚好满足后级寄存器保持时 间的数据到达时间是Data Required Time(相对于Latch Edge计算),实际的数据 到达时间是Data Arrival Time(相对于Launch Edge计算)。显然,在保持时间检 查中, Data Arrival Time要大于Data Required Time,否则就会造成保持时序违规。 也就是说, Data Required Time是Data Arrival Time的最小值。二者之差就是保持 时间的时序余量。 建立时间检查和保持时间检查都是同步逻辑设计中对同一个规则的不同解 释:当前时钟沿发出的数据要在下一个时钟沿被正确捕获,不能晚,也不能早。 晚了会造成下一个时钟沿的建立时间违规,当前时钟沿发送的数据不能被下一个 时钟沿捕获;早了会造成上一个时钟沿发送的数据保持时间违规,上一个时钟沿 发送的数据不能被当前时钟沿正确捕获。二者在计算公式上的区别在于Slack计 算公式中减数与被减数关系。 Timequest分析器对每一种建立关系进行两种保持检查。第一种保持检查确 定当前Launch Edge的数据没有被前一Latch Edge捕获到。第二种保持检查确定下一Launch Edge没有被当前Latch Edge捕获到。需要注意的是,在Hold Slack计算中公式中的Latch Edge实际对应的是上一个Launch Edge。所以,当launch clock和latch clock是同一个时钟时,上述公式中的Latch Edge等于0;当前级和后级时钟不同时,还需要具体计算Latch Edge的取值。

好啦,差不多就是这样子理解就好了,我也不知道读者们懂了没,感觉说得太多了。如果有什么不正确的地方,请各位大侠指出,小弟定会好好改正,小编也会加紧修炼,增强功力,在与各高手过招的过程中不断学习。实际上吧,个人认为时序约束是FPGA开发设计中最难搞的一块,还需要计算PCB上的走线延时,什么最大最小延时之类的,好吧,真的太多了。

小编在这两篇博客中也省略了不少东西,比如恢复时间和移除时间啊,还有一些概念也没写出来吧,还有一些约束常用的语法未讲;过大家注意到一点东西没,就是这里全是理论知识,

还需要读者们亲手去试试,做一下约束,毕竟,理论和实践的差距真的挺大的。小编在这边就做得不好啦。当然这里的东西不一定全对,我怕会误导大家,如果是这样的话,小编是个罪人了,千古罪人啊。最后送给大家一句话:

尽信书不如无书!