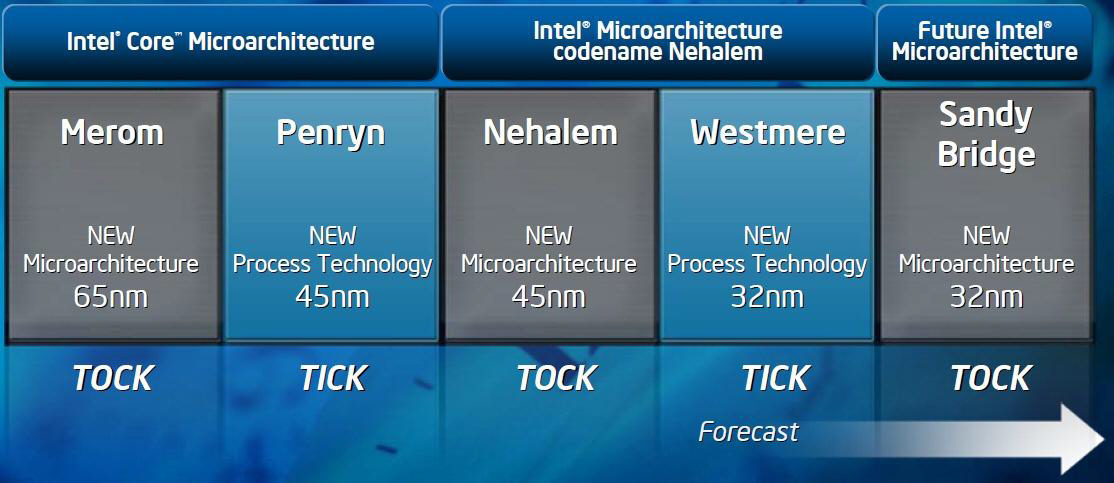

一、intel cpu发展计划tick-tock

Tick-Tock是Intel发展微处理器芯片设计制造业务的一种战略模式。Intel指出,每一次处理器微架构的更新和每一次芯片制程的更新遵循“Tick-Tock”规律,名称源于时钟秒针行走时所发出的声响。每一次“Tick”代表着一代微架构的处理器芯片制程的更新,而每一次“Tock”代表着在上一次“Tick”的芯片制程的基础上,更新微处理器架构提升性能。一般一次“Tick-Tock”的周期为两年,“Tick”占一年,“Tock”占一年。

二、现在CPU微架构

三、cpu cache

一个例子,下面loop1和loop2 哪个执行快

int []arr = new int[64 * 1024 * 1024];

// Loop 1

for (int i = 0; i < arr.Length; i++) arr[i] *= 3;

// Loop 2

for (int i = 0; i < arr.Length; i += 16) arr[i] *= 3;

第二个循环只执行了第一个1/16的计算量,但是两个循环在计算机上的耗时是差不多的70-80ms;造成这个问题的原因在于cpu cache line是64bytes,每次从内存加载64Bytes数据到cache;

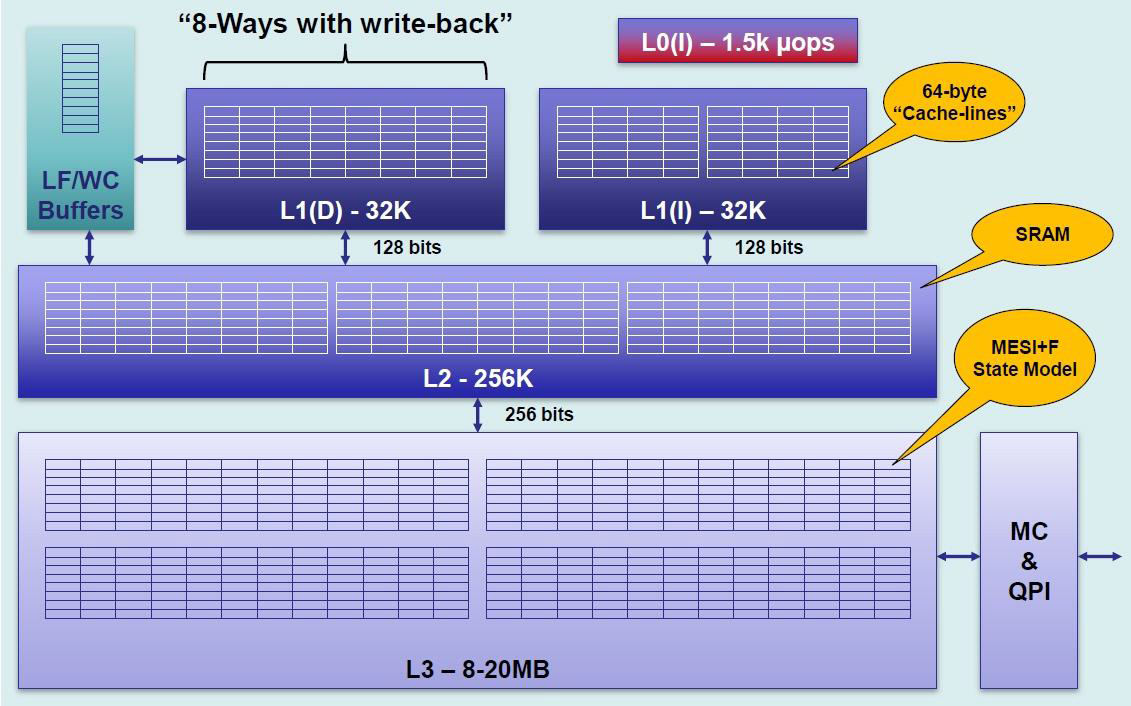

3.1 Nehalem(三级)结构

L1(每核独有) 数据32k 指令32K分开

L2(每核独有) 256K

L3(共享) 8M

四、cache和内存的关联方式(associativity)

一类是全关联cache(full associative cache),一种是直接关联cache(direct mapped cache),还有一种是N路关联cache(N-ways associative cache)。

全关联(每个内存块可映射到任意cache line),冲突最低,定位慢;直接关联(每个内存块映射到固定的cache line),定位最快,冲突严重;N路关联折中。

下图是8路关联 cache line定位,共64个set:

其中:

index用于定位set

tag用于在set中定位cache line

offet在cache line中定位数据

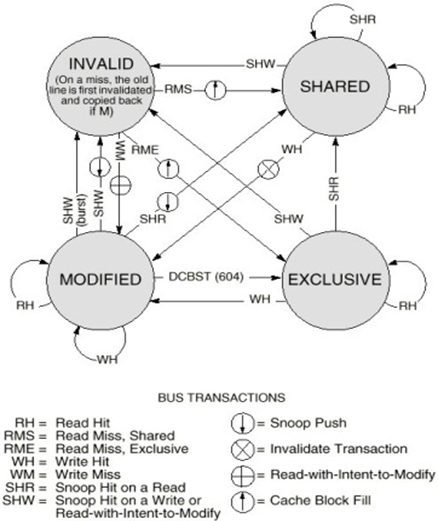

五、cache一致性协议MESI

cache一致性问题描述:

步骤2 update时,根据一致性协议,会先发送Invalid消息到总线,失效core1的cache及RAM;core1读取Bar时,发现Invalid状态后,会向总线请求,core2会发送Bar=2给core1的cache。

MESI提供cache一致性保证,表示cache对应的四种状态及状态迁移。

Invalid:无有效数据

Shared:与memory有一致数据,读

Modified:更新数据,与memory不一致

Excusive:与memory有一致数据,单点持有;