lab05 -- SOS信号之一

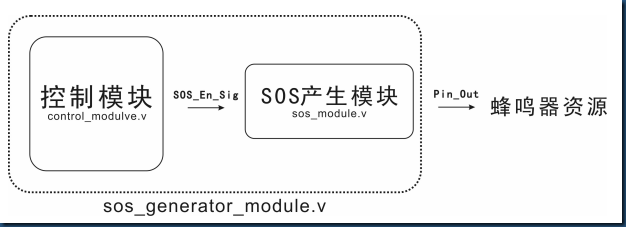

本实验要做一个sos信号发生器,如上图所示,由2个模块构成,其中sos_module.v用来产生sos信号,对应莫尔斯电码就是. . . _ _ _ . . .,其中点(短音)用100ms的高电平表示,杠(长音)用300ms的高电平表示,空格用50ms的间隔表示。control_module.v作为控制模块,用来产生一个使能信号sos_en_sig。最后,实验的演示验证部分,由于DE2不带蜂鸣器,暂用LEDG8代替。(当然,用蜂鸣器的效果要明显些)。

代码

sos_module.v

1 /**

2 * File name: sos_module.v

3 *

4 */

5

6 module sos_module

7 (

8 clk, rst_n, pin_out, sos_en

9 );

10

11 input clk;

12 input rst_n;

13 input sos_en;

14 output pin_out;

15

16 parameter T1MS = 16'd50000 - 1;

17

18 reg [15:0] count;

19

20 always @(posedge clk or negedge rst_n)

21 if (!rst_n)

22 count <= 16'd0;

23 else if (iscount && count == T1MS)

24 count <= 16'd0;

25 else if (iscount)

26 count <= count + 1'b1;

27 else if (!iscount)

28 count <= 16'd0;

29

30 reg [9:0] count_ms;

31

32 always @(posedge clk or negedge rst_n)

33 if (!rst_n)

34 count_ms <= 10'd0;

35 else if (iscount && count == T1MS)

36 count_ms <= count_ms + 1'b1;

37 else if (!iscount)

38 count_ms <= 10'd0;

39

40 reg iscount;

41 reg rpin_out;

42 reg [4:0] i;

43

44 always @(posedge clk or negedge rst_n)

45 if (!rst_n)

46 begin

47 iscount <= 1'b0;

48 rpin_out <= 1'b0;

49 i <= 5'd0;

50 end

51 else

52 case(i)

53 5'd0:

54 if (sos_en)

55 i <= 5'd1;

56

57 5'd1, 5'd3, 5'd5, //short

58 5'd13, 5'd15, 5'd17:

59 if (count_ms == 10'd100)

60 begin

61 iscount <= 1'b0;

62 rpin_out <= 1'b0;

63 i <= i + 1'b1;

64 end

65 else

66 begin

67 iscount <= 1'b1;

68 rpin_out <= 1'b1;

69 end

70

71 5'd7, 5'd9, 5'd11: //long

72 if (count_ms == 10'd300)

73 begin

74 iscount <= 1'b0;

75 rpin_out <= 1'b0;

76 i <= i + 1'b1;

77 end

78 else

79 begin

80 iscount <= 1'b1;

81 rpin_out <= 1'b1;

82 end

83

84 5'd2, 5'd4, 5'd6, //interval

85 5'd8, 5'd10, 5'd12,

86 5'd14, 5'd16, 5'd18:

87 if (count_ms == 10'd50)

88 begin

89 iscount <= 1'b0;

90 i <= i + 1'b1;

91 end

92 else

93 iscount <= 1'b1;

94

95 5'd19: //end

96 begin

97 rpin_out <= 1'b0;

98 i <= 5'd0;

99 end

100 endcase

101

102 assign pin_out = rpin_out;

103

104 endmodule

105

106

107

control_module.v

1 /**

2 * File name : control_module.v

3 *

4 */

5

6 module control_module

7 (

8 clk, rst_n, sos_en

9 );

10

11 input clk;

12 input rst_n;

13 output sos_en;

14

15 parameter T3S = 28'd150_000_000 - 1;

16

17 reg isen;

18 reg [27:0] count;

19

20 always @(posedge clk or negedge rst_n)

21 if (!rst_n)

22 begin

23 isen <= 1'b0;

24 count <= 28'd0;

25 end

26 else if (count <= T3S)

27 begin

28 isen <= 1'b1;

29 count <= 26'd0;

30 end

31 else

32 begin

33 isen <= 1'b0;

34 count <= count + 1'b1;

35 end

36

37 assign sos_en = isen;

38

39 endmodule

40

41

sos_generator_module.v

1 /**

2 * File name: sos_generator_module.v

3 *-----------------------------------

4 * pins: KEY0-rst_n, LEDG8-pin_out

5 *-----------------------------------

6 * yf.x

7 * 7-15-2011

8 *

9 */

10

11 module sos_generator_module

12 (

13 CLOCK_50, KEY, LEDG

14 );

15

16 input CLOCK_50;

17 input [0:0] KEY;

18 output [8:8] LEDG;

19

20 wire sos_en;

21

22 control_module U1

23 (

24 .clk (CLOCK_50),

25 .rst_n (KEY),

26 .sos_en (sos_en)

27 );

28

29 wire pin_out_wire;

30

31 sos_module U2

32 (

33 .clk (CLOCK_50),

34 .rst_n (KEY),

35 .sos_en (sos_en),

36 .pin_out (pin_out_wire)

37 );

38

39 assign LEDG = pin_out_wire;

40

41 endmodule

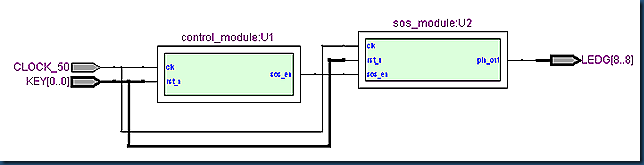

RTL图

小结

控制模块每隔3秒就产生一个使能信号,促使功能模块发出sos信号。至于代码,做到这里,已经能感觉到akuei2的风格,即建模的“仿顺序操作”的思想。