使用组合逻辑电路驱动VGA显示器

1. 概述

本文讲述一种不使用缓冲存储器驱动VGA显示的简单方法.其中,VGA分辨率采用DE10-Lite建议使用的640X480.像素的时钟25MHz,刷新率59.5帧/秒.

在DE10-Lite实验板上,VGA接口使用4位数值表示色彩.全0表示不亮,全1表示亮度最高,红,黄,蓝的明度在4’b0000-4’b1111之间,表示不同亮度的色彩.

信号col和row表示VGA控制器驱动的像素地址.

2. VGA接口信号

VGA接口相对简单.信号v_sync(垂直同步)变低,表示一帧图像完成,并为下一帧图像做准备.这一点在下图可以看到.

同样,信号h_sync变低表示一行数据传输完成,并为下一行数据做准备,这个在上图放大后可以看到h_sync变低了数百次.

下图显示了一些波形的细节,在266行,信号v_sync和h_sync都是高的时侯,col和row计数的变化,这里没有显示红黄蓝的数值.

3. 开始编写VGA代码

代码设计参考vga.combinational2.zip,其中包含各个模块和PLL例化.

4. 模块说明

VGA工程的主要模块说明如下:

l pll.v,pll.qip,pll.ppf

为得到一个正确的时钟信号,用PLL例化,由50MHz生成25Mhz的时钟信号。

pll.qip给Quartus提供一些信息,器件,相关的Verilog文件,ppf文件。pll.v是PLL例化文件。pll.ppf提供各种输入/出引脚数据。

l vga_controller.v

这个模块生成VGA接收端需要的行和列同步信号。通常,并不需要h_sync,v_sync和disp_ena信号。像素显示总是从左到右,从上往下,起点是左上角那个(0,0)的像素点。为了方便定位像素点,VGA_controller输出两个信号:行和列坐标。row-纵坐标,col-横坐标。注意disp_ena为0时,这些信号无效。

l comb_ckt_generator.v

这是一个组合逻辑模块,用来决定实验板上10个SW开关对应位置的像素点的RGB的色彩值。

l top.v

这是本设计的顶层模块,例化vga_controller和产生寄存器的时序,色彩输出信号。

这里面注意RGB为4‘b0000和4’b1111时的色彩。

5.使用代码去驱动显示

上面提供的代码很简单。给定行,列坐标(row:0-479;col:0-649)。像comb_ckt_generator.v里显示的那样,要创建合适的逻辑给像素点赋值RGB。

通常,会使用缓存来现存储要显示的图像,再显示。这里因为MAX10 FPGA没有现成的足够数量的缓存,所以我们用前述方法替代。

6.时钟信号vga_clk

在这个设计里,所有触发器的同步时钟信号应该是25MHz,而不是50MHz。VGA接口的像素时钟也是25MHz。

7.关于帧更新的时间问题

在完成一帧画面传输至准备传输下一帧画面之间,要及时更新传输的数据。比如,快速移动的对象,不会一部分显示在这一块,一部分显示在另一块。

处理这个问题,最好的方法是使用同步信号,比如垂直同步信号(VGA_VS)。如同DE10-Lite用户手册所述,VGA接口信号包含特殊的时间间隔。前面提供的代码里已经解决了这个问题。

8.保持VGA输出同步

虽然comb_ckt_generator.v没有时钟输入,如果块的复杂性需要,当然可以添加时钟输入和时钟内部逻辑。在行列,同步信号间可以添加流水线控制。

9. 补充说明

VGA驱动电路的难点还是在于VGA时序控制模块,这里的代码采用了一个比较巧妙的设计,以行扫描为例来阐述.我们知道一行完整的数据传输需要行同步的时间+后沿+像素显示的时间+前沿,其中行同步时用来表明一行显示完,准备显示下一行,而前沿,后沿则是消隐的需要.代码里,为了使计数器的值从0开始就与像素的坐标匹配,所以行扫描的周期从像素显示开始计数,一行的计数顺序是像素显示+前沿_行同步+后沿.这样,通过限定最大值,就能确定坐标的范围,并且是从左上角那个点开始显示.

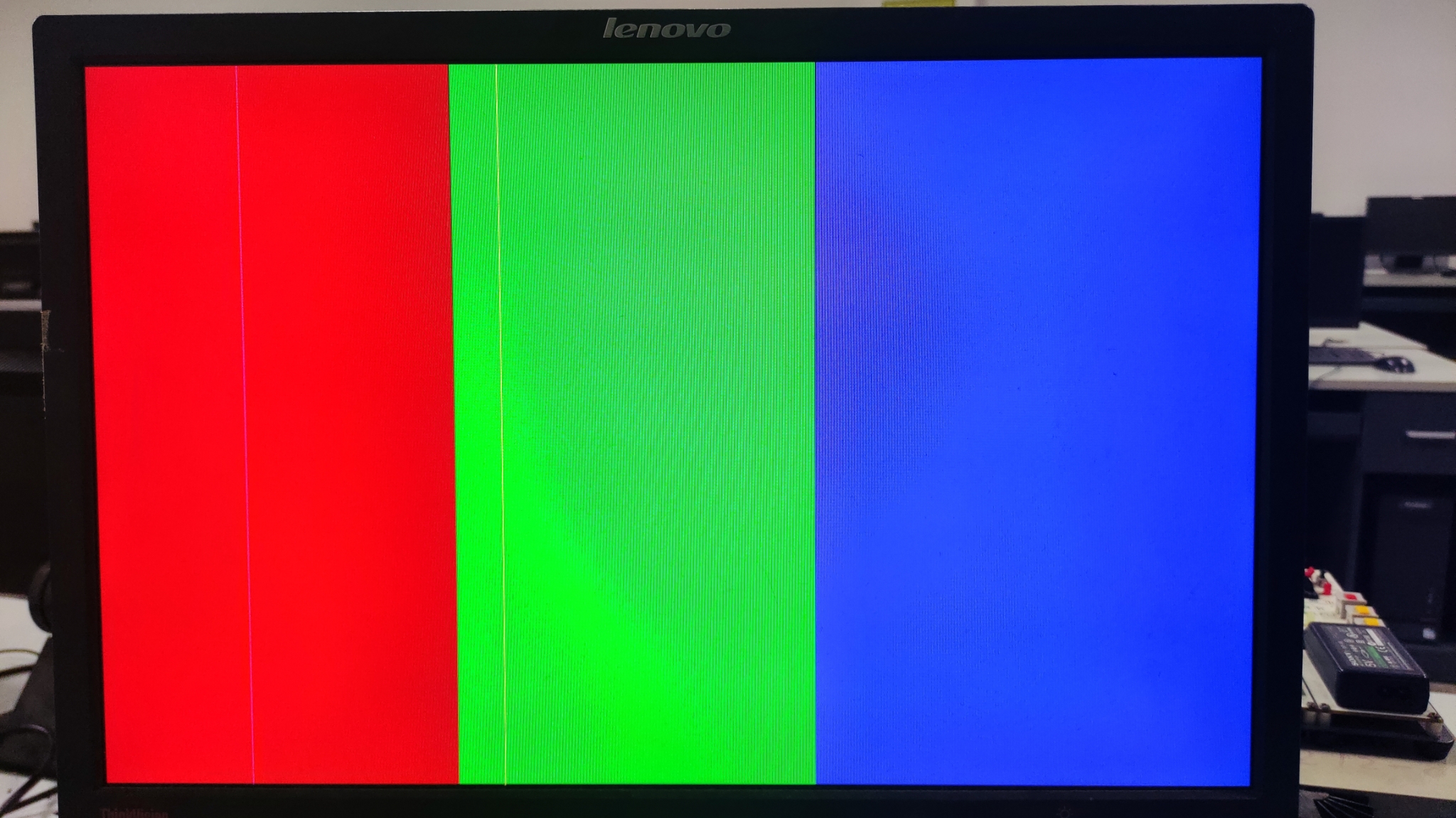

原设计是用3个SW开关来控制显示屏显示三种色彩或混合色.有了坐标和像素点的对应关系的理解后,可以稍稍把下图中85-87行的代码修改成col的区域,使屏幕显示不同的色块.

修改后可以实现类似

References:

- EEC180 Tutorial: Displaying to a VGA monitor using a combinational circuit

https://www.ece.ucdavis.edu/~bbaas/180/tutorials/vga/

Written by YongfengXie

2022/05/27 Written