DE10-Lite锁相环使用教程

目标:本文讲述如何在Quartus里设置和例化一个锁相环.

引言

锁相环(PLL)是一种闭环频率控制电路,用于比较压控振荡器的输入信号和输出信号之间的相位差. 负反馈回路迫使锁相环的输出信号与输入信号同相。

几乎所有的FPGA都含有用于时钟产生和分配的片内锁相环.锁相环最大的优点是能产生不同于输入时钟的输出时钟信号. 例如,完全可以使用锁相环从DE10‐LITE板上的50 MHz外部时钟在MAX10 fpga上生成100 MHz内部时钟。

本教程将演示如何使用Quartus中的IP(知识产权)核来实例化设计中的PLL,以生成不同的时钟频率。关于锁相环和Altera/Intel设计组件的更深入的讨论可以在https://www.altera.com/en_US/pdfs/literature/ug/ug_altpll.pdf查看.

生成PLL IP组件

- 打开工程.

- 在Quartus里打开IP目录窗口Tools > IP Catalog,在目录窗口的库里浏览,找到ALTPLL。

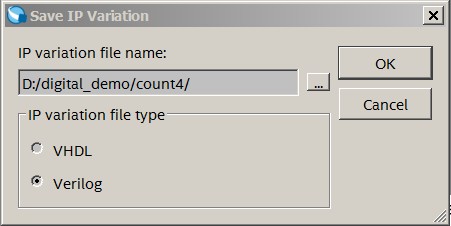

3. 双击ALTPLL。弹出的对话框询问存储IP组件的位置。通常我会建议在工程目录下建立一个IP子目录用来保存IP组件,这里指定保存路径,并以pll命名这个IP组件。

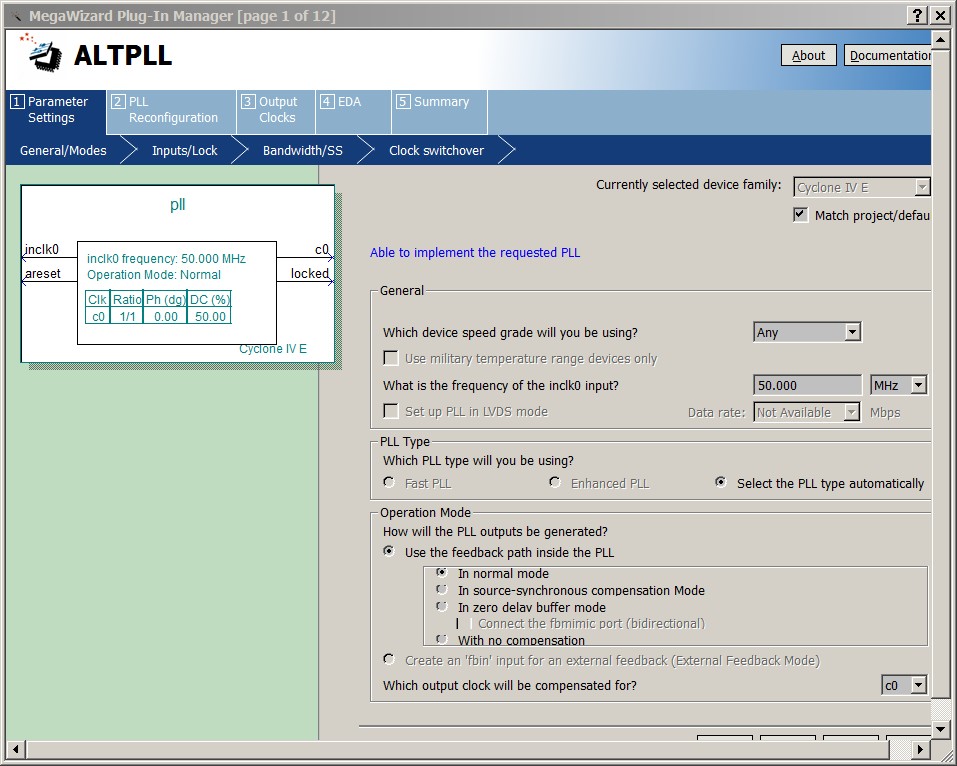

4. 单击OK。出现插件功能管理器窗口。为了匹配DE10-Lite上的外部时钟,把输入时钟inclk0的频率改为50MHz。

5. 单击Next。删除areset和locked,这里我们一般不需要这两个信号。

6. 一路单击Next直到设置时钟c0窗口。这里把c0的频率设为100MHz,Quartus将尽力生成这个频率的时钟信号。

7. 如果你需要更多的时钟信号,同样可以很容易的添加设置c1-c4。如果不需要,就一路单击Next,直到最后一个窗口。勾选例化模板项。这样在顶层设计里例化pll模块时将会很方便。然后单击Finish。

8. 会弹出对话框,询问你是否要把刚生成的pll组件添加到工程里,这里选Yes。

9. 在工程管理窗口的文件页,你会发现pll.qip文件。这样说明已经成功地生成PLL IP组件。

使用生成的IP组件

现在,我们将要在顶层模块里例化之前生成的PLL IP组件。

1. 打开存储PLL组件的目录,会发现pll_inst.v例化模板文件。

2. 打开pll_inst.v文件,把例化模板复制到剪切板。

3. 在顶层模块里(需要例化的地方)粘贴复制的例化模板,然后修改匹配端口名。必须注意输入/出的时钟信号要和实验板上的时钟名,电路里使用的时钟名匹配。比如输入时钟用MAX10_CLK1_50 或 MAX10_CLK2_50,输出时钟用clk(你顶层代码里的时钟信号的名称)。

4. 完成。

修改PLL IP组件

如果需要修改PLL组件,不用重复上面的步骤去生成一个新的组件,只需要在工程管理窗口打开IP Components页。双击要修改的IP组件,就会打开设置窗口,更改即可。

References:

- Tutorial: Instantiating and Using a PLL on the DE10‐LITE

https://www.ece.ucdavis.edu/~bbaas/180/tutorials/using.a.PLL.pdf

Written by YongfengXie

2022/05/26 Written