6.1 I/O系统

一.设备

1.分类

(1)速度

1)低(鼠标、键盘)

2)中(打印机)

3)高(磁盘)

(2)传输单位

1)字符(低:键盘,鼠标(中断))

2)块(高:磁盘(DMA))

(3)属性

1)独占

2)共享

3)虚拟设备:独占->共享

(4)方式

1)I(鼠标键盘)

2)O(打印机)

3)I/O(磁盘)

2.接口

(1)数据信号线

(2)控制信号线

(3)状态信号线

二.控制器

- 功能

(1) 接收和识别命令。设备控制器能接收并识别处理机发来的多种命令。在控制器中 具有相应的控制寄存器,用来存放接收的命令和参数,并对所接收的命令进行译码。例如, 磁盘控制器可以接收CPU发来的read、write、format等丨5条不同的命令,而且有些命 令还带有参数。相应地,在磁盘控制器中有多个寄存器和命令译码器等。

(2) 数据交换。设备控制器可实现CPU与控制器之间、控制器与设备之间的数据交换。 对于前者,是通过数据总线,由CPU并行地把数据写入控制器,或从控制器中并行地读出 数据。对于后者,是设备将数据输入到控制器,或从控制器传送给设备。为此,在控制器 中须设置数据寄存器。

(3) 标识和报告设备的状态。控制器应记下设备的状态供CPU 了解。例如,仅当该设 备处于发送就绪状态时,CPU才能启动控制器从设备中读出数据。为此,在控制器中应设 状态寄存器,用其中的每一位反映设备的某一种状态。当CPU将该寄存器的内容读入 后,便可了解该设备的状态。

(4>地址识别。就像内存中的每一个单元都有一个地址一样,系统中的每一个设备也 都有一个地址。设备控制器必须能够识别其所控制的每个设备的地址。此外,为使CPU能 向(或从)寄存器中写入(或读出)数据,这些寄存器都应具有唯一的地址。控制器应能正确识 别这些地址。为此,在控制器中应配置地址译码器。

(5) 数据缓冲区。由于I/O设备的速率较低,而CPU和内存的速率却很高,故在控制 器中必须设置一缓冲区。在输出时,用此缓冲区暂存由主机高速传来的数据,然后才以与 I/O设备所匹配的速率将缓冲器中的数据传送给I/O设备。在输入时,缓冲区则用于暂存从 I/O设备送来的数据,待接收到一批数据后,再将缓冲区中的数据高速地传送给主机。

(6) 差错控制。对于由I/O设备传送来的数据,设备控制器还兼管进行差错检测。若发 现传送中出现了错误,通常是将差错检测码 S位,并向 CPU报告,于是 CPU将本次传送 来的数据作废,并重新进行一次传送。这样便可保证数据输入的正确性。

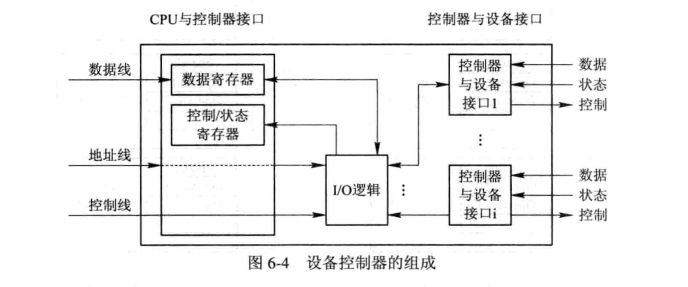

2.组成

(1) 设备控制器与处理机的接口。该接口用于实现CPU与设备控制器之间的通信,在该接口中共有三类信号线:数据线、地址线和控制线。数据线通常与两类寄存器相连接: ①第一类是数据寄存器,在控制器中可以有一个或多个数据寄存器,用于存放从设备送来 的数据(输入),或从CPU送来的数据(输出)。②第二类是控制/状态寄存器,在控制器中可 以有一个或多个这类寄存器,用于存放从CPU送来的控制信息或设备的状态信息。

(2) 设备控制器与设备的接口。在一个设备控制器上,可以连接一个或多个设备。相 应的,在控制器中便有一个或多个设备接口。在每个接口中都存在数据、控制和状态三种 类型的信号。控制器中的I/O逻辑根据处理机发来的地址信号去选择一个设备接口。

(3) I/O逻辑。I/O逻辑用于实现对设备的控制。它通过一组控制线与处理机交互,处 理机利用该逻辑向控制器发送I/O命令。每当CPU要启动一个设备时,一方面将启动命令 发送给控制器,另一方面又同时通过地址线把地址发送给控制器,由控制器的I/O逻辑对 收到的地址进行译码,再根据所译出的命令对所选设备进行控制。

三. 通道

- 定义:外围处理机,I/O处理机

- CPU与通道关系

|

设备 |

CPU |

CH |

|

指令 |

复杂 |

单一 |

|

存储器 |

有M |

无M |

|

关系 |

CPU与CH并行工作,CH受控于CPU |

|

- 分类

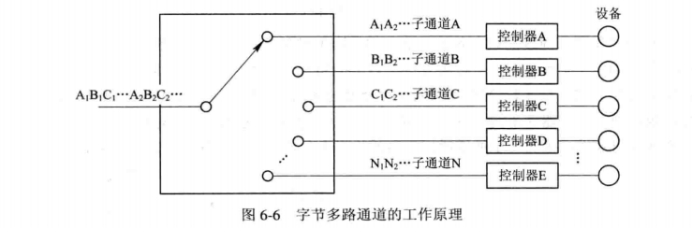

(1)字节多路通道

这是一种按字节交叉方式工作的通道。它通常都含有许多非分配型子通道,其数最可 从几十到数百个,每一个子通道连接一台I/O设备,并控制该设备的I/O操作。这些子通 逍按时间片轮转方式共享主通道。当第一个子通道控制其I/O设备究成一个字节的交换后, 便立即腾出主通道,让给第二个子通道使用:当第二个子通道也完成一个字节的交换后, 同样也把主通道让给第三个通道:依此类推。当所有子通道轮转一周后,又返回来由 第一个子通道去使用字节多路主通道。这样,只要字节多路通道扫描每个子通道的速率足 够快,而连接到子通道上的设备的速率又不是太高,便不致丢失信息。

(2)数组选择通道

字节多路通道不适于连接高速设备,这推动了按数组方式进行数据传送的数组选择通 道的形成。这种通道虽然可以连接多台高速设备,但由于它只含有一个分配型子通道,在 一段时间内只能执行一道通道程序,控制一台设备进行数据传送,致使当某台设备占用了 该通道后,便一贞由它独占,即使是它无数据传送,通道被闲置,也不允许其它设备使用该通道,直到该设备传送完毕释放该通道。这种通道的利用率很低。

(3)数组多路通道

数组选择通道虽有很高的传输速率,但它却每次只允许一个设备传输数据。数组多路 通道是将数组选择通道传输速率高和字节多路通道能使各子通道(设备)分时并行操作的优 点相结合而形成的一种新通道。它含有多个非分配型子通道,因而这种通道既具有很高的 数据传输速率,又能获得令人满意的通道利用率。也正因此,才使该通道能被广泛地用于 连接多台高、中速的外围设备,其数据传送是按数组方式进行的。

6.2 对I/O的控制方式

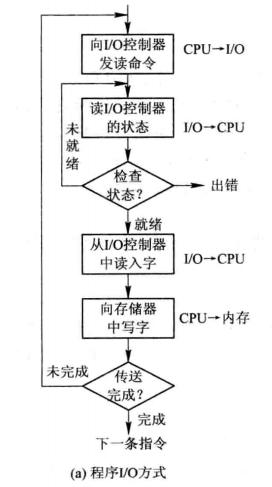

一.轮询的可编程I/O方式

处理机对I/O设备的控制采取轮询的编程I/O方式,即在处理机向控制器发出一条 I/O指令,启动输入设备输入数据时,要同时把状态寄存器中的忙/闲标志busy置为1,然 后便不断地循环测试busy(称为轮询)。当busy=l时,表示输入机尚未输完一个字(符),处 理机应继续对该标志进行测试.直至busy=0,表明输入机已将输入数据送入控制器的数据 寄存器中。于是处理机将数据寄存器中的数据取出,送入内存指定单元中,这样便完成了 -个字(符)的I/O。接着再去启动读下一个数据,并busy=1。

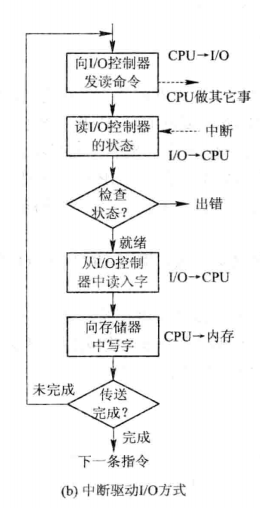

二. 使用中断的I/O可编程方式

当前,对I/O设备的控制,广泛采用中断的可编程I/O方式,即当某进程要启动某个 I/O设备工作时,便由CPU向相应的设备控制器发出一条I/O命令,然后立即返回继续执行原来的任务。设备控制器于是按照该命令的要求去控制指定I/O设备0此时,CPU与I/O 设备并行操作。例如,在输入时,当设备控制器收到CPU发来的读命令后,便去控制相 应的输入设备读数据。一旦数据进入数据寄存器,控制器便通过控制线向CPU发送一中 断信号,由CPU检査输入过程中是否出错,若无错,便向控制器发送取走数据的信号,然后再通过控制器及数据线,将数据写入内存指定单元中。

三. DMA(直接存储器访问方式)

- 特点

(1)数据传输的基本单位是数据块

(2)数据是从设备直接送入内存或相反

(3)仅在传输的开始和结束时CPU干预,其他时间控制器控制

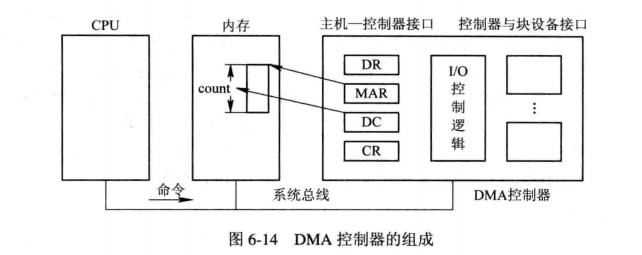

2.控制器组成

(1)主机与DMA控制器的接口

(2)DMA控制器与设备块的接口

(3)I/O控制逻辑

控制器有4类寄存器

(1) 命令/状态寄存器CR,用于接收从CPU发来的I/O命令,或有关控制信息,或设 备的状态。

(2) 内存地址寄存器MAR,在输入时,它存放把数据从设备传送到内存的起始目标地 址,在输出时,它存放由内存到设备的内存源地址。

(3) 数据寄存器DR,用于暂存从设备到内存,或从内存到设备的数据。

(4) 数据计数器DC,存放本次 CPU要读或写的字(节)数。

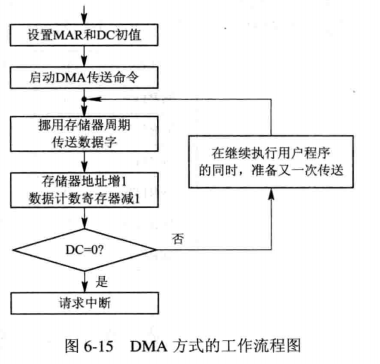

3.工作过程

四. I/O通道控制方式

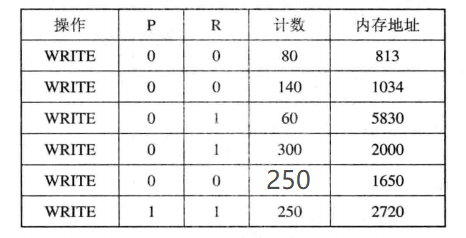

通道是通过执行通道程序并与设备控制器共同实现对I/O设备的控制的。通道程序是 由一系列通道指令(或称为通道命令)所构成的。通道指令与一般的机器指令不同,在它的每条指令中都包含下列诸信息:

(1) 操作码,它规定了指令所执行的操作,如读、写、控制等操作。

(2) 内存地址,标明字符送入内存(读操作)和从内存取出(写操作)时的内存首址。

(3) 计数,表示本条指令所要读(或写)数据的字节数。

(4) 通道程序结束位P,用于表示通道程序是否结束。P=1表示本条指令是通道程序的 最后一条指令。

(5) 记录结束标志R,R=0表示本通逍指令与F—条指令所处理的数据是同属于一个记 录:R=1表示这是处理某记录的最后一条指令。

下面示出了一个由六条通道指令所构成的简单的通道程序。该程序的功能是将内存中 不同地址的数据写成多个记录。其中,前三条指令是分别将813〜892单元中的80个字符 和1034〜1173单元中的140个字符及5830〜5889单元中的60个字符写成一个记录;第4 条指令是单独写一个具有300个字符的记录:第5、6条指令共写含300个字符的记录。

-------------------------------分界线-------------------------------

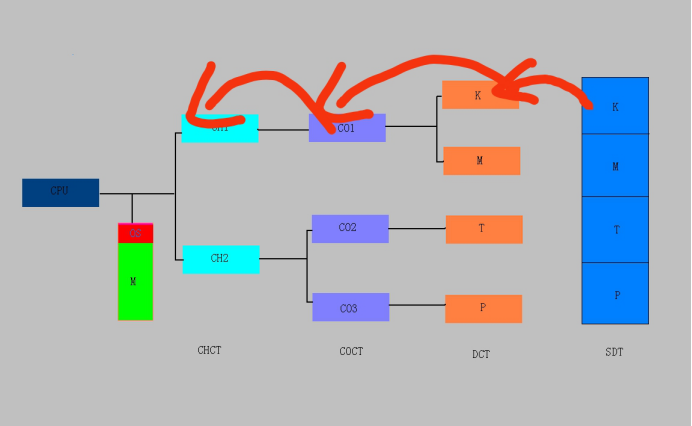

设备分配的顺序,某进程申请K,申请时的顺序为

-------------------------------分界线-------------------------------