外部引脚信号:

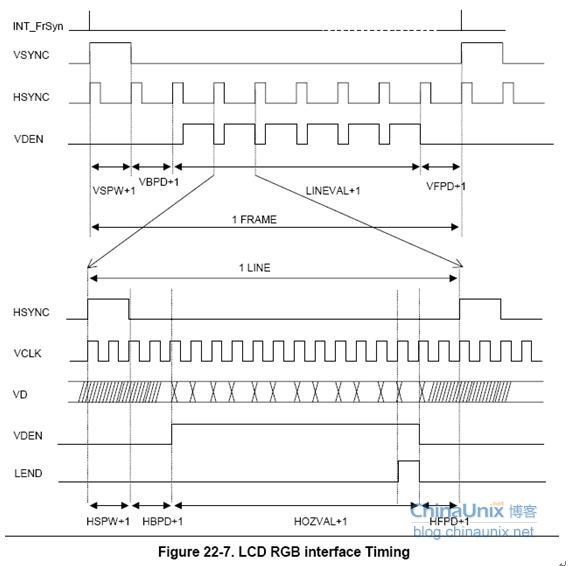

VSYNC: 帧同步信号,表示扫描1帧的开始,一帧也就是LCD显示的一个画面。

HSYNC: 行同步信号,表示扫描1行的开始。

VDEN:数据使能信号。

VD[23:0] : LCD像素数据输出端口。

VCLK:像素时钟信号。

内部参数说明:

VSPW:帧同步信号的脉宽,单位为1行(Line)的时间。Vertical pulse width (有些驱动简单vs)

VFPD: 帧同步信号的前肩,单位为1行(Line)的时间。有时缩写vfp

VBPD: 帧同步信号的后肩,单位为1行(Line)的时间。有时缩写vbp

LINEVAL :帧显示尺寸-1,即屏行宽-1,对于800*480分配率的LCD屏,那么LINEVAL=480-1=479,请记住,是屏行宽,也就是LCD屏显示一帧数据所需要的行的数目。

HBPD:行同步信号的后肩,单位为1VCLK的时间。 Horizontal back porch

HFPD:行同步信号的前肩,单位为1VCLK的时间。

HSPW:行同步信号的脉宽,单位为1VCLK的时间。Horizontal pulse width (有些驱动简写hs)

HOZVAL:行显示尺寸-1,即屏列宽-1,对于800*480分配率的LCD屏,那么HOZVAL=800-1=799,请记住,是屏列宽,也就是LCD屏显示一行数据所需要的像素(pixel)的数目。

扫描一行所所需的时间:

= ((HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1))个VCLK时间。

而一个VCLK时间由LCD寄存器VIDCON0内的CLKVAL决定:

=HCLK/(CLKVAL+1) ------>这个公式是S3C2443的LCD控制器的,其他CPU的不一定一样

因此扫描一帧所需的时间:

T=[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)][(HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1)] HCLK/ (CLKVAL+1)

判断 HSYNC,VSYNC,VCLK, VDEN信号是否需要反转

这个根据具体的手册来看。

调试总结:pclk计算 pclk=(hfp+hbp+hs+active_col)(vfp+vhp+vs+active_row)fps

问题1:这些参数,是给谁用的? dvp tx用,还是dvp rx用?调试dvp驱动,这些参数都是自动识别的。屏幕我看lvds驱动,也是自动识别的,那这些参数存在的一样如何?

转载于https://blog.csdn.net/pankul/article/details/71155768?ops_request_misc=&request_id=&biz_id=102&utm_term=video_timing&utm_medium=distribute.pc_search_result.none-task-blog-2allsobaiduweb~default-3-71155768.nonecase&spm=1018.2226.3001.4187