一般来说,时钟切换有3种手段:

1、器件本身有硬件结构支持切换

… For example, you can use the Clock Switchover feature or the Clock Control Block available in certain Altera devices.

2、使用动态PLL

… Many Altera devices also support dynamic PLL reconfiguration, which is the safest and most robust method of changing clock rates during device operation.

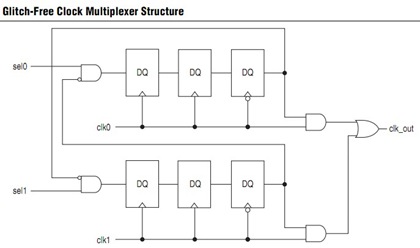

3、构造特殊的MUX

该结构的特点是:

… The design enforces that no clock activates until others have been inactive for at least a few cycles.

这个结构是没有glitch的。

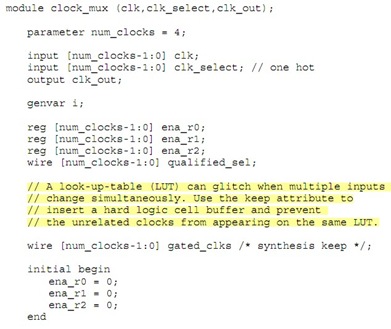

结构代码如下:

关于在这里使用synthesis keep的原因,文档说的不是很详尽,个人理解应该是防止综合工具使用LUT。

![G@%M2OP7(3]3QI4)BPB@_YO G@%M2OP7(3]3QI4)BPB@_YO](https://images.cnblogs.com/cnblogs_com/freshair_cnblog/201208/201208161838216163.jpg)