测试代码如下:

1 module led( 2 CLOCK, 3 RESET, 4 LED 5 ); 6 7 input CLOCK; 8 input RESET; 9 output reg [3:0] LED; 10 11 always @(posedge CLOCK) 12 begin 13 if(RESET) 14 LED <= 4'h0; 15 else 16 LED <= 4'hf; 17 end 18 19 endmodule

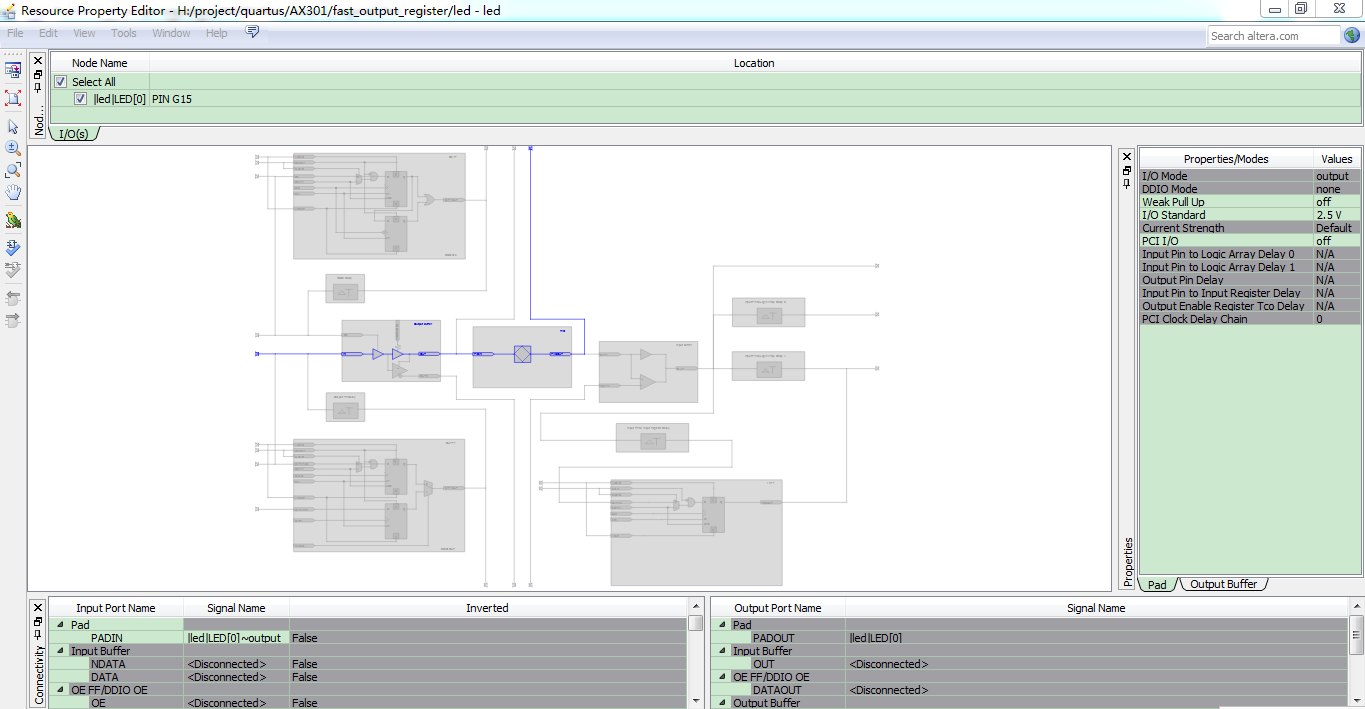

在quartus中设置fast output register方法是:Assignment Editor - 找到管脚 - 选Fast Input/Output Register - On,如图所示:

下图是没有设置fast output register的Route结果:

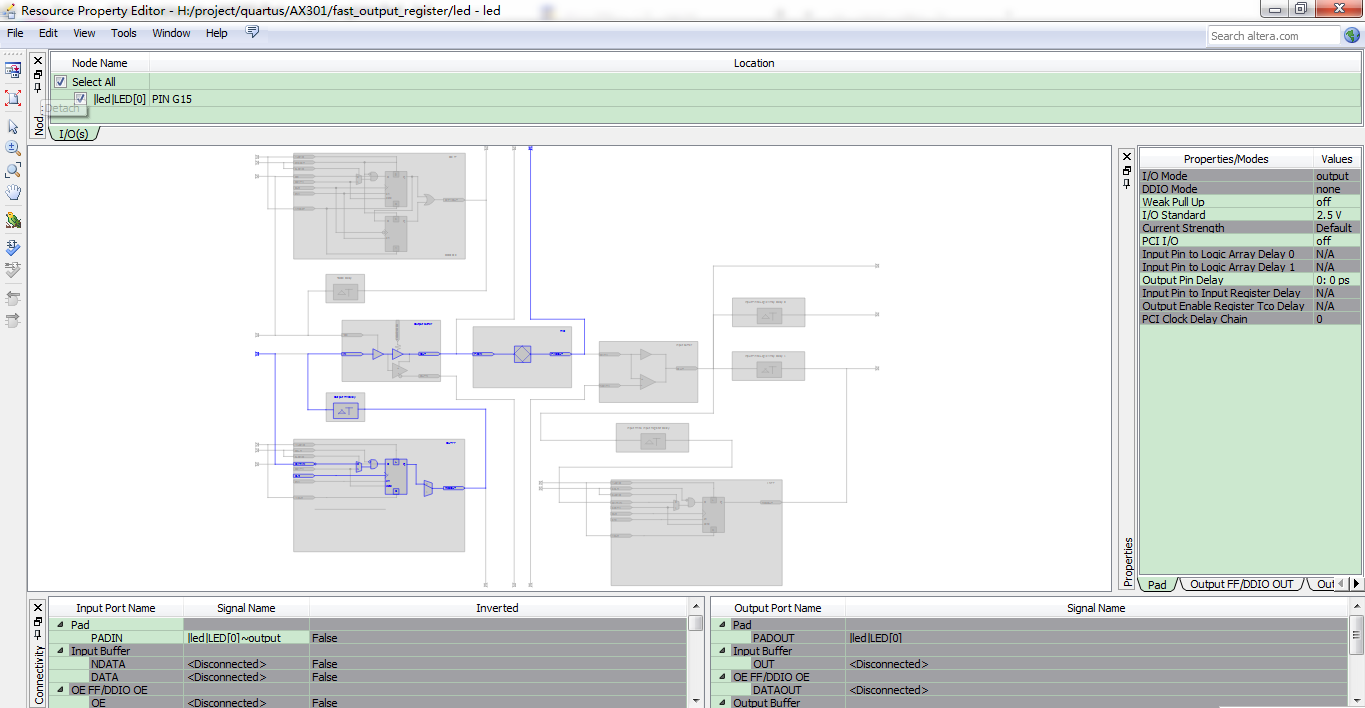

下图是设置fast output register的Route结果:

可以看到两者的不同之处在于设置了fast output register会使用左下角的OUT FF,这个就是fast output register。从这个register输出到PAD的延时相对固定,所以如果输出是多路并行输出,使用fast output register可以使并行数据输出的延时基本保持一致并且相对固定。

在Xilinx中具有类似功能的是IOB register,在Vivado中设置IOB register的方法之一是在代码中增加(*IOB = “TRUE”*),例如,把代码输出部分改为:

(*IOB = "TRUE"*) output reg [3:0] LED;

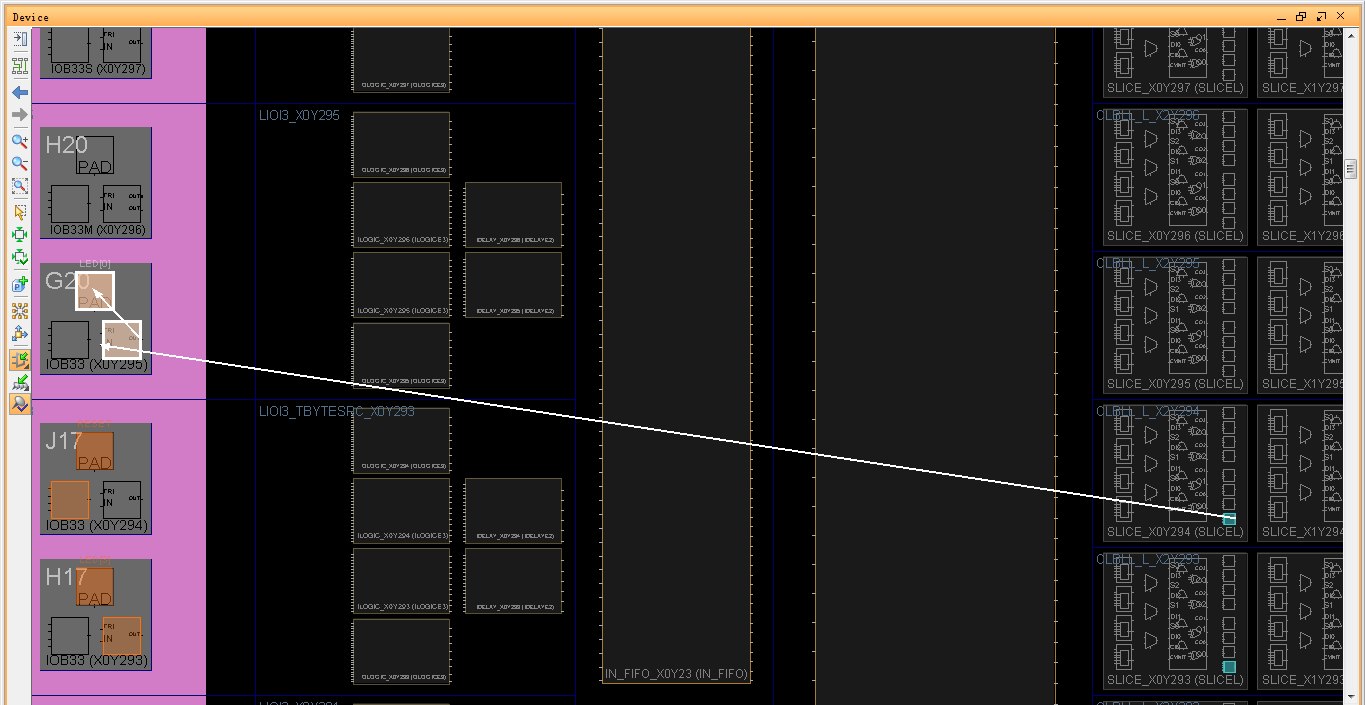

下图是没有设置IOB register的Route结果:

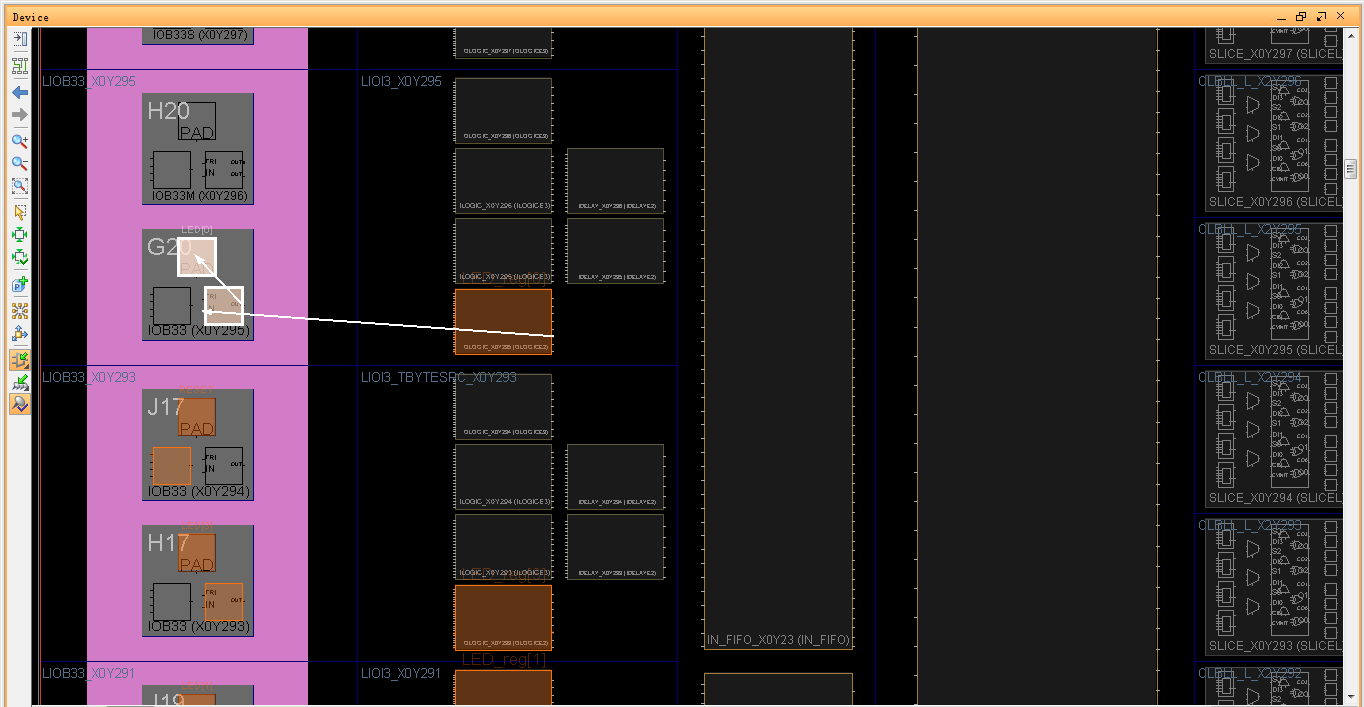

下图是设置IOB register的Route结果,与上图对比可以发现register被放置到了IOB中。

总结一下,当输出数据是多路并行数据时,可以使用fast output register或IOB register来使并行数据之间的延时基本保持一致并且相对固定。输入同理。转载请注明出处。