MAX10 是Intel FPGA的CPLD中的一个特殊的芯片,因为它内部有CPLD的Flash结构,也有FPGA的Ram结构。具体的可以参考MAX10 Handbook文档。

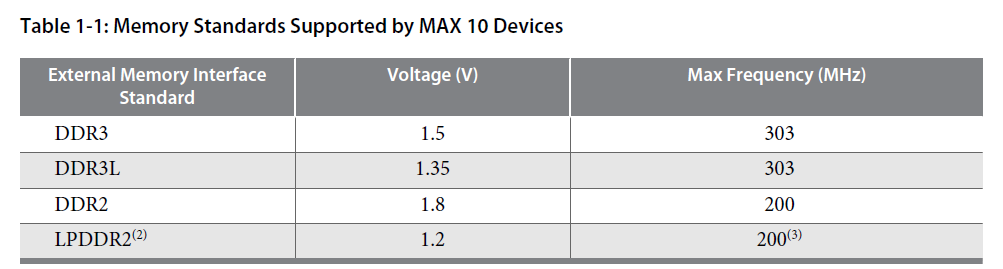

Max10 在外部存储器方面不但支持DDR2,还支持DDR3和LPDDR2。 不过需要注意的是并不是所有的芯片都支持DDR3和LPDDR2的,只有-6等级的芯片才支持DDR3和LPDDR2,而且速度也有要求,大于300MHZ,小于303Mhz。另外最大支持24bit(16bit data+8bit ECC),放置的位置为右边的Bank5/6, PLL使用的是右上边的PLL。

这里不说DDR3的IP核如果使用,就说工程建好之后遇到的一个错误如何解决。

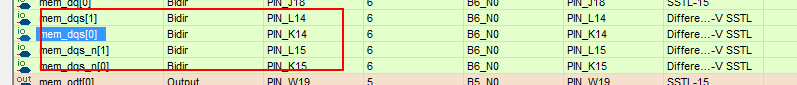

含有DDR3 IP的工程建成之后,绑定Pin的时候,在绑定的DQS pin之后,DQSn pin就会自动的绑定,如下图:

编译之后,布局布线的时候出现一个错误,如下:

Error (13130): The assigned location PIN K15 for DQSn pin "mem_dqs_n[0]" is not a legal location Info (13132): There is no legal DQSn location for the DQSn pin.

Error (13130): The assigned location PIN L15 for DQSn pin "mem_dqs_n[1]" is not a legal location Info (13132): There is no legal DQSn location for the DQSn pin.

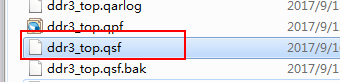

这个需要将DQSn的pin绑定给 注释掉, 原因不知道, 只有MAX10上的DDR3 IP需要这么做,其他的器件不需要。 打开.qsf文件,将DQSn的绑定 pin 的 那句命令用#号 绑定注释掉。

然后如下图所示:

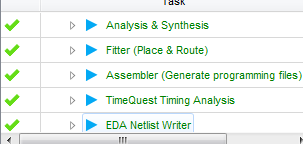

然后编译通过。