最近在调试LATTICE FPGA 做的视频板子,颇不顺利,所以记录下来作为以后的参考:

1、FPGA的IO口不是所有的都是双向的,有些有特殊作用的是单向的。

在查阅 LatticeECP3-17EAPinout.CSV 之后, 发现在LEF3-17EA-FN484C中,有以下几个管脚是单向的:

C4 G7 G6 : jtag 管脚

C14 C15 B15 B16 :编程管脚

K1 L5 L1 K6 N17 M18 :PLL的反馈(fb)管脚

AB2 AB3 : RESERVE

N15 : XRES

其中最容易被用掉的是 PLL的反馈管脚,要格外注意。其他的型号和封装可以参考相应的 .CSV 文件。

否则提示错误: ERROR : the output port XX is assigned to an input dedicated pins [M18] .

2、在将程序下载到外部spi flash时,设置完成之后提示错误:

其中有 Except Device ID 0x04002310 READ:0X0000000; 则是说没有读到芯片的地址,则有可能是连接flash的读入线(相对FPGA)有问题。

尤其要检查是不是输入和输出线连接反了。

3、在下载程序到FPGA内部时,浏览芯片出现错误,或下载的时候出现错误,提示也如同上面的错误,就是读不到芯片的 ID, 那么可能是JTAG的四根连线出现问题,要详细检查。 例如我的是在TMS线上接了一个对地100nf的大电容,则把波形都滤掉了,所以出现错误而读不到数据。

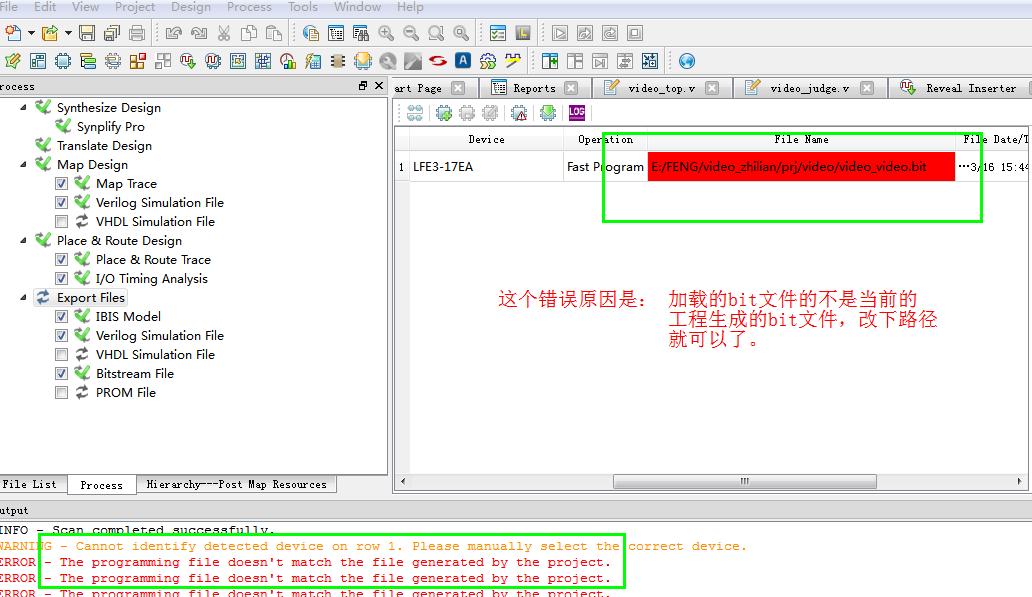

4、lattice Diamond 在下载的时候 加载bit文件的时候,由于这个软件不会自动寻到正在编译的工程目录下,所以加载的bit文件可能是上个工程的路径,这样软件就会报出一个错误:

这个原因是下载文件的路径有问题,改为你当前工程的路径即可。

5、关于lattice DDR3 IP 核的wl_err信号的调试:

lattice 的DDR3 IP核 在调试的时候要注意,硬件上电之后,DDR3 要复位 200us之上,如果时钟是74.25M的输入,则需要计数达到3000个clk,才可以开始初始化。如果是仿真,当然不需要那么久了,假设仿真时钟是6666ps,就是核内部demo的仿真参数,则如下所示

`timescale 1 ps/ 1 ps parameter c = 6666; always #(c) clk = ~clk ;

那么 复位的时钟个数计数只要达到100个就可以了(demo 是200个clk周期)。

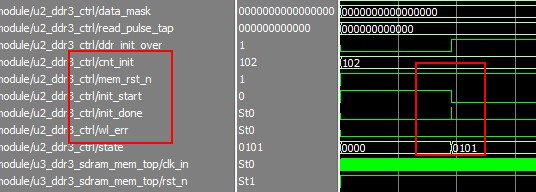

那么正确的wl_err的 信号在初始化的时候的波形是这样的:

就是在init_done 有效的时候,init_start被拉低,wl_err信号保持为低电平,表示核初始化写调整没有错误,可以正确的读写。

但是吧,有一天,我感觉 c = 6666; 这样太长了,仿真太慢了,于是我又把C调整为 c = 666; 或者 c 更小 ,我想这样是不是只要延时时间一样长,

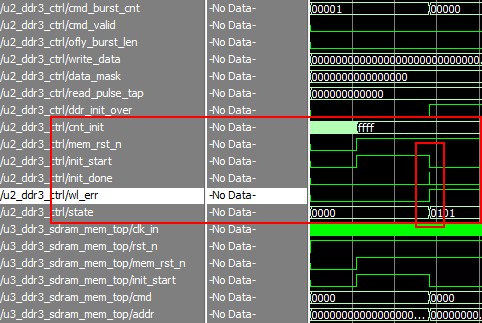

就可以完成初始化了???于是我就实验,将c= 666,计数记到 100,甚至 16‘hffff,最后发现wl_err的波形在初始化完成时都是下图这样的:

在init_done有效的时候,wl_err被拉高,且一直保持,这就是说,核初始化过程中写调整有错误,这样的结果是——导致核的读操作不能被有效的

响应,就是度有效之后,不能读出数据 。当然这个核是没法仿真的了。 猜测 可能是 时钟的 频率 太快了。

最后没办法,老老实实把 c改为6666 吧。