坑,,以后填

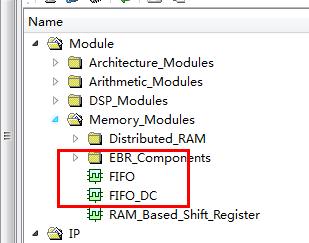

对于Lattice 的 FIFO 存储器分为两种,见下图:

这两个的主要区别是一个后面加DC一个不加,那这个DC是什么意思呢??DC这里是Dual Clock的意思,也就是双时钟的意思,那意思就很明显了,另一个是单时钟;更本质的可以说单时钟是同步FIFO的意思,双时钟是异步FIFO的意思。

同步FIFO:

一、先看datasheet

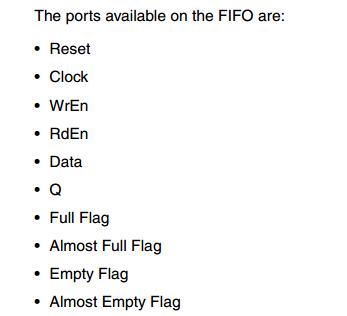

显示端口说明:

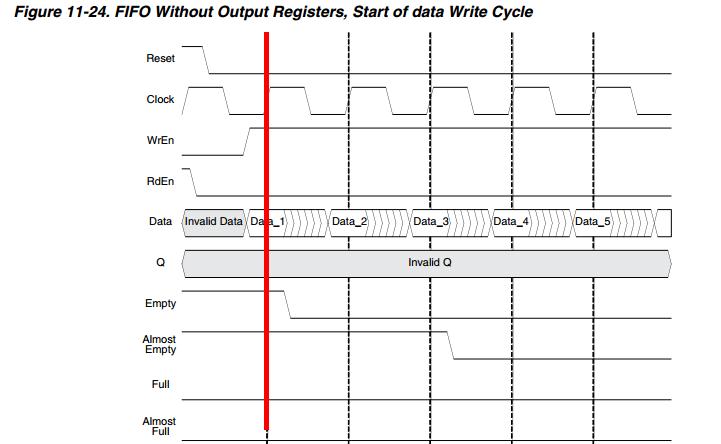

没有输出寄存器时的写操作,可以看出,写操作是在clk的上升沿的时候将 写请求使能有效且写数据准备好即可。写入数据之后empty就会被拉低。

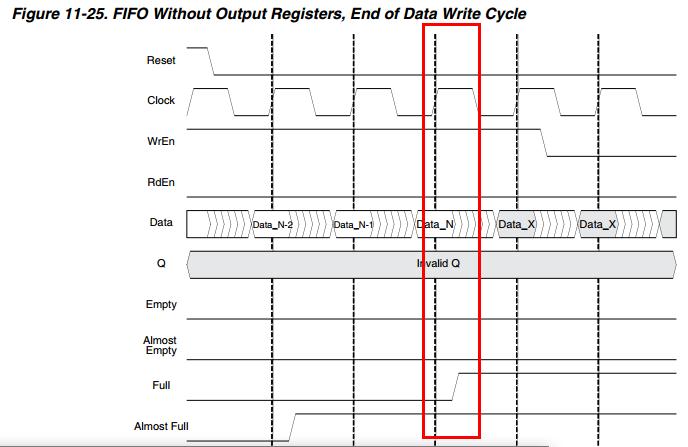

上图显示写满之后再写数据就无效了。

读时序:

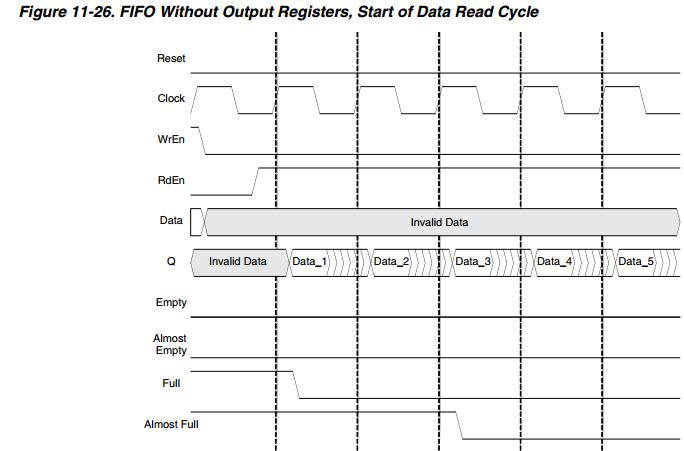

上图可以看出,在写使能有效的一个时钟周期之后数据才送出Q端口。

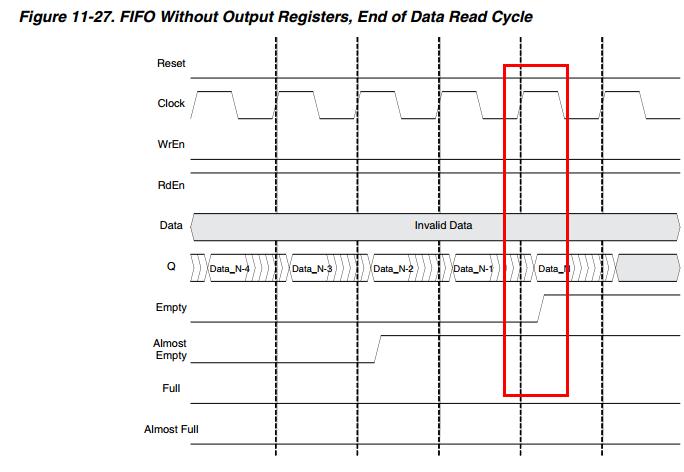

当最后一次读取数据的时候,empty信号会被拉高,然后一个时钟周期之后数据从Q端口送出。

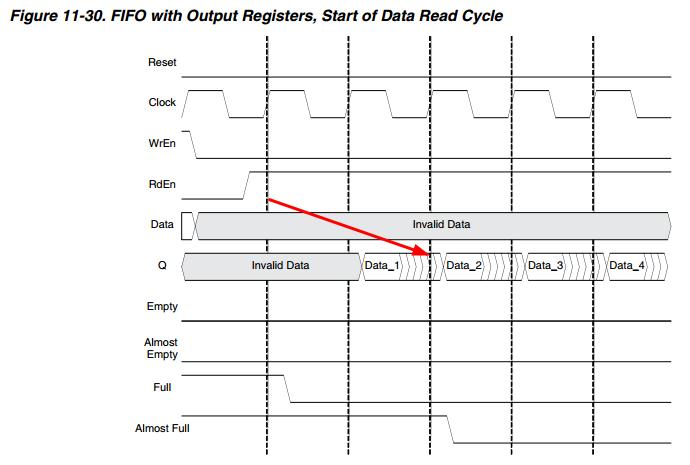

在输出端口使能了输出寄存器之后,对FIFO的写操作没有影响,只是对读操作有影响,具体影响是:在原来的基础上又延时了一个时钟周期。

最后需要注意的是:

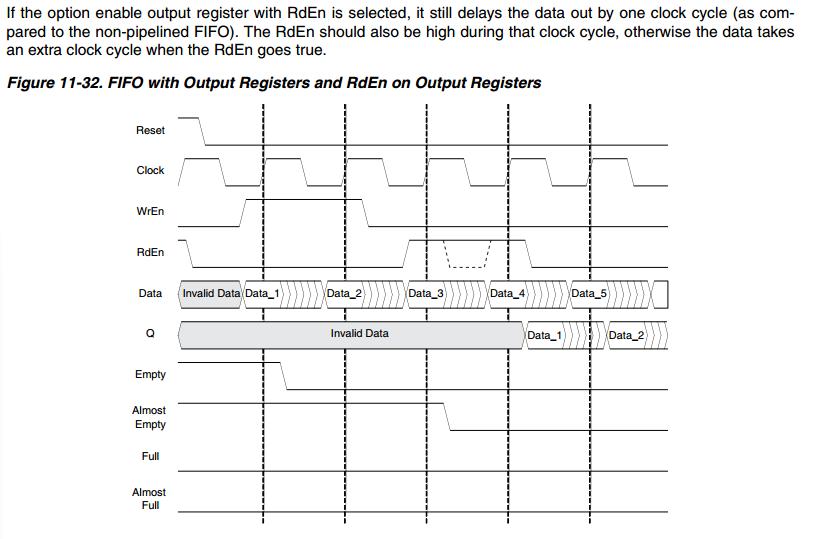

这个操作和生成FIFO的设置有关系。

现在就看FIFO生成的时候的设置吧:

首先是名字和路径以及语言的选择,直接跳过。

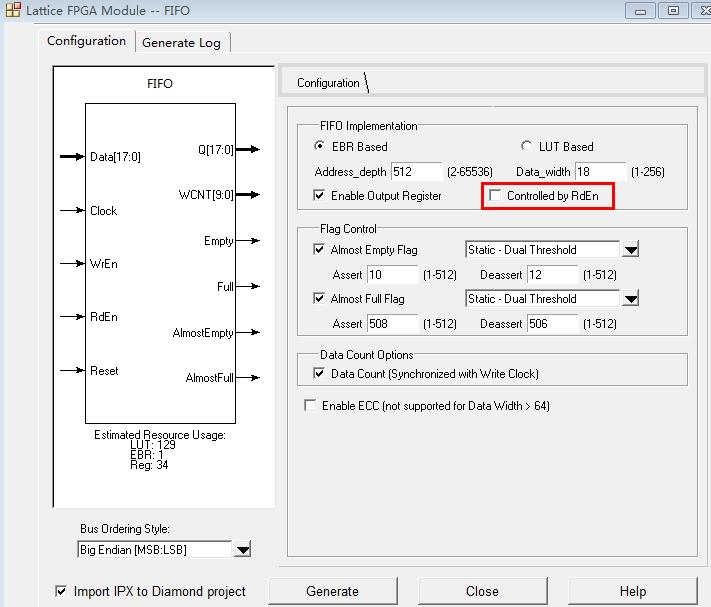

打开后界面如下:

界面设置也很简单, 先是FIFO的类型,默认即可;地址深度就是存多少个数据,这里深度只能是2的幂即2的n次方;数据宽度可以任意选择,默认输入和输出的深度宽度是一样的。Enable output reg选项就是使能输出寄存器选项,选择之后就是输出端数据延时两个时钟周期输出。

Controlled by RdEN 选择时候,读取的时候时序图就是上面最后一个时序图的时候。

设置输入满,输出空的阈值;设置显示内部数据个数。

最后选择左下端的Import IPX to Diamond project 选项之后,生成的FIFO文件会直接加入到工程里面去。

同步FIFO就到这里。

异步FIFO

异步FIFO与同步FIFO有所不同,

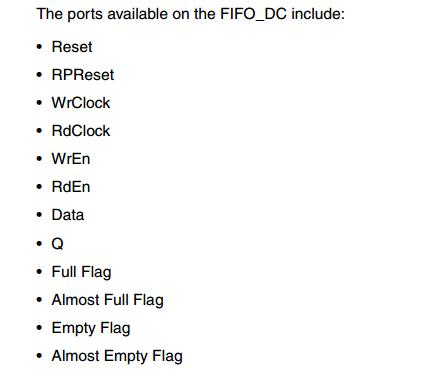

先是端口:

可以看出它有两个时钟,但是本质其实和同步FIFO相似,可以看做为两个同步FIFO,在不同的时钟驱动下一个只进行读操作,一个只进行写操作,读写单独操作互补影响,这里不做时序图的介绍和记录了,直接看生成时候的设置界面。

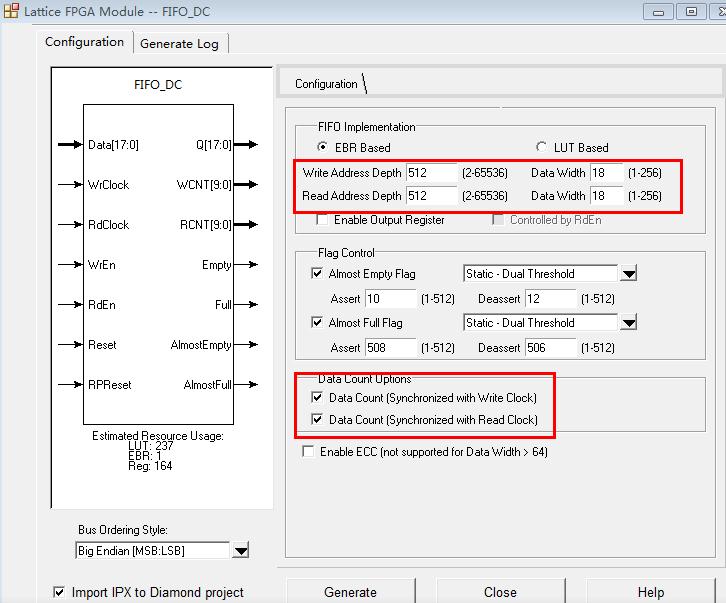

可以看到 上图两个红色方块内是两个不同之处,上面是读和写操作都要设置FIFO的存储深度和数据宽度。 而且深度要是2的幂。

最重要的是要确保输入的深度乘以数据宽度要等于输出的 深度乘以数据的宽度。否则生成不了FIFO。

下面方框内是数据的计数,读写数据分别计数。在写数据的计数增加之后,读数据的计数也会在读时钟作用下相应的增加。