1、参考

UG585

网络笔记

参考:ZYNQ进阶之路14–PS端uart串口接收不定长数据

2、理论知识

参见上一次实验:基于ZYNQ 的UART中断实验之串口写数据到DDR3中

3、实验目的

基于ZYNQ 的UART中断实验,这里在上一次实验的基础上将发送固定的数据改为可以发送不定的数据。

4、实验过程

建立工程,设置并初始化串口中断,在运行程序之后,如果串口接收的数据达到了RXFIFO触发的中断则会产生中断,zynq会将数据搬移到一块recvbuffer中,另外如果在接收到一定的数据之后(没有达到rxfifo中断level),如果在规定的等待一定时间内还没有新的数据接收到则也会产生中断通知ZYNQ去读取,这也标志本次数据已经完全读取完了。可以处理数据了。

5、实验平台

Microphase ZUS zynq7020 开发板。 串口使用 uart1[48,49]. DDR选择 MT41J256M16 RE-125,32bit. BANK1 = 1.8v.

6、Vivado 建立工程

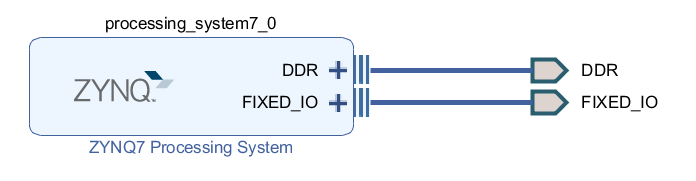

block design 如下: