区别与verilog HDL代码,主要留意以下内容:

1,语言本身支持的特征和可综合的代码是两回事,不是所有verilog语言都可以转化为硬件的。

2,testbench作为top module,不需要任何输入和输出。

3,在testbench module中将要测试的模块例化为dut(名字可以任起),input要是reg类型,output要是wire类型,inout是reg。

4,initial和always是同时执行的,只是initial只执行一次。

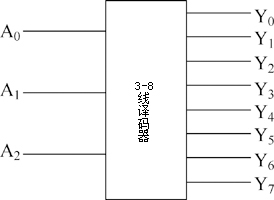

一.38译码器框图

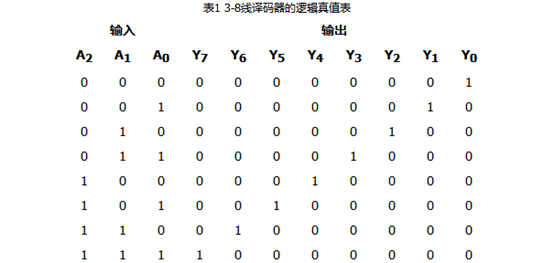

二、真值表

创建工程:

按照真值表定义编写Verilog程序:

module my_38(a,b,c,out);

input a;

input b;

input c;

output reg [7:0]out; //定义一个8位的位宽.只要是在always块中进行赋值的都要定义为reg类型。

always@(a,b,c)

begin

case ({a,b,c}) //{}位为位拼接,将信号拼接成一个三位的信号

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100_0000;

3'b111: out=8'b1000_0000;

endcase

end

endmodule

编写testbench测试文件:

`timescale 1ns/1ns

module

my38_tb;

reg a,b,c;

wire [7:0]

out my3_8 u1(

.a(a),

.b(b),

.c(c),

.out(out)); //顶层例化

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

$stop;

end

endmodule

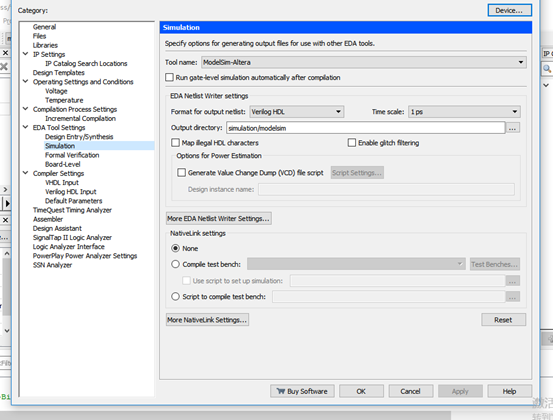

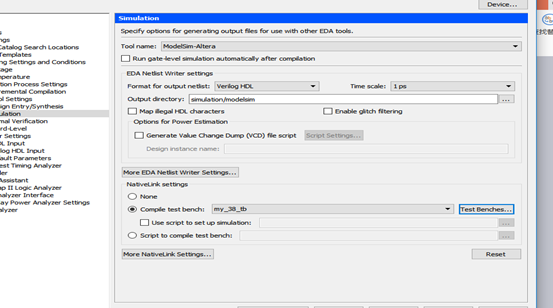

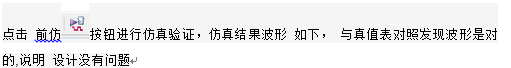

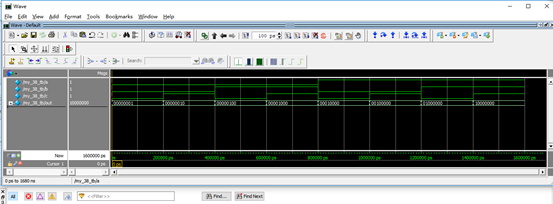

将testbench文件链接到仿真工具

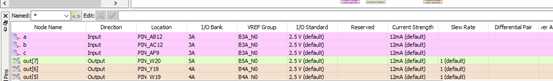

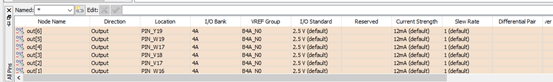

分配引脚

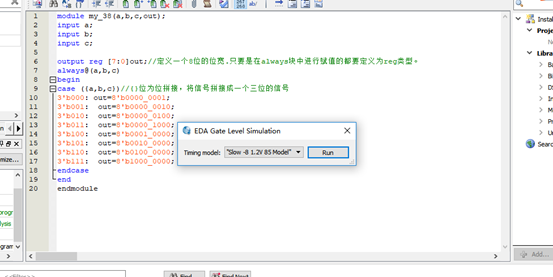

点击全编译按钮后,上电链接开发板,点击programmer,将系统生成的.sof文件烧写到开发板中。

本次实验中,testbench是用initial块给信号赋初值,initial块执行一次,

首先在写testbench时,应注意名称要和自己待仿真的工程名称要对应,比如自己的待仿真文件名称叫my_38,那么对于teshbench的名称则取一个叫my_38_tb,在书写testbench module name则取名叫my_38_tb,这样对于自己有好处,以免自己找不到自己写的文件。