本实验使用DE1器件,cyloneV,主要做的基础实验,目的是回顾前期的学习和巩固知识和熟悉操作流程。

视频主要学习的是小梅哥视频。

工程文件夹取名

- prj ----- 工程文件存放目录(ip文件夹存放生成的ip核文件)

- rtl ----- verilog可综合代码

- img ----- 设计相关图片存放目录(方便写文档)

- doc ----- 设计相关文档存放目录

- testbench ----- 对应的testbench仿真测试文件存放目录

初学者FPGA开发流程:

1、设计定义;

2、设计输入;(quartus II)

3、语法检测,分析和综合(quartus II检查);

4、功能仿真;(modelsim-altera仿真)

5、芯片布局布线;(开发软件对芯片布局,会生成逻辑图);(quartus II检查);

6、时序仿真;(逻辑仿真是零延迟的,实际中会有延迟);(modelsim-altera仿真)

7、时许约束。

8、分配引脚;I/O分配;配置文件的生成;(quartus II检查);

9、配置(烧写FPGA);

10、在线调试。

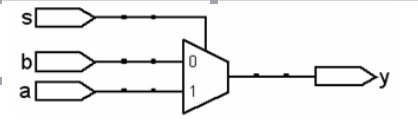

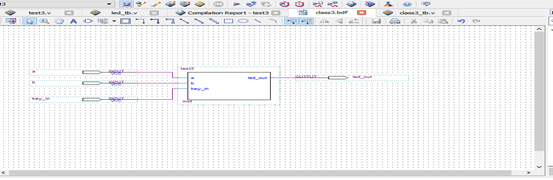

例1:2选1多路选择器

设计定义:两个I/O,a为低电平、b高电平。

输入按键按下,led灯与a端口输入一致。

没有按按键,led灯与b端口输入一致。

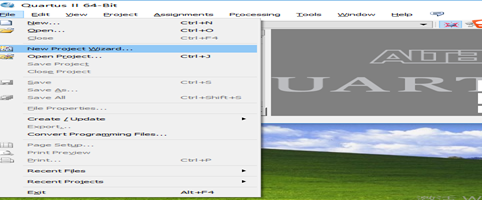

设计输入;(quartus II)

- 创建工程

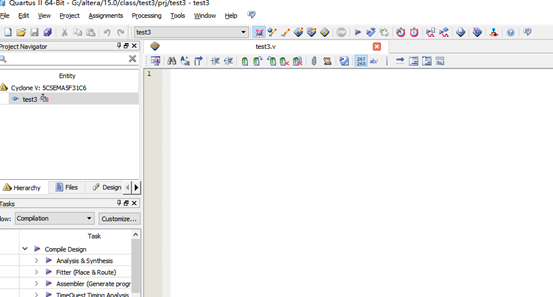

选择文件夹,选择器件和型号:根据所用开发板选用;选择EDA工具:

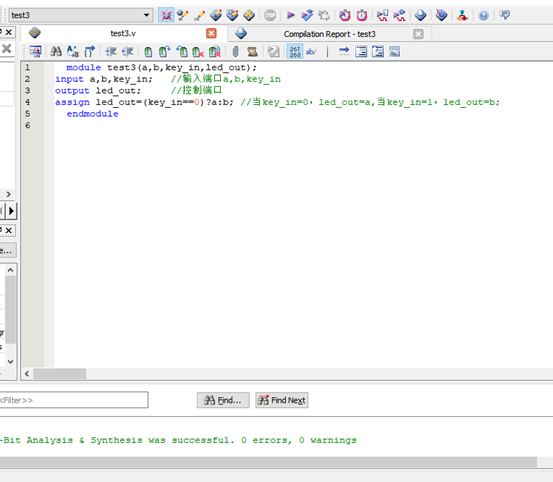

保存时文件名要与工程名一致,写程序,并检查有无语法错误:

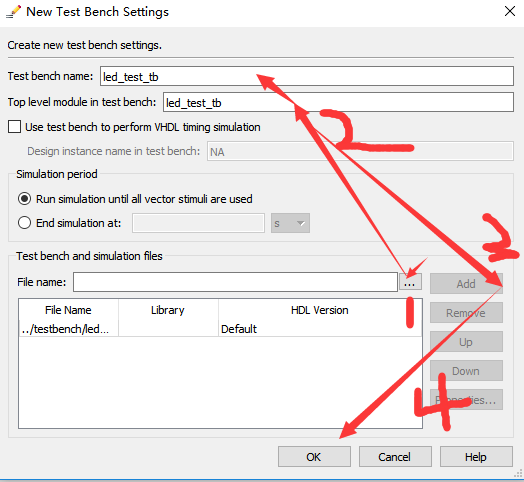

- 功能仿真;(modelsim-altera仿真)

新建

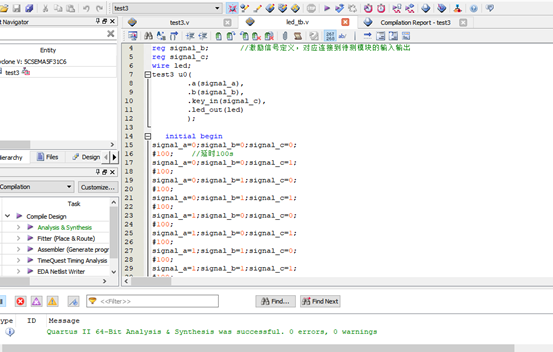

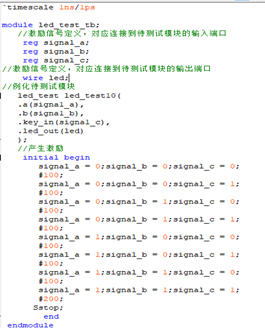

`timescale 1ns/1ps

定义时间精度;

100.1 //仿真精度1ps,仿真时间为100.1ns;

`timescale符号为:

保存新建程序

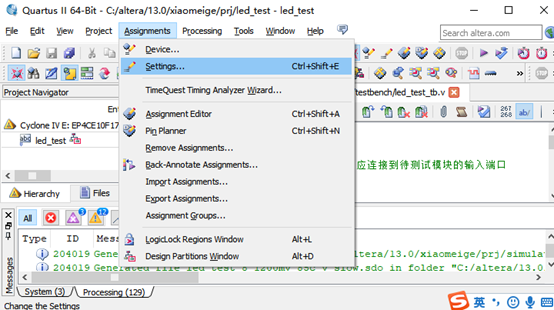

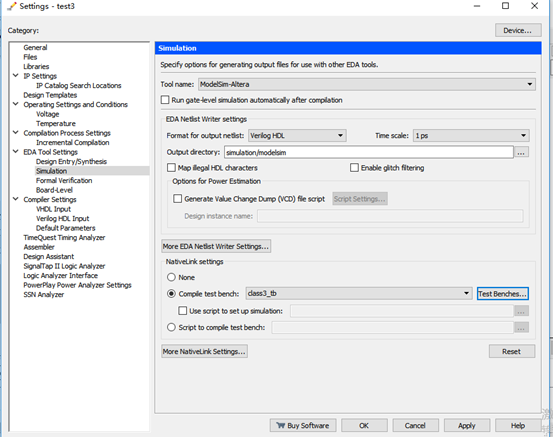

将模块告诉modelsim-altera,要设置脚本;

仿真

出现报错,路径错误

设置路径。

最后在quartus中设置modelsim的路径,quartus->tools->option->EDA tool options ,在右边选择modelsim_altera的安装路径

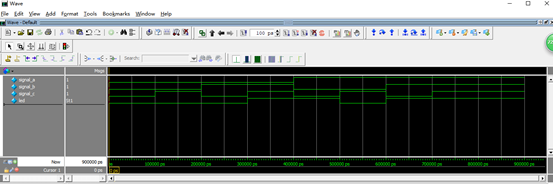

仿真波形如下,前仿:

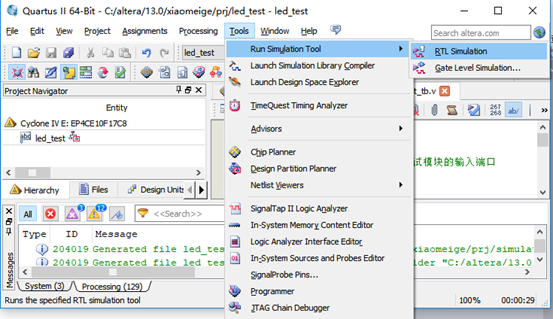

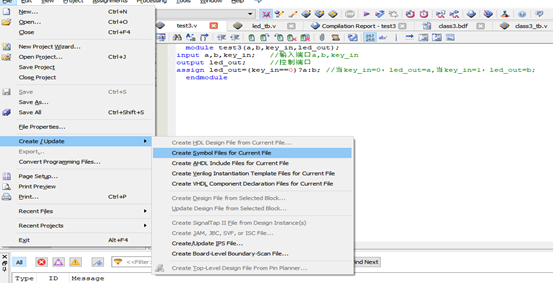

后仿:先点击class3;

为顶层的代码编写一个testbench

点击Get level simulation

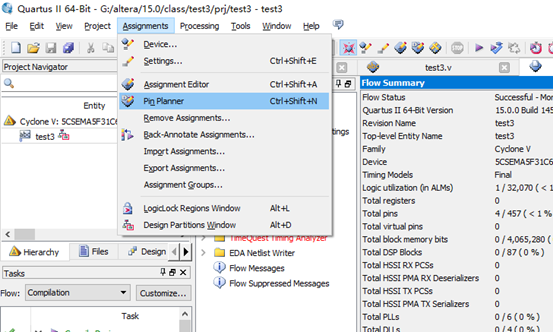

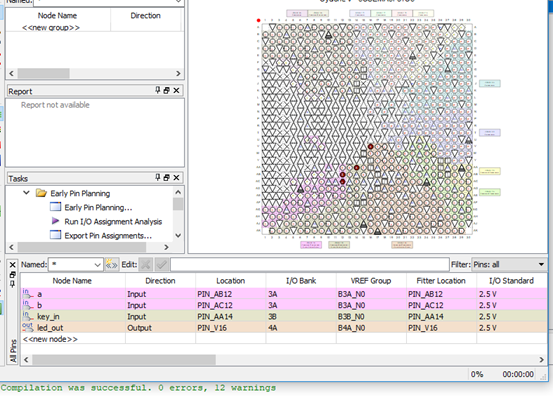

分配引脚:

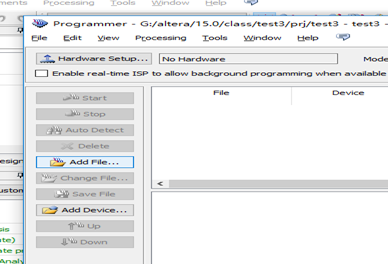

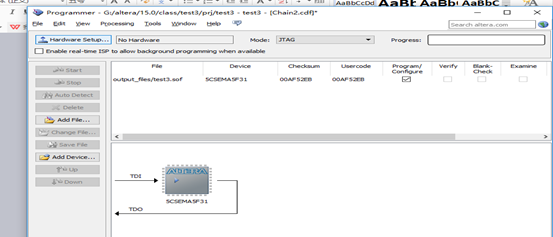

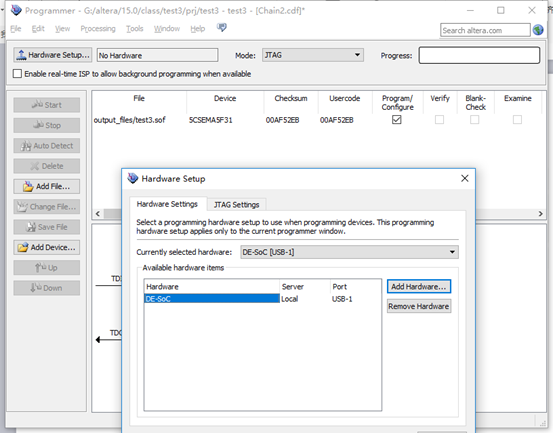

全编译后,点点击programer键即可打开下载界面。点击Hardware Setup

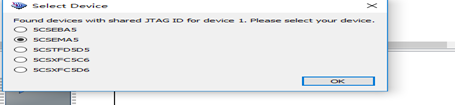

然后点击autodetect,选择FPGA设置,FPGA和HPS装置会出现在JTAG chain里面

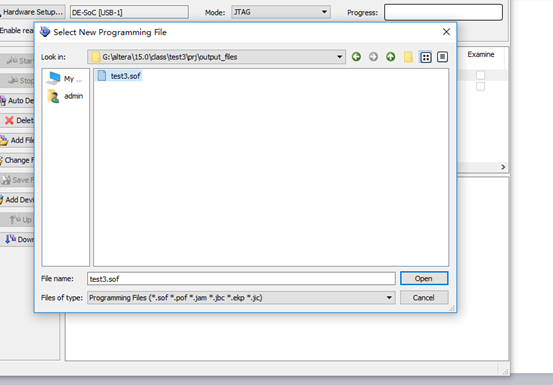

选定器件后右键,选择Change file

实验运行