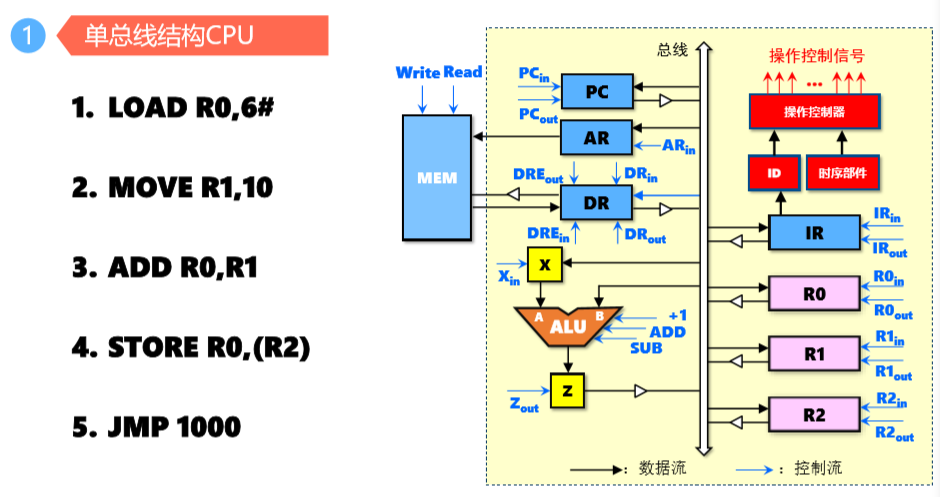

1、单总线结构CPU

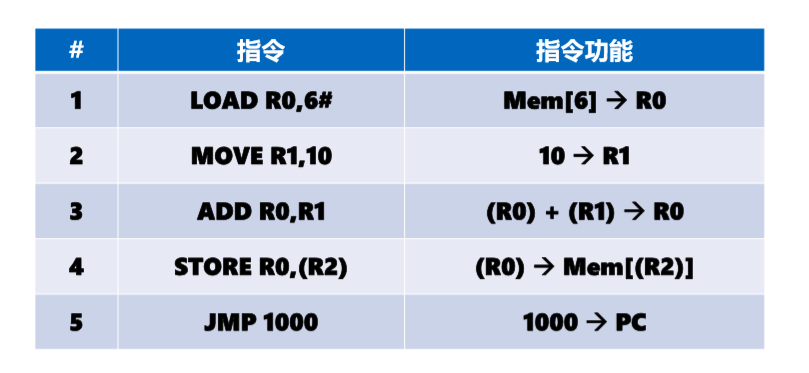

首先说一下取指令如何完成:

首先将PC的值取出,这个动作我们需要给出一个PC out的信号,控制三态门值输出到总线,然后再由总线输入AR中,同样需要一个ARin的写使能控制信号,在下一个时钟到来时,就会将对应的PC值输入到AR,同时PC的值要完成加1的操作,通过总线传输到x端,同样需要一个Xin的控制信号,时钟到来后,PC的值就会写入X中,这是第一个时钟干的事,就是将PC的值存入AR和X中。

下一个时钟周期,我们要干什么呢?我们要通过AR来访问内存,同时将PC的值加1,具体操作就是,给ALU的运算选择信号+1,让pc的值加上1送到结果Z,要想让结果写入Z,必须在时钟到来后才可以,因为Z没有写使能,所以时钟到来后,一定会锁存。同时在内存处,给出读信号,主存就可以进行相应的工作,这是第二拍。

第三拍,我们要将PC运算的结果Z的值送回PC,并且我们要把内存中对应的数据写入到DR中。首先将Z的值送回PC,给出Zou信号,将Z的值传输到数据总线,再给出一个PCin,等第三个时钟到来后,Z的值就会写入到PC中了,然后将主存中的数据写入到DR中,给出DRin信号,当第三个时钟到来后,数据就写入到DR中了。

第四个时钟周期,需要把DR写入到IR,我们给出DRout,将DR的值写入到总线,再给出IRin,第四个时钟到了后,就会把DR的值写入到IR中。到此取指令就完成了,然后再将指令送到指令译码器生成操作控制信号,由时序产生器控制时序,由操作控制器产生各功能部件所需要的控制信号序列,这些都是执行指令的事了。

下面,以LOAD R0,6# 指令为例,详细讲下执行指令的具体过程,这条指令的作用是将6号存储单元取出以后送到R0中,因为6是存在指令里边的,所以将6从指令寄存器的地址码部分取出,然后访问主存,最后将对应的数据送到寄存器中,首先我们应该把6从IR中取出来,把6送入到AR中去访存,具体操作是给出IRout信号,将6输出到总线,送到AR的输入端,给出ARin,当第一个时钟到达后,就可以将6写入到AR中,当6在AR里,下一步就给出内存读信号,当第二个时钟到达后,就会锁存,内存就会开始读,第三拍我们就将数据取出,送到DR中,需要给出DRin信号,第三个时钟到达后,就可以将数据写入到DR中,在第四拍时,需要将DR的值送入到R0寄存器,给出DRout信号,将DR的值输入到总线,然后给出R0in,在第四个时钟到达时,将DR的值写入到R0中

,指令执行结束,现在R0中存放的就是6号单元的数据。

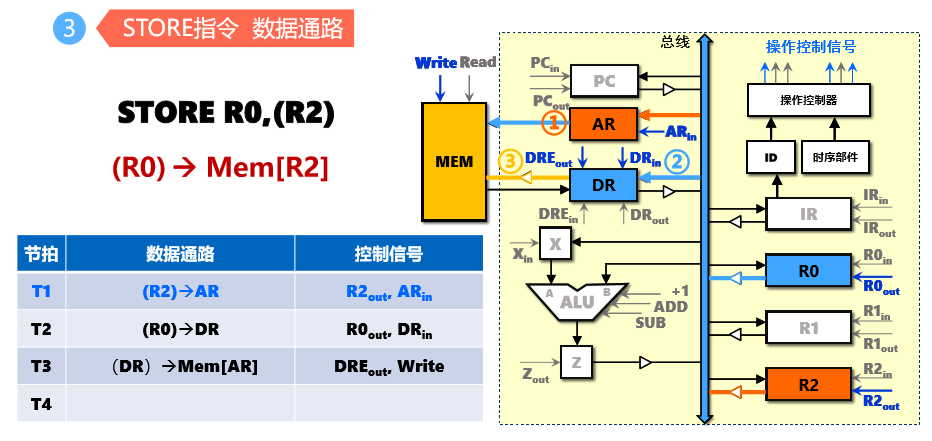

1、MOVE指令执行数据通路

2、ADD指令执行数据通路

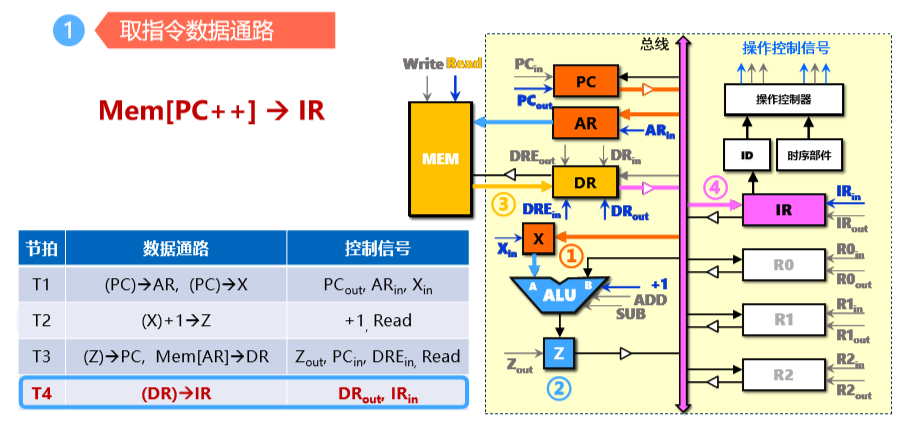

3、STORE指令 数据通路

4、JMP指令数据通路