重点:门控时钟和操作数隔离

1.并行与流水的选择

并行与流水都是用面积换速度,但是有时可以降低功耗

并行处理常用于数字信号处理部分,采用并行处理,也已降低系统工作频率从而降低功耗

用两个乘法器取代原设计中的一个乘法器,时钟频率会降低,系统整体功耗也会降低。

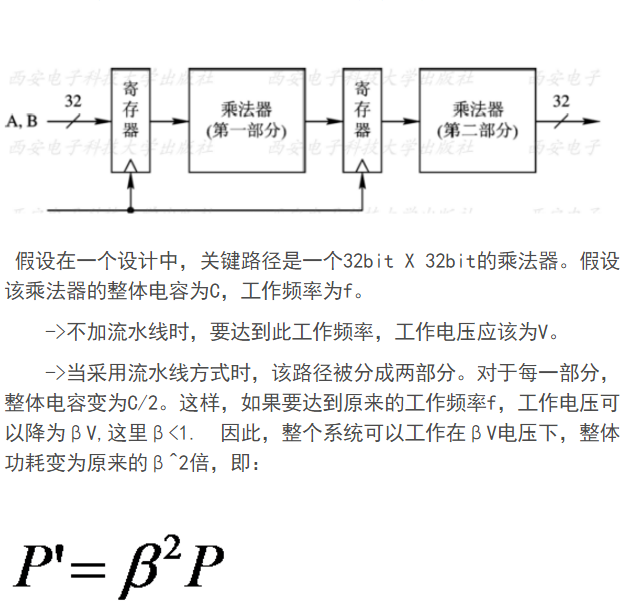

流水线技术是将一个较长的组合路径分为M级流水线。路径长度缩短为原始路径长度的1/M。这样一个时钟周期内充/放电短融变为C/M。如果在加入流水线之后,时钟速度不变,则一个周期能只需要对C/M进行充/放电。因此在相同的速度要求下,可以采用较低的电源电压来驱动系统,系统的整体功耗可能会降低

2.资源共享与状态编码

利用数据编码来降低开关活动(例如,用格雷码比用二进制码翻转更少,功耗更低)

3.操作数隔离(operand isolation,简称OI)

可以通过EDA工具来实现

1.如果在某一段时间内,数据通路的输出是无用的,则将它的输入置成个固定值,这样,数据通路部分没有翻转.功耗就会降低.不过这种做法会增加面积,影响到DFT

2.在使用compile命令进行综合时,如果手动指定的IO物体满足前面的三点:

1.OI物体是算术运算器或层次组合单元。

2.OI物体的输出是选择性地使用。

3.运算器必须有非零的翻转率。

那么综合器就会进行操作数隔离。

3.实现操作数隔离需要插入相应的隔离逻辑,比如与门或者或门之类的。

4.门控时钟(注意和使能时钟的区别,门控时钟降低功耗,而使能时钟不能降低功耗)

注意。使用的是锁存器。

这种方式消除了EN与CLK组合产生的毛刺对门控时钟的影响。该方法的原理在于:锁存器在CLK为低时透明。这样,EN 信号上的毛刺仅出现在CLK的低电平处,EN1与CLK进行与操作,可以将这部分毛刺消除掉。这样,GCLK上就没有毛刺了。

这里粘一下锁存器和DFF的区别

锁存器:电平敏感;DFF:边沿敏感

if和case不全的时候很同意产生latch

区别:

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch容易产生毛刺(glitch),DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

4、latch将静态时序分析变得极为复杂。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

latch优缺点:

latch的好处:

因为使用latch可以timing borrow,在高速电路设计中(timing会很紧),有时候就需要用latch。

latch的缺点:

1. latch是电平触发,无法实现同步操作,与我们正常的时序逻辑电路设计思路不符。

2. latch会对输入电平敏感,受布线延迟影响较大,比较容易导致输出有毛刺产生。

3. latch会导致静态时序分析和DFT会很复杂。

4. 在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

所以ASIC中一般用latch,fpga中一般用DFF,或者没有时钟的时候用latch

timing borrow:比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。