Xilinx S6 PLL 重配置工程概述

一.思路说明

官方配置过程:官方大概是这么配置的,在rom中初始化2组参数,通过顶层模块的STTEP和STATE以及SRDY信号控制配置过程。上电后等待SRDY有效(1clk)之后,使能STTEP(1clk),在STTEP有效的前提下,判断STATE的值是1或者0,从而选择哪组参数有效,实际上最终是由状态机来完成对PLL寄存器读写的,状态机请参考pll_drp_modify.v文件。

修改说明:由于我们要动态配置PLL,且要求灵活性较高,故采用RAM的存储数据,这样便不需要指定两组或者多组参数了,且将参数的值例化为顶层模块的输入,使用的时候可以用单片机配置fpga的寄存器,单片机计算相关参数的数值通过协议发送给fpga,由FPGA最终完成配置,参数的计算,请参考官方的pll_drp_func.h文件,工程已经转换为.c文件供参考。

二.使用说明

使用工程下的C计算参数参考文件中的<参数计算_exc_pll_cal.c>文件,传入对应的值后就可以运行得到相关的参数,然后将这些参数写入到fpga对应的测试文件中,目前仿真已测试。

三.部分C函数使用说明

- void s6_pll_lock_lookup(u8 divide, LOCK * p);

使用说明:该函数主要是设置值PLL检测锁存的能力,第一个参数用来设置CLKFBOUT+MULT的属性,取值范围:1-64,第二个参数是传入结构体的地址,因为这个是40bit的,由32bit+8bit构成,这里用了结构体数据类型。

- u16 s6_pll_filter_lookup(u8 divide, char *p);

使用说明:该函数会影响PLL相位的偏移和抖动的过滤能力,其主要实现查表,Xilinx官方提供了64个数据的表格,根据第一个参数来查找相应的数据,取值范围:1-64,第二个参数是PLL的带宽值,取值范围:HIGH, LOW, AND OPTIMIZED,但是实际上只有两个值,因为HIGH,和OPTIMIZED是一样的,返回值采用u16接收,其实有效数据位只有10bit。

- u32 s6_pll_count_calc(u8 divide, s32 phase, u32 duty_cycle);

使用说明:该函数用来计算分频或者倍频、相位和占空比的参数。第一个参数取值范围:1-128,第二个参数取值(-360° ~ +360)*1000:第三个参数取值:(0-1)*100_000,返回值用u32接收,其有效数据位只有14bit+9bit有效。

四.参数计算说明

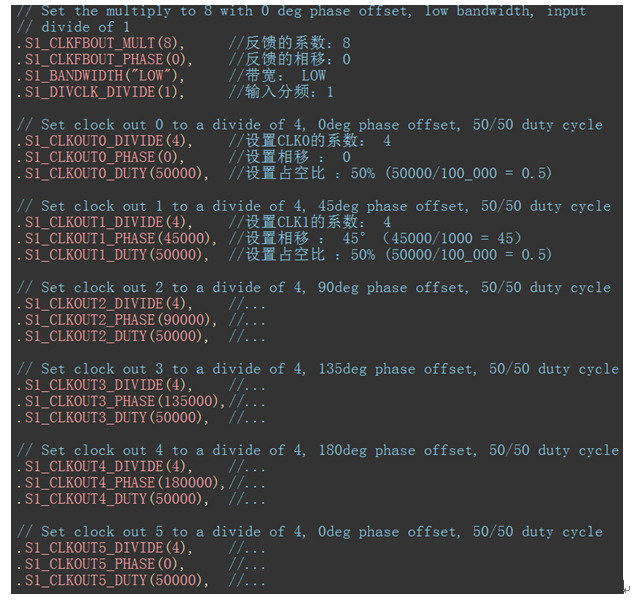

以下是官方顶层文件中的例化实例,我加了一下注释:

输出转换关系:

输出频率 :(反馈系数 / 设置输出的系数)* 输入时钟 (注:假设输入分频为1)

输出相移 :数值 / 1000

输出占空比:数值 / 100_000

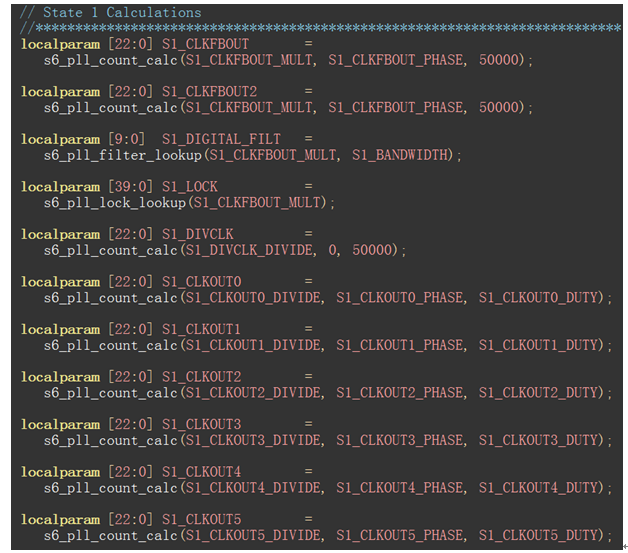

官方参数计算说明,当上图的参数传入后,对应的参数是怎么计算的,如下图:

前5个都是计算反馈的相关参数的,是调用用官方提供的.h文件进行计算,传入的参数参照名字。

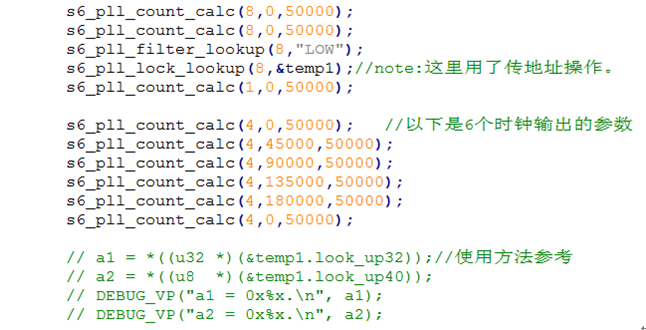

参考xx.h文件,设计了参数计算_exc_pll_cal.c文件,该计算方法是参照上图的使用规则,举例:

前5行是反馈系数的计算,后面的6行是输出时钟的参数计算,实际运用中,应该接收函数的返回值,这里并没有接收,是不正确的使用方法,之所以这么用,是因为我在函数中加了打印注释信息,可以根据打印信息去调试,实际运用要接收函数的返回值。

一.附录

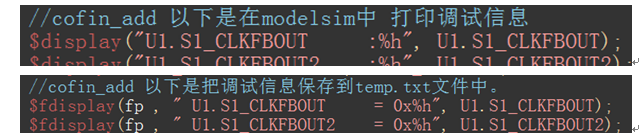

实际工程中,在测试文件中加入了如下调试信息,如下所示:

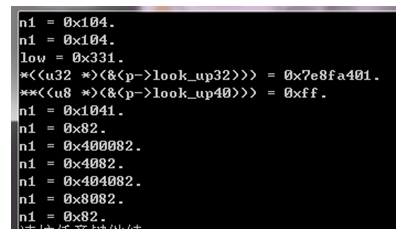

运行modelsim后,写入到temp中的数据:

xx.c文件打印的调试参数:

可以看到和上面的一样,可以用官方的计算参数和xx.c运行之后的结果比对,验证计算后数据的正确性。

备注:关于PLL配置的其他相关资料请查看Xilinx官方的文档。

需要工程文件请向博主索要,欢迎大家讨论,转贴请注明出处,谢谢。欢迎大家一起交流,Q群:912014800。

--------------------cofin_add