之前最常用的一个attribute就是mark_debug了,语法如下:(*mark_debug="ture"*)。

今天又学到几个新的,原文在这里:http://china.xilinx.com/support/answers/54357.html

一、PARALLEL_CASE (Verilog Only)

Parallel case is valid only for Verilog designs. This attribute forces a case statement to be built as a parallel multiplexer. This also prevents the case statement from being transformed into a prioritized if-elsif cascade.

This attribute can only be controlled through the Verilog RTL.

Example:

(* parallel_case *) casex select 4'b1xxx: res = data1; 4'bx1xx: res = data2; 4'bxx1x: res = data3; 4'bxxx1: res = data4; endcase

二、TRANSLATE_OFF/TRANSLATE_ON

TRANSLATE_OFF and TRANSLATE_ON instructs the Synthesis tool to ignore blocks of code. This can be useful to ignore source code that is not relevant for Synthesis, such as simulation code.

These attributes are given within a comment in RTL code. The comment should start with one of the following keywords:

- synthesis

- synopsys

- pragma

TRANSLATE_OFF starts the section of code to be ignored, and TRANSLATE_ON ends the section to be ignored. These attributes cannot be nested.

Be careful with the types of code that are included between the translate statements.

If it is code that affects the behavior of the design, a simulator could use that code, and create a simulation mismatch.

Verilog Example

// synthesis translate_off ...Code to be ignored... // synthesis translate_on

VHDL Example

-- synthesis translate_off ...Code to be ignored... -- synthesis translate_on

三、USE_DSP48

The use_dsp48 attributes allows a user to control how the Synthesis tool deals with arithmetic structures.

By default, mults, mult-add, mult-sub, and mult-accumulate type structures go into DSP48 blocks. Adders, subtractors, and accumulators can also go into these blocks, but by default are implemented with the fabric instead of using DSP48 blocks.

If this attribute is not specified, the default behavior is for Vivado Synthesis to determine the correct behavior.

This attribute overrides the default behavior and forces these structures into DSP48 blocks, and is placed in the RTL on signals, architectures and components, entities and modules, with the following priority:

- Signals

- Architectures and components

- Modules and entities

Accepted values for this attribute are "yes" and "no."

Verilog Example

(* use_dsp48 = "yes" *) module test(clk, in1, in2, out1);

VHDL Example

attribute use_dsp48 : string; attribute use_dsp48 of P_reg : signal is "no";

重点说一下USE_DSP48,这句话可以放在模块的前面,也可以放在reg声明的前面,如下:

一、放到模块前面

(*use_dsp48="yes"*)module COUNTER( input clk, input rst, output [7:0] cnt ); reg [7:0] cnt_tmp = 8'b0; always @(posedge clk,posedge rst) if(rst) cnt_tmp <= 8'b0; else cnt_tmp <= cnt_tmp + 1'b1; assign cnt = cnt_tmp; endmodule

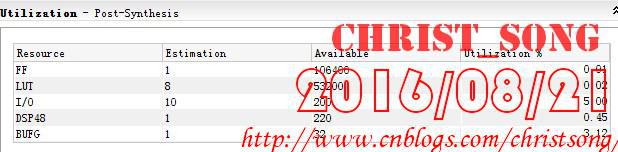

综合后的资源占用如下:

二、放到寄存器声明前面

module COUNTER( input clk, input rst, output [7:0] cnt ); (*use_dsp48="yes"*)reg [7:0] cnt_tmp = 8'b0; always @(posedge clk,posedge rst) if(rst) cnt_tmp <= 8'b0; else cnt_tmp <= cnt_tmp + 1'b1; assign cnt = cnt_tmp; endmodule

综合后的资源占用如下,可以看到跟放到模块前面的资源使用情况是一样的。但这只是针对计数器这么一个简单的模块,如果你的模块中还有其它更复杂的逻辑,那么建议使用第二种方法,只对某些特定的逻辑使用DSP单元。

三、对比不使用DSP

// (*use_dsp48="yes"*) 默认加法不使用DSP module COUNTER( input clk, input rst, output [7:0] cnt ); reg [7:0] cnt_tmp = 8'b0; always @(posedge clk,posedge rst) if(rst) cnt_tmp <= 8'b0; else cnt_tmp <= cnt_tmp + 1'b1; assign cnt = cnt_tmp; endmodule

综合后的资源占用: