GTP+SDI工程播出部分思路整理(3)

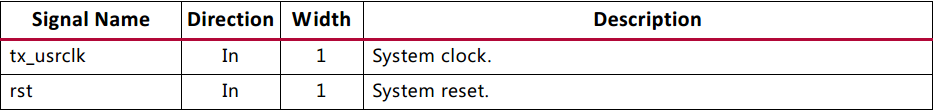

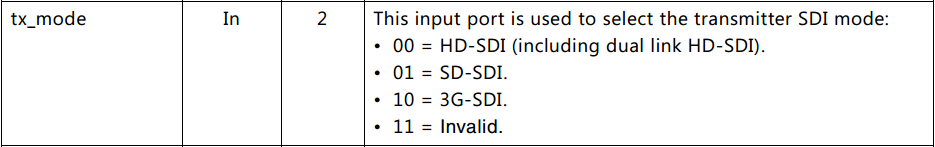

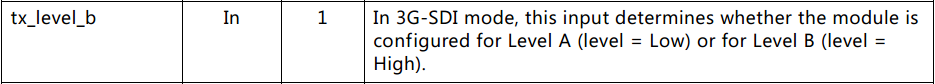

1.本文的目的主要分析video_out_to_sdi模块中输入信号 tx_usrclk, rst, tx_mode, tx_level_b的使用

Tx_usrclk, rst:

Tx_mode:

Tx_level_b:

现在对应分析原SDI工程播出部分是怎样使用这些信号的。

Tx_mode信号脉络:

input wire [1:0] tx_mode, // 00 = HD, 01 = SD, 10 = 3G

Tx_mode信号作为了smpte_sdi SDIRXTX模块的输入信号,也作为x7gtx_sdi_control GTX_CTRL模块的输入信号,看来这个信号很重要。

但是在k7_sdi_rxtx模块中,tx_mode信号是用wire进行定义的,但是没有进行相应的assign语句对tx_mode进行赋值。从监视器观测到的彩条为1280x720@50HZ属于HD信号,是否可以理解为,编译器将tx_mode默认为00,因此,尝试assign tx_mode = 2'b01;修改tx_mode的初值,然后观测监视器上的彩条是否会出现相应的SD-SDI制式的彩条,编译程序,下载代码,监视器上显示720x480@60HZ,属于SD信号。因此可以理解为,tx_mode信号需要自己引出来,用户自己设置。

Tx_level_b信号脉络:

在x7gtx_sdi_wrapper模块中对于tx_level_b信号有如下定义:

input wire tx_level_b_3g, // 0 = level A, 1 = level B

在x7gtx_sdi_wrapper模块中对于tx_level_b的接线如下:

.tx_level_b_3g (1'b0), // In 3G-SDI mode, this demo only transmits level A

在tpg测试工程中,此信号可能用不上。

Tx_usrclk信号脉络:

在x7gtx_sdi_wrapper模块中,与tx_usrclk信号有关的定义如下:

output wire tx_usrclk_out, // clock input

在k7_sdi_rxtx模块中tx_usrclk_out接线如下:

.tx_usrclk_out (tx_usrclk),

在顶层文件kc705_sdi_demo中,tx_usrclk通过ODDR2输出到FPGA端口。