1. general

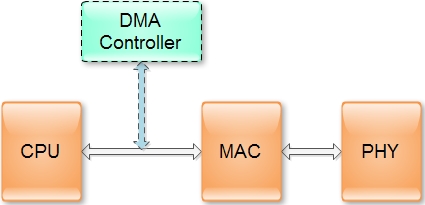

下图是网口结构简图.网口由CPU、MAC和PHY三部分组成.DMA控制器通常属于CPU的一部分,用虚线放在这里是为了表示DMA控制器可能会参与到网口数据传输中.

对于上述的三部分,并不一定都是独立的芯片,根据组合形式,可分为下列几种类型:

- CPU集成MAC与PHY;

- CPU集成MAC,PHY采用独立芯片;

- CPU不集成MAC与PHY,MAC与PHY采用集成芯片;

本例中选用方案二做进一步说明,因为CPU总线接口很常见,通常都会做成可以像访问内存一样去访问,没必要拿出来说,而Mac与PHY之间的MII接口则需要多做些说明.

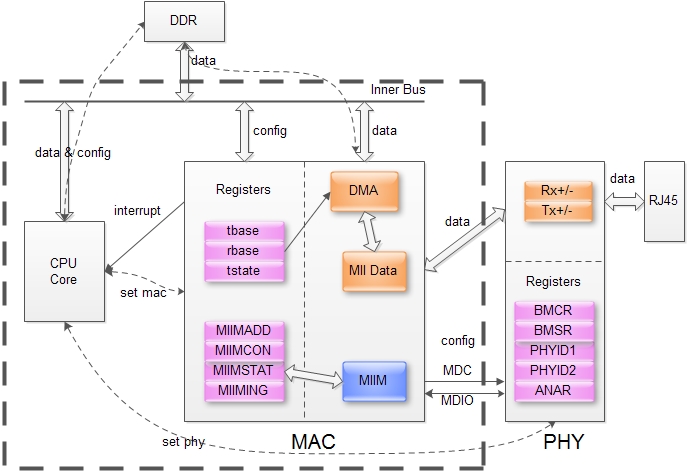

下图是采用方案二的网口结构图.虚框表示CPU,MAC集成在CPU中.PHY芯片通过MII接口与CPU上的Mac连接.

在软件上对网口的操作通常分为下面几步:

- 为数据收发分配内存;

- 初始化MAC寄存器;

- 初始化PHY寄存器(通过MIIM);

- 启动收发;

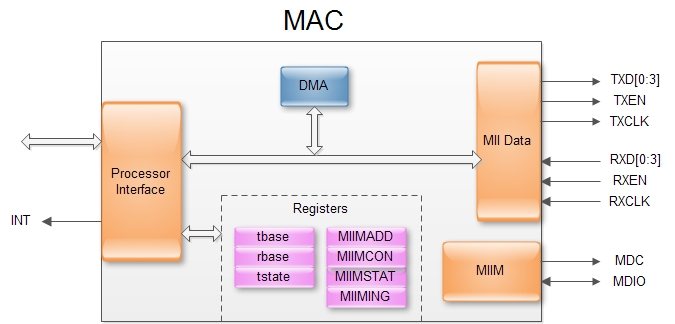

2. MII

MII接口是MAC与PHY连接的标准接口.因为各厂家采用了同样的接口,用户可以根据所需的性能、价格,采用不同型号,甚至不同公司的phy芯片.

需要发送的数据通过MII接口中的收发两组总线实现.而对PHY芯片寄存器的配置信息,则通过MII总的一组串口总线实现,即MIIM(MII Management).

下表列出了MII总线中主要的一些引脚

|

PIN Name |

Direction |

Description |

|

TXD[0:3] |

Mac to Phy |

Transmit Data |

|

TXEN |

Mac to Phy |

Transmit Enable |

|

TXCLK |

Mac to Phy |

Transmit Clock |

|

RXD[0:3] |

Phy to Mac |

Receive Data |

|

RXEN |

Phy to Mac |

Receive Enable |

|

RXCLK |

Phy to Mac |

Receive Clock |

|

MDC |

Mac to Phy |

Management Data Clock |

|

MDIO |

Bidirection |

Management Data I/O |

MIIM只有两个线, 时钟信号MDC与数据线MDIO.读写命令均由Mac发起, PHY不能通过MIIM主动向Mac发送信息.由于MIIM只能有Mac发起, 我们可以操作的也就只有MAC上的寄存器.

3. DMA

收发数据总是间费时费力的事,尤其对于网络设备来说更是如此.CPU做这些事情显然不合适.既然是数据搬移, 最简单的办法当然是让DMA来做.毕竟专业的才是最好的.

这样CPU要做的事情就简单了.只需要告诉DMA起始地址与长度, 剩下的事情就会自动完成.

通常在MAC中会有一组寄存器专门用户记录数据地址, tbase与rbase, cpu按MAC要的格式把数据放好后, 启动MAC的数据发送就可以了.启动过程常会用到寄存器tstate.

4. MAC

CPU上有两组寄存器用与MAC.一组用户数据的收发,对应上面的DMA;一组用户MIIM,用户对PHY进行配置.两组寄存器由于都在CPU上,配置方式与其他CPU上寄存器一样,直接读写即可.数据的转发通过DMA完成.

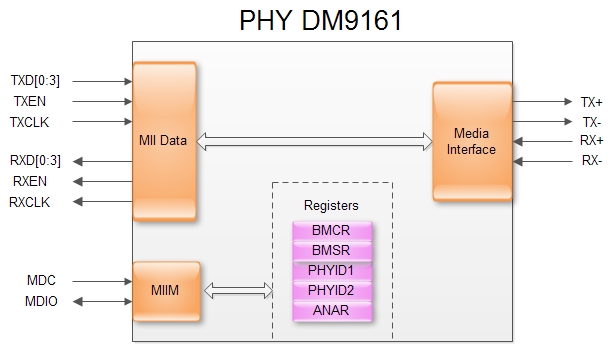

5. PHY

该芯片是一个10M/100M Ethernet网口芯片

PHY芯片有一组寄存器用户保存配置,并更新状态.CPU不能直接访问这组寄存器,只能通过MAC上的MIIM寄存器组实现间接访问.同时PHY芯片负责完成MII总线的数据与Media Interface上数据的转发.该转发根据寄存器配置自动完成,不需要外接干预.

本文转自:http://www.360doc.com/content/13/0717/16/2768962_300623597.shtml

转载:http://www.cnblogs.com/jason-lu/p/3196096.html

嗯,实验室的嵌入式项目需要写设备驱动,我分到了网络驱动的活,写一个适配SylixOS的(这里夸一句,这个真是国内相当不错的嵌入式实时操作系统了)MPC8377的网卡驱动,说实话原来从来没接触过写驱动的事情,更别说复杂的网卡驱动了。所以准备先看看人家写的东西,明确一下概念。讲道理来说现在真的连网卡是啥都不知道。

第一天看了看SylixOS的arm2440的dm9000的网卡驱动,内核的网络协议栈用的是lwip。大概看了看整个驱动的框架……有了个大概的印象,然后又请教了sylixOS的工程师很多问题。

由于在嵌入式系统方面的积累实在太少,所以我对很多嵌入式的概念其实真的不清楚………………比如我以为写网卡驱动就是真的写一个“网卡”的驱动,结果网卡的构成是什么样的都不知道……

本文转载自本文,也结合了其他的网络上博客内容。

以太网(Ethernet)是一种计算机局域网组网技术,基于IEEE制定的IEEE 802.3标准,它规定了包括物理层的连线、电信号和介质访问层协议的内容。以太网是当前应用最普遍的局域网技术。它很大程度上取代了其他局域网标准,如令牌环、FDDI和ARCNET。历经100M以太网在上世纪末的飞速发展后,目前千兆以太网甚至10G以太网正在国际组织和领导企业的推动下不断拓展应用范围。基于以太网的应用一定时期内是研究开发热点。

Ethernet的接口实质是MAC通过MII总线控制PHY的过程。

下图是网口结构简图.网口由CPU、MAC和PHY三部分组成.DMA控制器通常属于CPU的一部分,用虚线放在这里是为了表示DMA控制器可能会参与到网口数据传输中.

对于上述的三部分,并不一定都是独立的芯片,根据组合形式,可分为下列几种类型:

1.CPU集成MAC与PHY;

2.CPU集成MAC,PHY采用独立芯片;

3.CPU不集成MAC与PHY,MAC与PHY采用集成芯片;

MPC8377就正好属于第二种,手上这块板子是eTSEC集成+8e1111 PHY芯片。

下图是采用方案二的网口结构图.虚框表示CPU,MAC集成在CPU中.PHY芯片通过MII接口与CPU上的Mac连接.

在软件上对网口的操作通常分为下面几步:

1.为数据收发分配内存;

2.初始化MAC寄存器;

3.初始化PHY寄存器(通过MIIM);

4.启动收发;

按照OSI七层结构来看,MAC是在数据链路层,而PHY属于物理层。

1.MAC

2.MII

- transmit data - TXD[3:0] ////被发送数据

- transmit strobe - TX_EN////发送使能

- transmit clock - TX_CLK///10/100M信号时钟

- transmit error - TX_ER/TXD4////发送器错误

- receive data - RXD[3:0]///接收数据

- receive strobe - RX_DV///接收数据有效指示

- receive clock - RX_CLK///接收信号时钟

- receive error - RX_ER/RXD4///接收数据出错指示

- collision indication - COL////冲突检测

- carrier sense - CRS////载波检测

- management data clock - MDC////管理配置接口

- management data input/output - MDIO ////管理配置接口数据IO

RMII口是用2根线来传输数据

MII口是用4根线来传输数据

GMII是用8根线来传输数据

MII/RMII只是一种接口,对于10M线速,MII的时钟是2.5M,RMII则是5M;对于100M线速,MII的时钟是25M,RMII则是50M。

前导符+开始位+目的mac地址+源mac地址+类型/长度+数据+padding(optional)+32bitCRC

如果有vlan,则要在类型/长度后面加上2个字节的vlan tag,其中12bit来表示vlan id,另外4bit表示数据的优先级!

3.PHY

100BaseTX采用4B/5B编码。PHY在发送数据时,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC),每4bit就增加1bit的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去。收数据时的流程反之。PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。通信速率通过双方协商,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为Auto Negotiation或NWAY。隔离变压器把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到连接网线的另外一端。RJ-45中1、2是传送数据的,3、6是接收数据的。新的PHY支持AUTO MDI-X功能(也需要隔离变压器支持)。它可以实现RJ-45接口的1、2上的传送信号线和3、6上的接收信号线的功能自动互相交换

网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。很多网卡的这两个部分是做到一起的。他们之间的关系是pci总线接mac总线,mac接phy,phy接网线(当然也不是直接接上的,还有一个变压装置)。

由此可见,MAC 和PHY,一个是数据链路层,一个是物理层;两者通过MII传送数据。

转载:http://blog.csdn.net/hahajinbu/article/details/52174259