Quartus Prime 与 Modelsim 调试 及do文件使用

前言

最新从Xilinx转到Intel,摸索quartus调试做的一些总结

推荐使用quartus加modelsim-intel edition,原因后面讲。但是本博客的目的是总结出quartus prime pro的modelsim使用(这个是最麻烦,自动化最差的),所以选择modelsim的独立版本。本文通过学习standard版本中自动生成的do文件,学习并总结modelsim仿真库的配置(基于quartus)和do文件的详细使用。

调试1,调试2 作为学习仿真操作和do文件编写的一个探索,调试3是pro版真正实操的流程

困难:目前只能对a10及以下芯片仿真,Stratix 10(pro edition才能用)找不到对应的仿真库(器件库已经装了,但是找不到仿真库),目前没法仿真,若有大佬知道怎么解决,望告知,感激不尽。

Quartus本身的一些信息

- 2017开始quartus prime 分standard和pro版本,standard版本支持器件到a10,pro能s10.

- standard版本支持直接调用modelsim(通过run simulation tool),pro版本没有这个选项

- 安装quartus时可以直接不勾选modelsim(starter版也可以,但是不推荐,有些仿真限制(1w行代码))

- 可以勾选modelsim-intel edition(需单独和谐),这样仿真的时候do文件就不用编译和链接(vmap)基础库了,但是ip核相关的文件还是要加

- 接下来的演示以modelsim独立版本为例,目的是探索pro版本的全部操作

调试 1(基于无IP核模式and简单Verilog代码)

安装完quartus(standard edition)后:

安装modelsim10.5se 并和谐:

下面基于是modelsim独立版本

- 在quartus中链接modelsim(每个新工程都需要这样做一次):

- 并且编译一次器件库到modelsim中,在quartus中也定位一下编译好的库(这样就不用每次仿真前都编译一下,但是每个工程都需要设 置一次

- 定位好了以后就可以顺利仿真了,通过run simulation tool。

这里是编译基础库和quartus中链接user compiled library location 的方法

这里是quartus设置仿真软件及testbench的方法

调试2 (基于有ip核)

使用简单的 IOPLL IP核进行测试,基于quartus prime 2017 standard:调试仿真

- 按照调试1中的步骤进行设置,发现会报错误,类似于找不到编译库(PLL相关)

do文件(通过run simulation tool 生成的do)编译ip核的包的时候可能会出现错误(找不到ip核的相关包) - 这种情况就不能如1中一样设置 user compiled library location为quartus预先编译的modelsim库(会缺ip核的包)

- 把这个选项reset成none,也就是不设置

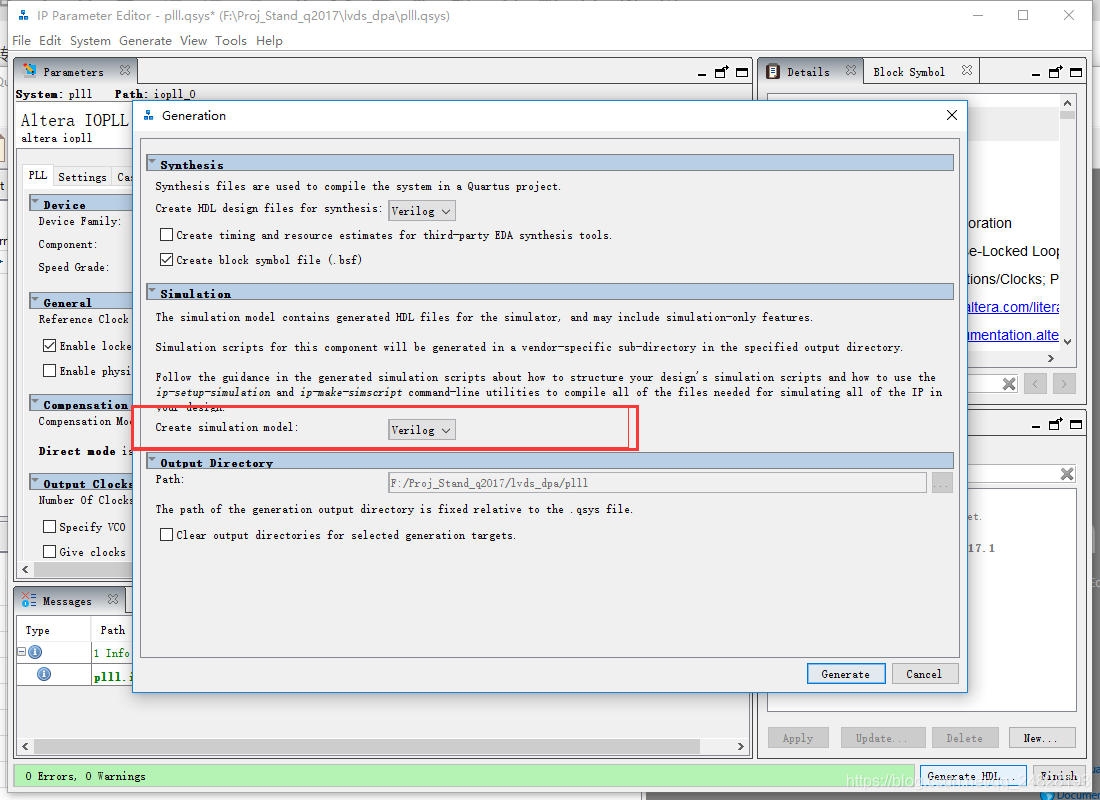

- 同时,IP核的仿真文件需要在设置IP核generate HDL的时候勾选simulation

若不设置user compiled labrary,则每次的do文件都会编译一次基础库(从quartus安装目录下面)和ip核相关文件(这个ip核的仿真文件需要在设置IP核generate HDL的时候勾选simulation ),.do文件实例如下(quartus standard 生成的),可以看出除了基础库,还会编译pll.vo,这个是生成ip核时同时生成的,这个就是最完整的.do文件,作为pro版自己编写时的参考

可以看到,modelsim仿真需要 的所有操作, 链接编译 基本库、ip核vo,v(包含ip核顶层文件v,还有主体文件vo)、 编译用户文件.v、 编译testbench , 并仿真testbench

这部分代码一定不能跳过,要仔细研究

transcript on

if ![file isdirectory test_iputf_libs] {

file mkdir test_iputf_libs

}

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_primitives.v}

vlib verilog_libs/lpm_ver

vmap lpm_ver ./verilog_libs/lpm_ver

vlog -vlog01compat -work lpm_ver {e:/quartus2017standard/quartus/eda/sim_lib/220model.v}

vlib verilog_libs/sgate_ver

vmap sgate_ver ./verilog_libs/sgate_ver

vlog -vlog01compat -work sgate_ver {e:/quartus2017standard/quartus/eda/sim_lib/sgate.v}

vlib verilog_libs/altera_mf_ver

vmap altera_mf_ver ./verilog_libs/altera_mf_ver

vlog -vlog01compat -work altera_mf_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_mf.v}

vlib verilog_libs/altera_lnsim_ver

vmap altera_lnsim_ver ./verilog_libs/altera_lnsim_ver

vlog -sv -work altera_lnsim_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_lnsim.sv}

vlib verilog_libs/twentynm_ver

vmap twentynm_ver ./verilog_libs/twentynm_ver

vlog -vlog01compat -work twentynm_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_atoms.v}

vlog -vlog01compat -work twentynm_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_atoms_ncrypt.v}

vlib verilog_libs/twentynm_hssi_ver

vmap twentynm_hssi_ver ./verilog_libs/twentynm_hssi_ver

vlog -vlog01compat -work twentynm_hssi_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_hssi_atoms_ncrypt.v}

vlog -vlog01compat -work twentynm_hssi_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_hssi_atoms.v}

vlib verilog_libs/twentynm_hip_ver

vmap twentynm_hip_ver ./verilog_libs/twentynm_hip_ver

vlog -vlog01compat -work twentynm_hip_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_hip_atoms_ncrypt.v}

vlog -vlog01compat -work twentynm_hip_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_hip_atoms.v}

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work

###### Libraries for IPUTF cores

vlib test_iputf_libs/PLL_altera_iopll_171

vmap PLL_altera_iopll_171 ./test_iputf_libs/PLL_altera_iopll_171

###### End libraries for IPUTF cores

###### MIF file copy and HDL compilation commands for IPUTF cores

vlog "E:/qua_standard_proj/PLL/altera_iopll_171/sim/PLL_altera_iopll_171_qwujbna.vo" -work PLL_altera_iopll_171

vlog "E:/qua_standard_proj/PLL/sim/PLL.v"

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj {E:/qua_standard_proj/test.v}

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj/simulation/modelsim {E:/qua_standard_proj/simulation/modelsim/test.vt}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver